SOC芯片类市场的现状如何?

集成电路的发展已有40 年的历史,它一直遵循摩尔所指示的规律推进,现已进入深亚微米阶段。由于信息市场的需求和微电子自身的发展,引发了以微细加工(集成电路特征尺寸不断缩小)为主要特征的多种工艺集成技术和面向应用的系统级芯片的发展。随着半导体产业进入超深亚微米乃至纳米加工时代,在单一集成电路芯片上就可以实现一个复杂的电子系统,诸如手机芯片、数字电视芯片、DVD 芯片等。在未来几年内,上亿个晶体管、几千万个逻辑门都可望在单一芯片上实现。

SoC ( System - on - Chip)设计技术始于20世纪90年代中期,随着半导体工艺技术的发展, IC设计者能够将愈来愈复杂的功能集成到单硅片上, SoC正是在集成电路( IC)向集成系统( IS)转变的大方向下产生的。1994 年Motorola发布的Flex Core系统(用来制作基于68000和PowerPC的定制微处理器)和1995年LSILogic公司为Sony公司设计的SoC,可能是基于IP ( Intellectual Property)核完成SoC设计的最早报导。由于SoC可以充分利用已有的设计积累,显著地提高了ASIC的设计能力,因此发展非常迅速,引起了工业界和学术界的关注。

SOC是集成电路发展的必然趋势,1. 技术发展的必然2. IC 产业未来的发展。

SoC的发展趋势及存在问题

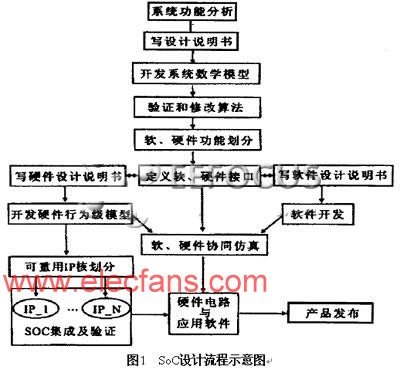

当前芯片设计业正面临着一系列的挑战,系统芯片SoC已经成为IC设计业界的焦点, SoC性能越来越强,规模越来越大。SoC芯片的规模一般远大于普通的ASIC,同时由于深亚微米工艺带来的设计困难等,使得SoC设计的复杂度大大提高。在SoC设计中,仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80% ,采用先进的设计与仿真验证方法成为SoC设计成功的关键。SoC技术的发展趋势是基于SoC开发平台,基于平台的设计是一种可以达到最大程度系统重用的面向集成的设计方法,分享IP核开发与系统集成成果,不断重整价值链,在关注面积、延迟、功耗的基础上,向成品率、可靠性、EMI 噪声、成本、易用性等转移,使系统级集成能力快速发展。

当前无论在国外还是国内,在SoC设计领域已展开激烈的竞争。SoC按指令集来划分,主要分x86系列(如SiS550) 、ARM 系列(如OMAP) 、M IPS系列(如Au1500 ) 和类指令系列(如M 3Core)等几类,每一类都各有千秋。国内研制开发者主要基于后两者,如中科院计算所中科SoC (基于龙芯核,兼容M IPSⅢ指令集) 、北大众志(定义少许特殊指令) 、方舟2号(自定义指令集) 、国芯C3 Core (继承M3 Core)等。开发拥有自主知识产权的处理器核、核心IP和总线架构,同时又保证兼容性(集成第三方IP) ,将使我国SoC发展具有更强的竞争力,从而带动国内IC产业往深度、广度方向发展。

SoC 技术现状及其挑战

当前在微电子及其应用领域正在发生一场前所未有的变革,这场变革是由片上系统(SoC)技术研究应用和发展引起的,从技术层面看,SoC技术是超大规模集成电路发展的必然趋势和主流,它以超深亚微米VDSM(Deep Submicron)工艺和知识产权IP核复用技术为支撑。

SoC 的由来及其发展

SoC 是20 世纪90 年代出现的概念。随着时间的不断推移和SoC 技术的不断完善,SoC的定义也在不断的发展和完善。Dataquest定义SOC为"an integrated circuit that contains acompute engine, memory and logicon a single chip", 即SoC为包含处理器、存储器和片上逻辑的集成电路。这大致反映了1995 年左右SoC 设计的基本情况。随着RF电路模块和数模混合信号模块集成在单一芯片中,SoC 的定义在不断的完善,现在的SoC 中包含一个或多个处理器、存储器模拟电路模块数模混合信号模块以及片上可编程逻辑。因此,SoC 定义的发展和完善过程,也大致反映SoC 技术在近15 年的发展趋势。

国内外SoC 技术的研究及应用现状

从应用开发的角度来看,SoC 的主要含义是在单芯片上集成微电子应用产品所需的所有功能系统。SoC技术研究内容包括:开发工具、IP及其复用技术、可编程系统芯片、信息产品核心芯片开发和应用、SoC设计技术与方法、SoC制造技术和工艺等。从使用角度来看,SoC有三种类型:专用集成电路ASIC(Application Specific IC),可编程SoC(System on Programmable Chip)和OEM(Original equipment Manufacturer)型SoC。

国际上SoC 应用设计逐渐从ASIC方向向可编程SoC方向发展。ASIC设计的典型实例主要包括:1994年Motolola的FlexCore系统是基于定制的 68000和PowerPC微处理器;1995年LSI Logic为Sony公司开发的SoC,它包括一个1MIPS的微处理器,存储器和Sony Logic,这已经被广泛应用于Sony Playstation视频游戏中;1996年IBM公司制造了它的第一款SoC ASIC,该系统包括PowerPC 401微处理器、SRAM存储器、高速的模拟存储器接口和私有的客户逻辑。

随着SoC应用的不断普及,市场需要更加广泛的SoC设计。SoC提供商不仅必须拓展系统内部设计能力,而且要直接开发和交付SoC设计套件和方法给客户。因此,SoC设计逐渐向可编程SoC方向发展。

中国在高新技术研究发展863 计划中,把SoC作为微电子重大专项列入了2000~2001年度信息技术领域的重大专项预启动项目,并在IP核的开发、软硬件协同设计、IP复用、 VDSM设计、新工艺新器件等方面布置了预研性课题,其中IP核的设计和制造是SoC技术中最为关键的部分。在中国最适应SoC技术应用开发的SoC类型是可编程SoC技术。

可编程SoC 是在一块现场可编程芯片上提供产品所需的系统级集成。多家IC提供商已经在可编程SoC的实现方面迈出了可喜的步伐。这些新的器件所提供的系统功能包括处理器、存储器和可编程逻辑,从而解决了与ASIC相关的NRE(非经常性工程)费用高或制造周期太长的问题。可编程SoC提供了ASIC的高集成度(低功率、小尺寸、低成本)及FPGA的低风险、灵活性和上市快的特性。这也是SoC技术在微电子行业受欢迎的最根本的原因。

目前,已有几家IC 提供商提供这种类型的可编程SoC。其中比较著名的三个公司是:Atmel、Xilinx和Altera。Atmel公司1999年开发出首个基于 RISC的现场可编程SoC集成电路FPSLIC(Field Programmable System Level IC)——AT40KFPGA。Xilinx公司的SoC芯片型号为Spartan、SpartanII、Virtex、VirtexII、XC4000 和XC9500,Altera公司的SoC芯片型号为APEXEP20KE、Stratix、StratixII和Cyclone系列。

SoC设计技术面临的挑战

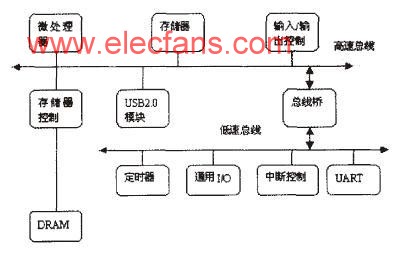

SoC 设计虽然在过去的十几年中已经取得了显著的发展,但是它所面临的挑战也是不容忽视的。作为基于IP核的设计,SoC设计主要向两个方向发展,一是以可重用 IP核为基础的系统级设计,这主要关心的是IP核间的互连性,同时也是SoC设计面临的挑战之一。二是以设计可重用IP核为目的的IP核设计,这主要关心的是IP核的可重用性,同时也是SoC设计面临的又一个挑战。对于第一个挑战,现在通常采用片上总线结构来解决IP核之间的互连性,即核与核之间并非直接相连而是通过片上总线进行互连。典型的互连结构见图1。使用片上总线结构虽然可以解决IP核间的互连问题,但这同时又出现了另外一个问题。由于不同厂商使用不同的总线结构,例如ARM的AMBA总线,MIPS的EC总线,IBM的CoreConnect总线,因此不同厂商IP核之间的互连几乎是不可能的。建立一种通用的片上总线结构是VSIA(Virtual Socket Interface Association)一直努力的目标。

最近,提出一种基于片上网络的互连结构,即IP核之间通过网络结构来实现数据的传输。典型的互连结构见图2。

这种结构虽然可解决通用总线的问题,但建立一个高效的路由算法是非常必要的。

对于第二个挑战,要设计一个可重用的IP核应该具有以下的特征:

● 可读性。这是针对软核和固核来说的,即使用者对IP核的功能和算法有比较详细的了解后,才能正确使用和充分发挥IP核的优点。这就要求IP核的提供商采用一种恰当的方法描述设计,使用户可以方便正确的使用IP核。同时还要采取措施,保护其知识产权不受侵犯。

● 设计的延展性和工艺适应性。IP核是经过精心设计、验证并且优化的,一经定型就要求其具有一定的应用范围,即针对不同的设计应用具有一定的适应性。

● 可测性。IP核必须是经过测试验证的,当用于具体的设计中时,并非一点改变都没有。因此,IP核的功能和性能还应该被使用方测试,不仅能对其进行单独的测试并且能在系统的应用环境中进行测试。

● 端口定义标准化。即IP核的端口要有一个统一的定义。

● 版权保护。

● 交付的数据资料完整,方便芯片的集成过程。

除了以上的挑战之外,伴随着VLSI技术时钟频率超过2.2GHz以及晶体管的特征尺寸缩小到小于0.13μm,对传统的VLSI设计者来说,SoC设计还将面临着下面的一些挑战:

● 由于连接延时的不确定性,在时钟频率为10GHz 集成了上亿晶体管的VLSI(Very Large Scale Integration)芯片上,时钟同步是一个关键问题,必须通过解决时钟抖动和减少摆率的技术来减少时序的混乱,一个全局异步局部同步的时钟策略是绝对必须的。为解决时钟摆率带来的问题,推荐采用网状树组合结构,而且,分布式PLL也变得很有可能。

● 由于高集成度和频率,在将来的生产过程中信号完整性问题将变得更加严重。

● 在将来的生产过程中,过程变量成为影响时序确定性的潜在因素,因为要控制已经减小的特征尺寸是非常困难的。

● 功耗问题仍然是限制SoC设计的因素。

电子发烧友App

电子发烧友App

评论