PCIe标准自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于满足高速显卡、高速存储设备对于高速数据传输的要求。出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIe 3.0,即PCIe 3代的规范,数据速率达到8Gbps。

2023-02-13 15:01:02 3217

3217

泰克公司日前宣布,在4月10日--11日于北京中国国家会议中心举办的2013英特尔信息技术峰会(IDF)上展示业界最完整、最灵活的高速串行信号测试解决方案,为高速数据设计人员解决USB 3.0、PCIe Gen3/4、SATA等高速串行信号测试带来的挑战,并大幅缩短测试和调试时间。

2013-04-10 11:17:54 1152

1152 业界领先的串行高速连接、信号调节和时频解决方案供应商百利通半导体公司(Pericom,纳斯达克股票市场代码:PSEM)日前宣布:面向移动和相关应用中最新CPU芯片组的先进连接需求,推出全新转换器和电源管理产品。

2013-04-11 16:09:32 1140

1140 业界领先的高速连接、信号调节和时频解决方案供应商百利通半导体公司(Pericom Semiconductor Corporation,纳斯达克股票市场代码:PSEM)今日宣布:推出一个全新的带有温度

2013-05-08 10:24:20 1585

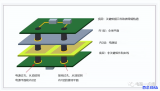

1585 时钟信号是由PCIE主机给到PCIE从机的,所以信号流向是指向左下角的。而此时的信号回流路径包含包地路径和地平面路径。

2020-11-19 15:26:00 3513

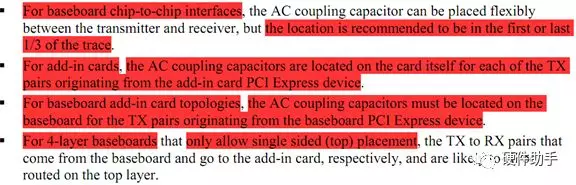

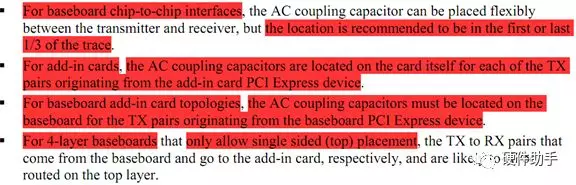

3513 本篇主要介绍PCIe总线的AC耦合电容、总线的去加重等高速信号调整技术。 AC耦合电容可以参考之前的文章《逻辑电平之差分互连AC耦合电容(7)》,本文主要针对PCIe接口介绍AC耦合电容的实际使用

2020-12-22 16:54:15 10606

10606

信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 889

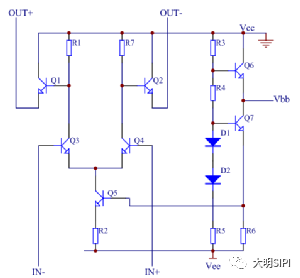

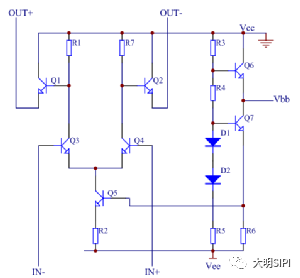

889 差分信号在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,比如PCIe、Ethernet、USB、HDMI等。

2023-06-14 14:22:39 7901

7901

网络搜索“什么是高速信号”或“低速信号与高速信号的区别”,出现一堆解释,例如:

2023-12-01 17:44:41 750

750

电子发烧友网报道(文/周凯扬)随着每代PCIe单通道速度的翻倍提高,电路板上的PCIe信号覆盖范围其实是在减小的,所以现在的服务器都开始用上了PCIe信号增强器。在PCIe 3.0时代,主要用于放大

2023-01-18 01:18:00 5673

5673 电子发烧友网报道(文/周凯扬)随着每代PCIe单通道速度的翻倍提高,电路板上的PCIe信号覆盖范围其实是在减小的,所以现在的服务器都开始用上了PCIe信号增强器。在PCIe 3.0时代,主要用于放大模拟信号的redriver芯片往往就能解决问题,实现更长的线缆长度。

2023-01-29 08:00:00 6169

6169 。PCIe高速采集存储系统由数据采集模块、高速数据存储模块、GPU实时处理模块、便携式工控机等部分组成。可以实现信号的实时采集存储,并且通过调用Window API的方式实现了比一般方式更快的数据存储速度。二

2016-03-29 10:53:40

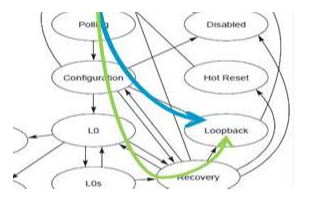

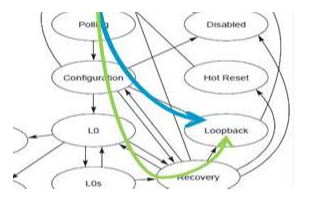

一、接收机测试及环回工作模式(Loopback ) 随着信号速率的不断提升,只对高速信号的发送端物理层测试已经不能够完全反应系统的特性,因此接收机测试也已成为了高速信号的必测项目,尤其是对于

2018-09-26 17:33:30

描述 这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2022-09-21 07:43:27

”,简写PCIe。2、AC耦合电容:高速差分信号电气规范要求PCIe发送端串联一个电容,进行耦合。3、链路类型与差分信号数量:X1:1对时钟差分信号,1对收发差分信号,单面pin数18pi...

2021-11-11 08:05:11

Pericom是一家Fabless芯片设计公司,致力于高速串行互联芯片设计,产品涵盖PCIe、USB3.0 、SAS、SATA、XAUI、HDMI。公司成立于1990年,1997年在纳斯达克上市

2011-02-22 17:55:54

高速信号的电源完整性分析在电路设计中,设计好一个高质量的高速PCB板,应该从信号完整性(SI——Signal Integrity)和电源完整性 (PI——Power Integrity )两个方面来

2012-08-02 22:18:58

形式:芯片级系统SOC、板级系统SOB、封装系统SOP。电子产品的互连有四个层次:芯片内互连、芯片封装、PCB 及系统级互连。它们正在严重地影响着信号、数据和电源的质量。 &

2010-04-21 17:11:35

Agilent Acqiris高速模拟信号平均器可提高oaTOFMS的质量准确度和动态范围

2019-10-29 07:39:14

查过mini pcie的信号引脚定义,有52个信号(大多引脚无用),X1 LANE 的情况,查看飞思卡尔或INTEL处理器的设计资料,关于这个应用除了主要 的差分收、发和差分时钟信号之外还需要额外

2017-11-29 11:50:51

伺服驱动器编码器输出信号接到ni pcie6351板卡上,怎么用,有那几个步骤。没经验,搞不好。大神前来指点一二。

2018-05-26 16:55:45

UD PCIe-404全国产化信号处理模块为标准PCIe全高的结构,对外支持PCIe3.0×8通信,也可以采用千兆以太网(RJ45连接器)、万兆以太网(或RapidIO、Aurora,QSFP+

2023-05-21 18:27:41

标准精心设计, DDR3芯片可以稳定跑到400MHz(FPGA采用-3等级),FPGA与USB3.0芯片以及FPGA跟外部IO之间的PCB连线采用等长设计,有效保证高速信号的可靠传输。通过两个80Pin

2018-10-12 11:38:37

是接收端使用。那么在此想要请教下各位大神,所谓的均衡器技术就是指补偿所接收到的信号,如果在这里我的EQ增益过大会不会影响信号输出的质量,或者是说在特定情况下增益不够,使用级联,又因为EQ主要是补偿接收

2017-04-11 16:52:03

通过cyu***3014传输信号源发出的图像到pc,图像为LVDS传输,用的max9248,信号源为max9247.只有在pcie转u***3.0的扩展卡上能正常工作,streamer跑通,速度

2019-04-19 18:14:57

在设计中,通常总是优先处理光口、PCIE等高速信号、或者是音频等模拟信号。规划使用最优的层,最优的通道,阻抗、延时、串扰等细节也被优化到极致。然而剩下的低速信号往往不被重视。但是有些低速信号表示自己也是要面子的,你不重视我,我就给你颜色看。

2019-07-31 08:02:19

年,USB 2.0增加了高速(HS)模式,数据传输速率达到480 Mbps,并向下兼容低速和全速模式。2008年11月公布的USB 3.0规范支持USB 2.0的所有模式(HS、FS、LS)和全新

2018-12-12 09:51:26

。误区二:有了仿真软件平台就可以做好高速 PCB 设计? EDA 设计软件平台集成了高速信号仿真功能,这对于高速 PCB 设计的规则制定与执行,信号质量仿真与评估都有很大的帮助。 但是,在 PCB 实际

2022-04-28 16:21:41

哪里可以做信号完整性测试,信号质量测试,USB2.0测试,3.0测试,眼图测试等等

2019-11-08 13:28:01

一、PCB设计时高速信号和低速信号区分在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则

2021-11-11 07:59:58

如何去测量数字传输信号的质量?如何保证数字视频信号的质量?

2021-06-01 06:16:39

解决高速PCB设计信号问题的全新方法

2021-04-25 07:56:35

并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

2019-09-26 07:56:41

一块带有PCIE接口的FPGA,一块PCIE转USB3.0板卡,想通过FPGA控制PCIE转USB3.0板卡,实现USB3.0读入数据,经过FPGA高速处理,不需要经过电脑CPU。请问各位专家:1.

2014-12-25 22:54:58

添加测试点会不会影响高速信号的质量?

2009-09-06 08:40:20

问:添加测试点会不会影响高速信号的质量?答:至于会不会影响信号质量就要看加测试点的方式和信号到底多快而定。基本上外加的测试点(不用线上既有的穿孔(via or DIP pin)当测试点)可能加在

2019-08-30 00:45:16

客户端量产状况,成功设计USB 3.0模块主要有三个要点。保持高速信号的完整性信号的质量关系到数据的传输是否完整或U盘的可靠性。根据信号完整性制定出电路板的设计规范及组件的摆放位置,差动传输线阻抗控制

2019-05-15 10:56:56

二:有了仿真软件平台就可以做好高速 PCB 设计?EDA 设计软件平台集成了高速信号仿真功能,这对于高速 PCB 设计的规则制定与执行,信号质量仿真与评估都有很大的帮助。但是,在 PCB 实际

2020-11-30 09:51:58

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-03-02 13:52:47

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-03-09 10:12:15

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-03-16 11:00:00

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-03-30 11:12:53

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-04-07 10:40:35

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-04-14 11:09:20

`产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-04-25 11:21:12

产品编号:1501001高性能6U VPX高速信号处理平台( B-VPX6-6678 )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心

2016-03-23 11:03:18

高速信号互连设计,精品文章,课程不断的发布,请大家关注

2022-05-30 11:44:28

PCIe-8034 是一块4口USB 3.0主控卡,专为工业自动化和机器视觉相关应用设计。USB 3.0或称作高速USB,是一项新兴的总线技术,10倍于USB2.0的传输速度,尤其适用于高速数据存储

2022-04-02 15:46:45

高速电路信号完整性分析与设计—信号完整性仿真:仿真信号仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上

2009-10-06 11:19:50 0

0 焊盘对高速信号的影响

焊盘对高速信号有的影响,它的影响类似器件的封装对器件的影响上。详细的分析

2009-03-20 13:48:28 1507

1507 多高的频率才算高速信号?

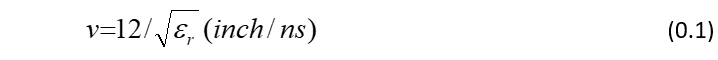

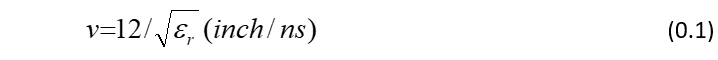

当信号的上升/下降沿时间< 3~6倍信号传输时间时,即认为是高速信

2009-04-15 00:41:34 6451

6451 高速信号走线规则教程

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的关注。高速PCB设计的成功,对EMI

2009-04-15 08:49:27 2798

2798

力科在DesignCon 2010上首家发布PCIe 3.0综合测试解决方案

第一个支持PCIe 3.0的高性能通讯发生器和练习器 Summit Z3-16 Exerciser同步2台WaveMaster 8 Zi 在4通道上同时提供30GHz带

2010-02-08 16:13:37 612

612 什么是链路质量和信号强度 术语名称:链路质量和信号强度

术语解释:信号强度是无线适配器接收到的信号的强度,

2010-02-24 10:30:34 3380

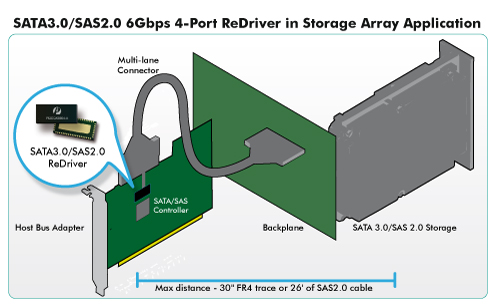

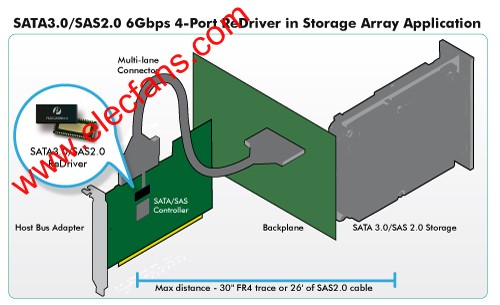

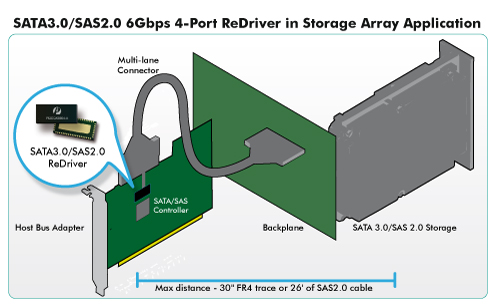

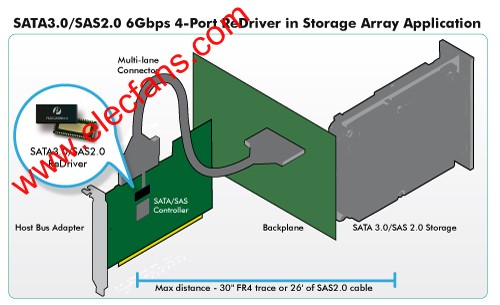

3380 Pericom发布业界第一条极低功耗SATA3/SAS2信号处理产品线

业界最小的单端口和四端口ReDriver产品线,以高成长的服务器、储存和笔记型计算机为目标市场

美国加州旧

2010-11-16 10:35:41 1085

1085

Pericom发布业界第一条极低功耗SATA3/SAS2信号处理产品线业界最小的单端口和四端口ReDriver产品线,以高成长的服务器、储存和笔记型计算机为目标市场

2010-11-16 10:36:55 861

861 Pericom Semiconductor Corporation日前宣布:推出一条包括三款全新的SATA3.0和SAS2.0 6Gbps ReDriver的信号处理产品系列,其中包括业界最小单端口和四端口ReDriver产品。此外,这三款低耗

2010-11-18 09:07:40 1324

1324

Pericom Semiconductor Corporation日前宣布:推出面向PCI Express (PCIe) 3.0的 ReDriver信号调节(signal conditioner)、信号交换(signal swit

2010-11-22 08:50:03 1120

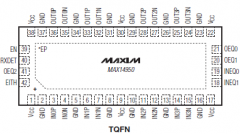

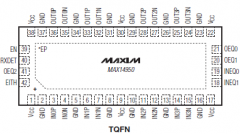

1120 maxim推出MAX14950超小尺寸均衡器/接收器,有效改善Gen 3.0应用中的PCIe信号完整性。

2011-01-15 08:56:06 968

968

百利通半导体公司(Pericom Semiconductor,纳斯达克股票市场代码:PSEM)日前宣布:其最新一代的USB 3.0、DP(Display Port)1.2和PCle 3.0产品系列将使最新CPU芯片组实现采用更高速串行协议的串行连接

2011-09-14 14:20:27 886

886 百利通半导体公司(Pericom )宣布其最新一代的USB3.0、DP(Display Port)1.2和PCle3.0产品系列将使最新CPU芯片组实现采用更高速串行协议的串行连接。

2011-09-17 12:03:46 2283

2283 百利通半导体公司(Pericom,纳斯达克股票市场代码:PSEM)今日宣布:公司产量持续攀升,并扩展了能够支持最新一代英特尔平台的USB3.0、DisplayPortTM(DP)1.2及PCI Express® (PCIe®) 3.0产品系列。

2012-04-11 15:46:29 1050

1050

因为PCIE 3.0信号的速率可以达到8Gb/s,而且链路通道走线也可能会很长,这可能会导致高速信号衰减过大,在接收端无法得到张开的眼图。因此在PCIE 3.0的Tx和Rx端均使用了均衡设置,以补

2012-12-10 10:51:01 41

41 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)今天宣布推出全新用于PCIe 3.0的SpeedBridge® Adapter。它为设计师们提供了一个重要的工具,来验证和确认他们的PCI Express (PCIe) 设计。

2013-07-30 18:35:06 2659

2659 ,正式推出业界首个 16 通道的 PCI Express® 3.0 信号调理重定时器。IDT 全新的 EyeBoost™ 重定时器针对计算、存储和通信应用中的长距离或嘈杂连接来恢复信号质量,从而

2013-09-26 17:06:02 1230

1230 领先的串行高速转换、连接、信号完整性和时频解决方案供应商百利通(Pericom)半导体公司日前宣布:Pericom将为包括笔记本电脑、智能手机和平板电脑等下一代移动设备,面向云计算的先进存储和服务

2015-09-01 10:01:53 880

880 安立公司发布了高速串行总线接收器测试解决方案,该解决方案使用其信号质量分析仪MP1800A系列以及Granite River Labs(GRL)开发的GRL-PCIE4-BASE-RXA 校准/接收器测试软件。

2015-12-23 17:45:15 2245

2245 PCIE 3.0中使用动态均衡方法能够针对不同的情形自动配置并优化发送端和接收端的均衡设置,补偿信号的传输通道对高速信号带来的影响(如损耗),以在接收端获得最好的信号质量。 但是动态均衡优化过程需要花费时间,有时候可能会导致系统工作或运行超时等错误。

2018-01-31 09:09:32 10138

10138

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。

2018-12-22 14:45:41 22377

22377 在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。

2019-12-10 17:25:23 1655

1655 在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响信号质量的5大问题。

2019-10-10 17:21:31 5023

5023 本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。 误区一:GHz速率以上的信号才算高速信号? 提到高速信号,就需要先明确什么是高速,MHz速率级别的信号算高速、还是

2019-11-05 11:27:17 10310

10310

来源:罗姆半导体社区 提到“高速信号”,就需要先明确什么是“高速”,MHz速率级别的信号算高速、还是GHz速率级别的信号算高速? 传统的SI理论对于“高速信号”有经典的定义。SI:Signal

2022-12-12 16:56:35 6009

6009 在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。

2020-11-20 10:55:07 3418

3418 在介绍信号的完整性分析方法在设计高速信号电路的作用前,首先必须明确两个概念,一是何为高速信号,二是何为信号的完整性分析。一提到高速信号,大家一定会想到频率高的信号即为高速信号,其实不然,对于数字信号

2020-12-22 08:00:00 5

5 在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响信号质量的5大问题。 根据目前工作的结论,信号质量

2020-12-22 16:34:40 1472

1472

在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响信号质量的5大问题。根据目前工作的结论,信号质量常见的问题主要表现在五个方面:过冲,回冲,毛刺,边沿,电平

2020-12-24 18:20:46 840

840 高速信号链选择指南

2021-04-24 12:19:08 14

14 据外媒 techpowerup 消息,美国芯片制造商Microchip发布了全球首款 PCIe 5.0 交换芯片:Switchtec PFX PCIe 5.0 系列。

2022-01-04 15:13:04 2552

2552 在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?

2022-02-09 10:02:28 4

4 然而,高速电路是什么,什么信号才属于高速信号?这是笔者曾在一次面试中被问到过的一个问题,当时脑袋中迅速闪过图像数据处理、音频处理等设计,但是如何定义所谓的“高速”却一下子想不出来如何定义这个基本概念。

2022-06-24 11:16:50 6006

6006 PCIe 7.0 接口将继续使用 1b/1b flit 模式编码和随 PCIe 6.0 引入的 PAM4 信号技术,这与PCIe 3.0 到PCIe 5.0 规范中使用的 128b/130b 编码

2022-07-28 15:11:54 925

925 本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2022-09-14 09:20:17 3153

3153 PCIE3.0协议分析仪U4301A,它是一块采用了Agilent AXIe架构的插卡,可以插在AXIe的机箱里,通过探头来捕获高速的PCIE 3.0信号,并通过外部PC控制显示协议分析的结果。

2022-10-12 17:33:56 1191

1191 PCIe标准自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于满足高速显卡、高速存储设备对于高速数据传输的要求。出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIe 3.0,即PCIe 3代的规范,数据速率达到8Gbps。

2022-10-20 09:59:21 4792

4792 随着高速串行信号的数据速率的越来越高,如PCIE6.0的数据速率已经达到64GT/s,USB4.0 V2的信号速率已经达到80Gb/s。高速信号的趋肤效应和传输线的介质损耗,使高速信号在传输

2023-06-07 17:27:02 832

832

电子发烧友网站提供《GEN3通道中的Pericom PCIe重新驱动程序/中继器兼容性.pdf》资料免费下载

2023-07-24 09:50:50 0

0 电子发烧友网站提供《使用Pericom交换机连接LVDS信号.pdf》资料免费下载

2023-07-26 09:17:24 0

0 电子发烧友网站提供《使用Pericom视频交换机接口视频信号.pdf》资料免费下载

2023-07-26 15:31:11 0

0 采集模式,系统实现了效率的检测。其中的挑战在于触发信号源来自编码器的CO输出,但每100个周期仅触发一次。 解决方案 硬件: 简仪科技选择了PCIe-69834高速采集卡和PCIe-5211 计数器卡,以满足复杂的触发需求。通过利用PCIe-5211计数

2023-09-04 09:50:55 370

370 今天给大家分享的是:高速信号、14条高速信号布局设计规则。

2023-09-07 09:19:57 454

454

1个PCIe X4连接器电口,接插件为molex接口,在使用中可支持光纤传输。1个PCIe X8 标准接口,支持V2.0,V3.0规范,1个千兆网络。

2024-01-09 11:07:59 216

216

基于“眼图”概念。眼图是一种信号波形的图形表示方法,由连续传输的数字信号构成。当高速信号被传输时,信号会受到各种噪声、失真和干扰的影响。通过绘制眼图可以观察信号的质量和稳定性,进而判断信号是否能被正确解读。 在高速信号眼图测

2024-02-01 16:19:49 142

142

电子发烧友App

电子发烧友App

评论