纳米制程节点将是半导体厂推进摩尔定律(Moore’s Law)的下一重要关卡。半导体进入7纳米节点后,前段与后段制程皆将面临更严峻的挑战,半导体厂已加紧研发新的元件设计构架,以及金属导线等材料,期兼顾尺寸、功耗及运算性能表现。

台积电预告2017年第二季10纳米芯片将会量产,7纳米制程的量产时间点则将落在2018年上半。反观英特尔(Intel),其10纳米制程量产时间确定将延后到2017下半年。但英特尔高层强调,7纳米制程才是决胜关键,因为7纳米的制程技术与材料将会有重大改变。

比较双方未来的制程蓝图时间表,台积电几乎确认将于10纳米制程节点时超越英特尔。但英特尔财务长Stacy Smith在2016年Morgan Stanley技术会议上强调,7奈米制程才是彼此决胜的关键点,并强调7奈米的制程技术与材料与过去相比,将会有重大突破。

过去,在90纳米制程开发时,就有不少声音传出半导体制程发展将碰触到物理极限,难以继续发展下去,如今也已顺利地走到10奈米,更甚至到7或是5纳米制程节点,以过去的我们而言的确是难以想像。

英特尔在技术会议上的这一番谈话,引起我们对未来科技无限想像的空间,到底英特尔将会引进什么样的革新技术?以及未来在制程发展上可能会遭遇到什么样的挑战?本文将会试着从半导体制程的前段(元件部分)、后段(金属导线)以及市场规模等因素来探讨先进制程未来可能面临的挑战,以及对应的解决办法。

闸极设计走向全包覆结构

半导体前段制程的挑战,不外乎是不断微缩闸极线宽,在固定的单位面积之下增加晶体管数目。不过,随着闸极线宽缩小,氧化层厚度跟着缩减,导致绝缘效果降低,使得漏电流成为令业界困扰不已的副作用。半导体制造业者在28奈米制程节点导入的高介电常数金属闸极(High-k Metal Gate,HKMG),即是利用高介电常数材料来增加电容值,以达到降低漏电流的目的。其关系函式如下:

根据这样的理论,增加绝缘层的表面积亦是一种改善漏电流现象的方法。鳍式场效晶体管(Fin Field Effect Transistor,FinFET)即是藉由增加绝缘层的表面积来增加电容值,降低漏电流以达到降低功耗的目的,如图1所示。

图1传统平面式(左)与鳍式场效晶体管(右)图片来源:IDF,Intel Development Forum(2011)

图2为未来晶体管科技发展蓝图与挑战。鳍式场效晶体管为三面控制,在5或是3纳米制程中,为了再增加绝缘层面积,全包复式闸极(Gate All Around,GAA)将亦是发展的选项之一。但结构体越复杂,将会增加蚀刻、化学机械研磨与原子层沉积等制程的难度,缺陷检测(Defect Inspection)亦会面临到挑战,能否符合量产的条件与利益将会是未来发展的目标

图2未来晶体管科技发展蓝图与挑战图片来源:Applied Materials(2013)

III-V族、硅锗材料呼声高然物理挑战艰钜

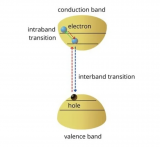

改变信道材料亦是增加IC运算性能与降低功耗的选项之一,晶体管的工作原理为在闸极施予一固定电压,使信道形成,电流即可通过。在数位电路中,藉由电流通过与否,便可代表逻辑的1或0。

过去信道的材料主要为硅,然而硅的电子迁移率(Electron Mobility)已不符需求,为了进一步提升运算速度,寻找新的信道材料已刻不容缓。一般认为,从10奈米以后,III-V族或是硅锗(SiGe)等高电子(电洞)迁移率的材料将开始陆续登上先进制程的舞台。

图2清楚指出10奈米与7奈米将会使用SiGe作为信道材料。锗的电子迁移率为硅的2∼4倍,电洞迁移率(Hole Mobility)则为6倍,这是锗受到青睐的主要原因,IBM(现已并入Global Foundries)在硅锗制程上的着墨与研究甚多。

III-V族的电子迁移率则更胜锗一筹,约为硅的10∼30倍,但美中不足的是III-V族的电洞迁移率相当的低。从图2可看出,n型信道将会选择III-V族作为使用材料,并结合锗作为p型信道,以提高运算速度。

但要将SiGe或是III-V族应用在现行的CMOS制程仍有相当多的挑战,例如非硅信道材料要如何在不同的热膨胀系数、晶格常数与晶型等情况下,完美地在大面积硅基板上均匀植入,即是一个不小的挑战。此外,III-V族与锗材料的能隙(Bandgap)较窄,于较高电场时容易有穿隧效应出现,在越小型元件的闸极中,更容易有漏电流的产生,亦是另一个待解的课题。

后段制程面临微影、材料双重挑战

0.13微米之前是使用铝作为导线的材料,但IBM在此技术节点时,导入了划时代的铜制程技术,金属导线的电阻率因此大大地下降(表1),信号传输的速度与功耗将因此有长足的进步。

为何不在一开始就选择铜作为导线的材料?原因是铜离子的扩散系数高,容易鑽入介电或是硅材料中,导致IC的电性飘移以及制程腔体遭到污染,难以控制。IBM研发出双镶崁法(Dual Damascene),先蚀刻出金属导线所需之沟槽与洞(Trench & Via),并沉积一层薄的阻挡层(Barrier)与衬垫层(Liner),之后再将铜回填,防止铜离子扩散。与过去的直接对铝金属进行蚀刻是完全相反的流程。双镶崁法如图3所示。

双镶崁法制程示意图

随着线宽的微缩,对于黄光微影与蚀刻的挑战当然不在话下,曝光显影的线宽一致性(Uniformity),光阻材料(Photo Resist,PR)的选择,都将会影响到后续蚀刻的结果。蚀刻后导线的线边缘粗糙度(Line Edge Roughness,LER),与导线蚀刻的临界尺寸(Critical Dimension,CD)与其整片晶圆一致性等最基本的要求,都是不小的挑战。

后段制程另外一个主要的挑战则是前文所提到铜离子扩散。目前阻挡层的主要材料是氮化钽(TaN),并在阻挡层之上再沉积衬垫层,作为铜与阻挡层之间的黏着层(Adhesion Layer),一般来说是使用钽(Ta)。

然而,钽沉积的覆盖均匀性不佳,容易造成导线沟槽的堵塞,20奈米节点以前因导线的深宽比(Aspect Ratio,AR)较低而尚可接受,但随着制程的演进,导线线宽缩小导致深宽比越来越高,钽沉积的不均匀所造成的缩口将会被严重突显出来,后端导致铜电镀出现困难,容易产生孔洞(Void)现象,在可靠度测试(Reliability Test)时容易失败。另外,钽的不均匀性容易造成沟槽填充材料大部份是钽而不是铜,由于钽金属导线的阻值将会大幅上升,抵销原先铜导线所带来的好处,其示意如图4所示。

图4 金属导线制程发展蓝图

前文提到衬垫层必需具有低电阻率、良好的覆盖均匀性、是铜的良好黏着层等重要特性,钽在20奈米节点以下已无法符合制程的需求,找出新的材料已经刻不容缓。

钴(Cobalt,Co)与钌(Ruthenium,Ru)是目前最被看好的候选材料。钴是相当不错的衬垫层,具有比钽更低的电阻率,对铜而言是亦是不错的黏着层,且在电镀铜时具有连续性,不容易造成孔洞现象出现。但钴衬垫层也有其不理想之处,主要是因为铜的腐蚀电位高于钴,因此在铜、钴的接触面上,容易造成钴的腐蚀,此现象称为电流腐蚀(Galvanic Corrosion),亦称为伽凡尼腐蚀。

解决电流腐蚀的问题必须从化学机械研磨(Chemical Mechanical Polish,CMP)的与后清洗(Post CMP Clean)着手,使用特殊的化学原料改变铜与钴之间的腐蚀电位,以降低或消除腐蚀现象。目前预估钴衬垫层将可延伸到10奈米制程节点。

接着在7奈米,阻挡层与衬垫层的候选材料将有可能是钌,铜可以直接在钌上电镀,并有效阻挡铜离子对介电层的扩散,如图5所示。

不过,钌跟钴在与铜接触时,一样都会有电流腐蚀问题,只是钌的情况与钴恰巧相反,钌的腐蚀电位高于铜,因此铜金属将会被腐蚀。另外,钌的硬度相当高,且化学性质稳定,不容易与其它化学成份反应,只有使用类似像过碘酸钾(KIO4)这种强氧化剂(过去是使用双氧水作为氧化剂)才可使其氧化,以提高研磨率(大约100∼150A/min)。钌的物理与化学特性,为化学机械研磨制程带来不小的挑战,目前业界还在寻找适当的解决办法。

需求规模恐不足先进制程面临经济因素考验

台积电是全球晶圆代工的龙头,它的动向对于半导体产业发展都具有重大的影响力,每一季财务发表会的声明皆为半导体产业发展的风向球,故分析其营收趋势,可约略窥探与预测未来全球IC产业的发展,图6为台积电各制程节点的每季营收趋势图。

图6台积电各制程节点营收趋势图图片来源:TSMC

由图6可看出,目前主要营收贡献来自28纳米。过去40纳米营收用了13季超越65纳米,28纳米因搭上了行动装置的热潮,只用了6季便超越40纳米。先进制程如20/16奈米制程从推出至今已达7季,虽维持高档,但仍未超越28纳米。从营收的另一个角度观察,价格乘上销售数量等于营收,20/16纳米制程的代工价格必定高于28纳米制程,但营收却未高过于28纳米,可依此推论终端客户对20/16纳米制程的需求与投片量相较于28纳米制程应该是低上不少。且在2016第一季时,20/16纳米制程的营收较上季下滑,28纳米制程却较上季上升,再加上台积电在法说会上提到28纳米制程的产能利用率未来几个季度依旧维持高档,这些迹象显示出终端客户对先进制程需求的态度保守。

过去智慧型手机与平板电脑带动半导体先进制程的发展与高成长,但现在行动通信装置的热潮已明显消退,IC产业链相关厂商亦希望找出下一个杀手级应用,继续带动半导体产业发展。

目前业界一致认为,物联网(Internet of Things,IoT)为最佳候选人之一。物联网主要构架是将会使用大量微控制器(Micro Controller Unit,MCU)与微机电感测器(MEMS Sensor),以及微型Wi-Fi芯片作为数十亿计的「物」的控制与连接元件,这些「物」的信号将会传送到背后数以千万计,具有高运算能力的服务器进行大数据(Big Data)分析,以提供使用者及时且有用的信息。

由此可知,与「物」相关的芯片数量应该会相当惊人,但其所需的半导体制程技术应是成熟型甚至是28奈米制程即可应付;而最需要先进制程技术的服务器中央处理器芯片,相较于「物」的数量应会低上不少,对相关IC制造厂商的贡献营收是否仍可继续支撑制程开发与设备的投资,仍是未知数。市场给予IC制造厂商的压力与挑战,并不亚于前文所提到的制程挑战。

技术挑战时时存在产业生态转变才是真考验

随着制程技术的演进,遇到的挑战与困难只会多不会少,并且制程节点已进入到10奈米以下,快要接触到物理极限,所以除了线宽微缩外,改变元件结构或是使用新的材料等选项,已是一条不可不走的路。

像前段制程的元件部份,除了线宽微缩的挑战之外,其他如功耗的将低或是运算能力的增进,亦是等待解决的课题之一。FinFET将过去的平面式结构转为立体式结构,增加对闸极的控制能力,未来更有可能转为全包复式的闸极以降低漏电流。

另外,改变信道材料,由过去的硅改为SiGe或是III-V族等信道材料,为的都是增加电子或是电洞的迁移率。但晶圆制造业者要如何把异质材料整合至硅基板上,又兼顾可靠度,将是避无可避的挑战。

后段金属导线在材料上的选择亦遇到阻挡层与衬垫层沉积的挑战,间接导致电镀铜的困难度增加,过去是使用氮化钽/钽作为阻挡层与衬垫层,但随着金属导线临介尺寸的缩小,钽/氮化钽已渐渐地不符合制程的要求。钴已在20奈米制程部份取代了钽,作为衬垫层的主要材料,未来钌更会在7奈米制程继续接棒。但因钴、钌与铜电化学与材料的特性,增加了化学机械研磨与后清洗的挑战。

回顾过去的历史,技术上的难关总有办法克服,但接下来半导体产业还要面临经济上的考验。未来的制程节点发展难度将会越来越高,相对的,制程开发与设备的投资金额也将会越来越庞大,最终必定将会反应到晶圆的销售价格上。

上一波行动装置如智慧型手机与平板装置的热卖,带起了28奈米制程营收的高峰,但未来先进制程可能不会有类似的机遇。在行动通信装置的退烧,以及物联网应用的普及带动下,成熟型制程如微机电与28奈米将仍可持续发光发热,但高成本的先进制程未来在市场的接受度上,仍有不少的质疑声浪与挑战,未来的发展有待持续观察。

电子发烧友App

电子发烧友App

评论