他表示,从FinFet向GAA的转变并不会有很大的优势,当中你只是获得了对晶体管静电性能控制的提升。

Fried也指出,GAA最大的提升在于缩小了栅极宽度。这样你就可以得到一个全环绕和一点的静电性能的控制。当然,gate的缩小是必不可少的。

由于每个技术都有优缺点,现在让你选择5nm的架构,相信你心里已经有了答案。

芯片制造商也面临艰难的决定。

“未来将会有两个、三个甚至更多的Finfet节点,未来是否替换材料也是一个问题,是否选择水平纳米线也是一个关键”。Lam的Hemker表示。但晶体管是不变的,但问题的关键是你是否能获得你想要的尺寸而已。

当然,在5nm的时候,你还可以有其他的而选择,例如2.5D堆栈的die,3D的设备和其他等等。

制造gate-all-around

制造GAA fet的方法有很多种,一个简单的方法是,芯片商在pFET和 nFET架构的沟道材料商做个选择。如在pFET 上选硅, Ge或者SiGe,在nFET上选硅、SiGe、Ge或者三五族材料。

Ge和三五族材料的迁移特性比硅高,但这些特殊材料面临缺陷和可靠性的问题。因此一个简单的做法是使用Si或者SiGe。硅锗对比于锗和三五族半导体,其优势是很明显的。IMEC的逻辑设备和集成主管Dan Mocuta表示。

恰当的例子:

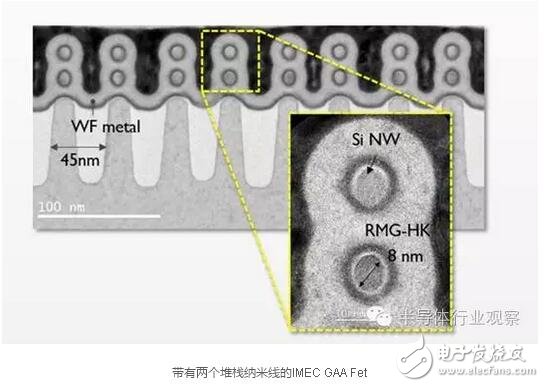

IMEC的GAA制程是通过在CMOS衬底上部形成一个超结晶格子结构,IMEC的超结晶格子结构是一个方形的架构,其包含了一个交互堆栈的Si和SiGe层。理想情况下,一个堆栈会包含三层的SiGe和三层的硅。

制造一个FinFET

一旦超晶格堆栈开发完成,FinFet就已经形成了。

在GAA里,Fin是在侧边的。当然,制程步骤和传统的FinFet是一样的。从一个离子注入机使用传统的掺杂技术,就会在超晶格方形堆栈的顶部形成了源极和漏极。源极会在堆栈的一端形成,漏极则会在另一端完成。

在这个步骤之后,顶部的超晶结构则会以字母H的形式pattern。在经过了几道光刻和刻蚀之后,这个结构就会和字母H很像,而这个H形状的图案是平躺的。

类似H图案的两个高层结构物分居两端,分别充当源极和漏极,中段就是fin的一部分。

在这过程中也会面临一些挑战。例如在pattern的时候,现在有两个光刻的选择,EUV光刻和193nm 沉浸式光刻。EUV和沉浸式光刻在5nm的时候都需要多多层的pattern。

尽管业界希望在7nm和5nm的时候使用EUV,减少pattern的步骤,但是在5nm的时候,芯片制造商是可以选用这两种方案的。

“没有EUV,Mask会爆增,但有了EUV,Mask就可以减少了,从而降低成本”,三星的Low表示。

但目前看来,EUV还是没有量产,因为它在光源、光刻胶和Mask方面都面临挑战。

现在,ASML最新版本的EUV光刻机NXE:3350B已经出货了,这个13.5nm波长工具有一个0.33的数值孔径和16nm间距的分辨率。

ASML同样也将其光刻机的功率从80瓦特提升到125瓦。这就会将晶圆的产量从55、65片每小时提升到85片每小时。除此之外,ASML的新一代产品NEX:3400B也准备好了,这个针对5nm的产品拥有13nm的分辨率。

ASML打算在今年或者明年推出一款两百瓦甚至更高瓦数的设备。但是芯片制造商则希望和以前一样,能够拿到250瓦的设备,这样就可以将其产能提高到最大。那就是125片每小时。

“为了让EUV满足我们的需求,我们还有很多的工作要做”,GlobalFoundries的技术研究高级主管和高级fellow表示。

芯片制造商同样希望EUV抗蚀剂能让其pattern的间距在30nm以下。

“如果抗蚀剂的灵敏度每平方厘米有20焦耳的话,那么这个花费就和沉浸式的三倍pattern差不多”,Levinson表示。

“基于目前的数据,20焦耳是可以达到的,在7nm的时候,30焦耳也是没问题的。这并没有给我们带来类似于沉浸式三倍pattern的花费。但使用EUV还是有其他优势的,在7nm的时候选择EUV是非常正确的”,他补充说。

制造纳米线

下一步可能就是GAA面临的最大挑战,那就是制造纳米线。

在pattern之后,如上文所述,形似H的结构两端分别代表源极和漏极,我们就得在中段制造纳米线。

在这个步骤,IMEC和其他供应商已经开发出一个可替代的金属栅极工艺。一开始,中间段是一个包含了交替堆栈硅和硅锗层的超晶格结构。

使用可替代工艺,目标就是把交替层中的SiGe层移除,这样就会只剩下硅层,且在硅层之间留下了一个空间。基本上来说,每一个硅层就形成了纳米线的基础,每个纳米线在SiGe的“压迫”之下,会提升沟道的移动性。

理想情况下,一个设备会有三层独立的纳米线,每个纳米线都在一个水平方向运行。同时每个纳米线都是悬空且从源极穿到漏极。

基本上,这三层纳米线相互之间是放置在顶部的(顶部、中部和顶部),同时纳米线是有分割空间分开的,互相也不会碰到。

在栅极替换过程中,芯片制造商使用一个刻蚀工具去移除材料。但传统的刻蚀工具在GAA上可能达不到想要的尺寸。

挑战就是在15挨(1挨等于0.1nm)甚至更小的间隙里移除硅锗,且在移除硅锗的过程中,不能干扰到设备的其他部分。

在这个过程中,芯片制造商可能需要用到下一代的刻蚀技术atomic layeretch(ALE),这个可以在原子尺度上有选择且精确地移除目标材料。理论上,ALE可以移除硅层之间的硅锗,而不会破坏剩下的部分。

“这个方法是可以有选择性的去除硅锗,这样你就能生成纳米线”,应用材料的全球产品经理Matt Cogorno表示。

然而,我们还需要面临其他挑战。

在纳米线下面,会有一个寄生沟道,你需要找个方法去阻隔寄生沟道的泄露,IMEC的做法是一个叫做地平面掺杂的方式,我们会在沉积超晶格结构之前掺杂这个区域,这样的话就会阻止泄露且提升亚阈值斜率,IMEC的Mocuta表示。

栅极和内部连接

现在,设备需要一个栅极,使用atomic layerdeposition (ALD),,HKMG材料被放置在源极和漏极的狭小间隙之间。这样的话,栅极就会被每个纳米线包围。

在这里会面临很多放置的挑战,Coventor的Fried表示。

在一个Finfet,你看栅极的沟槽,你可以看到fin,因此你可以把材料放置在任何地方,你只需对fin的侧墙有点担心,但你可以看到你放置的任何地方。

但在GAA,这是一个完全不同的故事。

现在你看向那个沟槽,你只看到那些线,我需要把材料放置在指定的位置,同时我还需要一个高质量的保护涂层,Fried表示。

其他人也认同这个观点。

ASMI的全球产品市场主管MohithVerghese说,无论你是在线周围涂层,还是线的下面涂层,你并没有任何对准线,你只有祈求化学工作能够完美。

要解决方案?

我们会看到热ALD的再次出现,这完全依赖于化学,Verghese表示。热ALD包括了一个带有两个反应物的二进制进程,A和B。A反应物被注入ALD里面,晶圆被加工然后化学物被清洗,然后化学物B经历同样的操作。

最后,在5nm的时候,内部连接会成为最大的挑战。

为了解决RC延迟的问题,芯片制造商需要新的突破。这是一个很大的问题,Lam的Hemker说。你需要从各个方面解决这个问题,这是一个有关材料、设备、集成方案和设备布局多方面综合的解决方案。

接下来呢?

虽然不确定是否会实现,但是芯片制造商在研发过程中会关注3nm和其他更先进的制程。

在3nm的时候,产业或许会探索水平GAA fet和垂直纳米线FET。

“我们现在正在和某些大学就垂直纳米线的相关研究进行合作,如果能够成功,这回事一个很大的进步。现在你从密度上解耦晶体管的性能,你需要将其尺寸变得越来越小,这样每更新一代进程,泄露就会增加。泄露的多少取决于先的长度。同时其堆积密度就是其直径。现在则更加独立了,你仍然需要去蚀刻这些东西并制造,与此同时,你还有很多的工作要做”。Hemker说。

除此之外,complementaryFET同样吸引了业界的关注。

这个设备有点像水平的GAA。每个纳米线就是nFET,然后下一个就是Pfet。等等注入类似。

“你在三维孤立这些设备并对战起来,这可能是一个思考模式的转移,这是电路密度的一个彻底转移。这就真的是一个大挑战了”。Fried表示。

电子发烧友App

电子发烧友App

评论