新思科技公司(Synopsys, Inc., 纳斯达克股票市场代码:SNPS)日前宣布: 该公司针对多家领先的晶圆代工厂优化的28纳米工艺DesignWare IP已赢得第100项设计。

2012-09-20 10:11:40 1139

1139 高质量DesignWare接口和模拟IP经过优化,可在人工智能、云计算和移动芯片中实现高性能和低功耗。

2019-06-29 09:49:28 1162

1162 新思科技接口和基础 IP 组合已获多家全球领先企业采用,可为 ADAS 系统级芯片提供高可靠性保障 摘要: 面向台积公司N5A工艺的新思科技IP产品在汽车温度等级2级下符合 AEC-Q100 认证

2023-10-23 15:54:07 691

691 英飞凌 | CoolSiC™器件为台达双向逆变器提供助力英飞凌科技股份公司的CoolSiC™产品被总部位于台湾的全球领先的电源管理及散热解决方案提供商台达电子选用,使得台达电子向着利用绿色电力实现

2022-08-09 15:17:41

一次泵变流量系统技术的应用研究一次泵变流量系统(Variable-Primary-Flow System,以下简称VPF系统)诞生的历史并不长,空调行业人士针对该系统的认识存在一渐进接受的过程

2021-09-09 07:25:40

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

` 观点:在技术领先的优势下,台积电获得苹果iPhone5芯片追加订单已成事实。然而,在iPhone 5推出后,苹果已朝下一世代A7处理器迈进,台积电凭借技术领先的优势,预估未来1-2年内

2012-09-27 16:48:11

制造技术为今年的10.5寸和12.9英寸iPad Pro制造A10X芯片。事实上,A10X是第一款采用该技术生产的芯片,尽管台积电还有其他客户。 相比之下,iPhone 7和7 Plus中使用的A10

2017-08-17 11:05:18

都用它拍摄。在嘉奖公告上,学院特别指出ALEXA摄像机直观的设计和具吸引力的图像再现,这是第一台被摄影师广泛采用的数码摄像机。数码摄像机(包括ALEXA)需要将一系列不同元素成功地结合起来,以制作出获奖

2018-10-24 08:54:21

的数据包,该ARP请求就是因为要发送这个包而发送的。这种方法在假设上层会重发被覆盖的数据时采用。每隔十秒钟,表就会刷新一次,旧的记录被丢弃,在嵌入式TCP/IP协议栈中,记录的有效时间为1秒。 2.2.2

2019-04-23 07:00:10

重发被覆盖的数据时采用。每隔十秒钟,表就会刷新一次,旧的记录被丢弃,在嵌入式TCP/IP协议栈中,记录的有效时间为1秒。 2.2.2 网络协议IP 在嵌入式TCP/IP中,IP协议执行两项功能:(1

2019-04-28 09:57:18

前言 随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息的处理变得日益重要,如基于PC的软复用器的实现,使得通过PC接收DVB(数字视频广播)码流

2019-05-05 09:29:32

AD7401*是一款二阶Σ-Δ调制器,采用ADI公司iCoupler?技术的片内数字隔离,能将模拟输入信号转换为高速的1比特的数据流。AD7401采用5V电源供电,可输入

2010-03-17 09:36:28

,最高支持7680×4320 8K分辨率,以及各种IO输入输出能力。英伟达还有一片GTX 1080 TI,同样采用台积电16nm FinFET+工艺制造,集成多达120亿个晶体管,硅片面积是471

2018-07-31 09:56:50

;*** CryptoCell技术有助于强化安全SoC设计;采用ARM Cordio? radio IP的完整无线解决方案,支持802.15.4 和Bluetooth? 5;通过ARM mbed? Cloud,云服务能够支持物联网设备的安全管理;ARM Artisan? IoT POP IP针对台积电40ULP工艺实现优化。

2019-10-23 08:21:13

现在创龙开发板提供的UDP例程,是基于创建一个DaemonNew 服务而实现,其第一次只能被动的接受客户端的消息,才支持对端的IP与端口号;void NetOpenHook(){ // 创建一个

2020-05-22 09:55:30

了https保证了数据交互的安全性。全方位助力区块链技术在行业中的实际应用。<p>`

2018-11-16 15:30:07

STM32按键之短按加一次而长按连续加的功能题目要求思路过程解决过程anjian.c注意anjian.htimer.c注意timer.h题目要求在蓝桥杯嵌入式第九届的省赛题出现了这样一个功能要求,每

2022-01-06 07:03:58

我想做放弃一次时间片的实验遇到了奇怪的现象,自己想半天想不出来啊。新人求指教。这么写 (如图1)这样写结果算是成功(任务2先跑的)(结果如图)。可是我把放弃的函数写在这里(如图2)结果是 这样的啊。我觉得到第二次的时候应该是任务2先跑第二次,可是没有。我百思不解啊。

2020-03-15 21:12:00

你好!我将 NodeMCU 连接到电容式土壤湿度传感器以发送湿度水平。我成功地将它连接到 ThingSpeak,并且能够每 30 秒记录一次数据。然后我尝试对 Firebase 做同样的事情。我遇到

2023-02-22 07:43:30

1座支持20纳米12英寸厂南科Fab14第5期已全产能投片,第2座12英寸厂Fab14第6期将在7月正式进入量产,将成为台积电第3季营收挑战2,000亿元新高的重要动能。 台积电原本计划在今年底转进

2014-05-07 15:30:16

芯片PMIC 5即将问世,由于改为BCD制程,台积电凭借先进制程技术优势,可望拿下高通新一代PMIC 5订单约70~80%数量,并牵动高通电源管理芯片代工厂大洗牌。 业界推估高通各种用途电源管理芯片的年

2017-09-22 11:11:12

`1.三星嵌入式方案思科德技术是从事三星嵌入式方案开发的专业团队,专注于以三星ARM处理器为核心的嵌入式平台开发。 思科德技术经历多年的研发和服务客户,开发出的产品方案包括平板电脑、手持设备、广告机

2013-11-19 17:26:07

的宽度,也被称为栅长。栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管。目前,业内最重要的代工企业台积电、三星和GF(格罗方德),在半导体工艺的发展上越来越迅猛,10nm制程才刚刚应用一年半,7n...

2021-07-29 07:19:33

SPI4-P2接口形式可直接采用Altera公司的IP Core实现。Altera的主流FPGA均实现了硬件DPA功能,以Stratix II器件为例,在使能DPA的情况下使用SPI4-P2 IP Core可实现

2012-11-09 18:43:41

越来越先进,台积电的5nm制程成本也水涨船高,开发一款芯片的费用将达到5.4亿美元,台积电5nm全掩模流片费用大概要3亿人民币,而且还不包含IP授权费用。如此高的门槛,大部分公司都会选择观望。目前,也

2020-03-09 10:13:54

本帖最后由 妙脆啵啵 于 2021-12-22 17:12 编辑

在labview中我利用了TCP/IP实现两台电脑进行通信,虽然在同一台电脑可以连续发送消息。但是两台电脑现在程序只能发一次

2021-12-22 16:55:33

纳米制程功耗低性能强国民做安全芯片起家,自带多种加密算法安全性高与台积电签订多份采购订单,供货较为稳定MCU产品已得到多家行业龙头客户认可并导入(华为、大疆、宁德时代)宽产品线、覆盖32位MCU从低端到高端的绝大多数应用场景国民技术MCU表示Pin数与flash容量的字母后缀与ST、GD对应含义

2021-11-01 07:51:48

门的协作。企业要从战略层面去落实开源管理。新思科技强调,软件风险等同于业务风险。因此,开源战略已经成为企业业务战略的一部分。凭借可信的开源管理工具,新思科技已经为全球许多客户软件开发生命周期的开源治理提供

2023-03-02 14:20:49

Kochpatcharin表示:“台积公司与新思科技等开放创新平台(OIP)合作伙伴紧密合作,助力我们的客户在执行定制及模拟模块的工艺制程设计迁移时,提高生产效率并加快设计收敛。现在,通过全新的新思科技AI驱动型模

2023-04-03 16:03:26

43.3亿美元,季增5.5%。结语:台媒表示,台积电涨价现已生效,但台积电的价格合同是一年一次的,因此新价格应该到2022年1月才会生效。台积电作为全球最大的芯片制造商,此翻大幅涨价将标志公司走上一

2021-09-02 09:44:44

。 成功客户辽宁省电力江苏常熟发电有限公司浙能集团燕山石化…… 综述通过在线直播的流媒体传播形式,可以完美实现日常业务培训与文件精神传达。电力行业由于企业特性——没有太多的分支机构在外,基本上均在

2012-08-23 10:13:15

潮流正在又一次上演,甚至以DSP著称的TI公司也自称是家模拟公司。既然这样,为什么具备丰富模拟专长的IDM还要采用别人的模拟IP呢? Franca给出了答案。目前,即使是飞思卡尔、TI和NXP等大型

2019-05-13 07:00:04

这些年,英特尔、三星、台积电在制程上的恩恩怨怨,堪比武侠小说中恩怨情仇。这些大厂的争斗均是围绕14纳米和16纳米,那么问题来了,这个14纳米和16纳米有什么好争的?下面芯易网就来简单做一下介绍。纳米

2016-12-16 18:20:11

这些年,英特尔、三星、台积电在制程上的恩恩怨怨,堪比武侠小说中恩怨情仇。这些大厂的争斗均是围绕14纳米和16纳米,那么问题来了,这个14纳米和16纳米有什么好争的?下面芯易网就来简单做一下介绍。纳米

2016-06-29 14:49:15

技术部攻关小组的潜心研发,成功攻克解决此问题,这一技术攻关的告捷标志着我公司产品技术再创新高,并为实现开封仪表行业的八突破做出重大贡献。突破一:提高产品可靠性;突破二:提高数字化、智能化、集成化水平;突破

2017-12-01 15:50:40

`第一次成功画PCB,高兴呀!失败了N次`

2013-05-31 17:03:43

下面的任务,只能在第一次执行UPP时成功,后面的均不成功,请创龙工程师看看为什么?Void UPP_TASK(Void){ int i,j,k,target_int_count=2; char ch

2019-07-04 11:54:28

第一次申请成功,还没有收到。使用后再上传试用报告。

2016-01-29 13:17:22

、可见性和效率,采用开放式行业标准网络技术的单一系统架构显得至关重要。”EtherNet/IP是自动化的基础:一种同时面向车间和企业网络的应用层协议在2013年11月开展“移动性、以太网和无线网络调查

2018-10-22 16:45:22

第三个特性为基础,我们还在第二部分开始探讨了融合型全厂以太网架构(CPwE),这是罗克韦尔自动化有限公司与思科公司联合开发的一种参考架构,其目的是鼓励通过结合使用标准以太网和IP套件实现IAC系统

2018-10-22 16:51:22

10nm将会流片,而张忠谋更是信心十足,他直言不讳地表示10nm量产后将会抢下更高的份额。台积电联席CEO刘德音此前也曾在一次投资人会议上透露,公司计划首先让自己的10纳米芯片产线在今年底前全面展开

2016-01-25 09:38:11

DesignWare是什么?Designware库中有哪些IP?

2021-06-21 06:49:49

灵思公司在最先进28nm高性能低功耗(HPL)技术部署上的再次成功,同时也是我们为客户提供最好可编程技术承诺的又一次成功!为此, 我们深感骄傲和自豪,并希望与您——赛灵思携手与之共赢的客户朋友共同

2012-03-22 15:17:12

了两次创业经历,如今一直坚持在做人工智能客服。每个人对成功的定义都不一样,魏佳星称自己的第一次创业只能说是半成功。公司刚成立,合伙人就走了,自己带着十几个兄弟坚持一直做,两年后公司被并购,第一次创业

2018-08-09 09:21:46

新思科技与中芯国际合作推出用于中芯65纳米低漏电工艺技术的、获得USB标志认证的DesignWareUSB 2.0 nanoPHY

通过芯片验证的DesignWare PHY IP

2010-05-20 17:39:09 588

588 新思科技完整实施流程助力英飞凌在中国成功实现首款40纳米3G基带处理器芯片设计和一次流片成功

中国北京和西安,2010年8月9日—全

2010-08-11 14:39:39 510

510 Synopsys, Inc.宣布:即日起推出面向多种180纳米工艺技术的DesignWare® AEON®非易失性存储器(NVM)知识产权(IP)。

2011-06-29 09:04:28 983

983 联电(2303-TW)(UMC-US)与全球半导体设计制造软体暨IP领导厂商新思科技(Synopsys)昨日共同宣布,双方已扩展夥伴关系,将于联电28奈米HLP Poly SiON制程平台上开发新思科技的DesignWare IP。 联电表

2011-10-13 09:41:08 677

677 领先的韩国半导体公司TLi采用Arasan的通用闪存(UFS)知识产权(IP)产品实现了芯片设计的出货,该公司之前获得了Arasan的UFS设备控制器IP及支持高达Gear 3速率的MPHY等产品的授权。TLi是最新一家使用Arasan的UFS Total IP解决方案成功实现芯片设计的公司。

2016-01-06 17:46:12 4483

4483 3月8日消息 据国外媒体报道,美国通信设备巨头思科公司宣布,将停止WiMax基站的研发及制造等工作,以集中精力开展IP网络业务。 思科公司新闻发言人布拉迪(Jim Brady)本周五宣布:思科公司

2017-12-12 06:05:33 538

538 Mali-G76处理器)的初期采用者实现了成功的流片。采用Fusion技术的新思科技设计平台、Verification Continuum Platform和DesignWare接口IP互相配合,提供了优化的性能、功耗和面积,并加速了基于Arm的产品上市时间。

2018-07-28 11:17:00 1352

1352 DesignWare IP解决方案,为行动、云端运算及汽车等各式应用提供高效能、低功耗的系统芯片(SoCs),由于达成多项客户硅晶设计成功,DesignWare IP获得广泛的采用,也因此设计人员在整合IP时能更具信心,并大幅降低SoC整合的风险。

2019-05-14 16:25:27 2862

2862 新思科技近日宣布推出DesignWare®视频电子标准协会(VESA®)显示流压缩(DSC)编码器和解码器IP,用于手机、增强/虚拟现实和汽车系统芯片(SoC)的显示接口的视觉无损压缩。新款

2019-05-23 08:36:35 5412

5412 新思科技近日宣布与GLOBALFOUNDRIES (GF)合作,针对GF的12纳米领先性能(12LP) FinFET工艺技术,开发覆盖面广泛的DesignWare® IP组合,包括多协议25G

2019-07-05 09:13:13 3145

3145 DesignWare DDR5/4 PHY IP核提供基于固件的训练,无需更改硬件即可进行现场升级,从而帮助客户降低采用新协议的风险。基于固件的训练也有助于使用复杂的训练模式,在系统层面上支持最高裕度和通道可靠性。

2020-08-28 15:38:04 1986

1986 新思科技(Synopsys, Inc. , 纳斯达克股票代码:SNPS)近日宣布,全球领先的无线通信和语音处理芯片解决方案提供商DSP 集团选用新思科技DesignWare® ARC® EM5D

2020-10-14 15:10:33 862

862 ● DesignWare CXL IP 支持 AMBA CXS 协议,以实现与可扩展 Arm Neoverse 相干网状网络的无缝集成 ● 新思科技 CXL IP 以 32GT/s 的速度运行,数据

2020-10-27 16:40:28 1477

1477 、DDR5、LPDDR5、MIPI、OTP NVM等 ●新思科技与GF的长期合作,成功实现了DesignWare IP核从180nm到12nm的开发,并可应用于广泛领域 新思科技(Synopsys)近日宣布

2020-11-03 16:48:08 2048

2048 技(Synopsys)近日宣布与英特尔开展合作,以成功实现用于PCI Express 5.0系统(PCIe 5.0)的DesignWare控制器和PHY IP与英特尔Xeon可

2020-11-24 16:00:53 1812

1812 新思科技(Synopsys)近日宣布与SiMa.ai开展合作,将其机器学习推理技术大规模引入嵌入式边缘设备。此次合作,SiMa.ai将采用新思科技的DesignWare IP核、Verification Continuum平台和Fusion Design Platform进行MLSoC开发。

2020-11-27 14:41:26 1755

1755 DesignWare HBM2E PHY IP 可提供每秒 460 GB 的聚合带宽,能够满足先进 FinFET 工艺 SoC 对海量计算性能的要求。HBM2E IP 是新思科技全面内存接口 IP

2021-02-14 09:22:00 773

773 今天小新又为大家带来两款接口IP明星产品的技术更新:适用于22纳米工艺的DesignWare MIPI D-PHY IP和新一代DesignWare USB4 IP。希望这两款产品更新可以帮助开发者

2021-01-15 09:39:50 2116

2116 超分辨率技术。为了实时执行该技术,处理器需要具备专用神经网络加速器,如新思科技的 DesignWare ARC EV 处理器 IP,以在不增加功耗和面积预算的情况下,也能满足密集计算的功耗需求。图像超分辨率技术现已应用于视频监控、人脸识别、医疗诊

2021-02-01 17:32:23 2355

2355

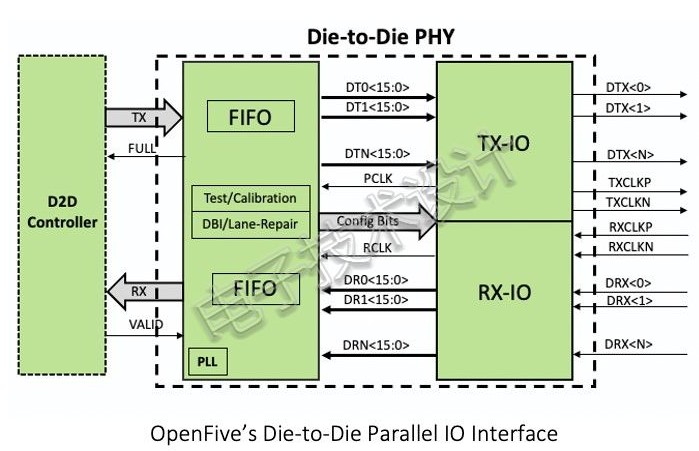

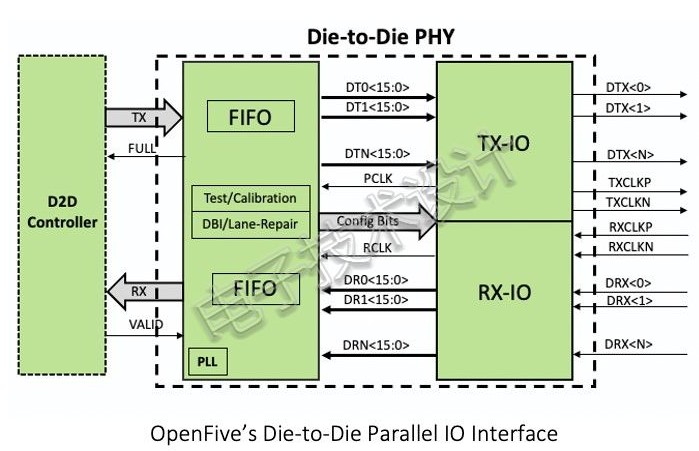

最大的RISC-V架构厂商SiFive近日宣布,其OpenFive部门已成功采用台积电(TSMC)的N5工艺技术流片公司首个SoC,采用2.5D封装HBM3存储单元,带宽7.2Gbps。在半导体行业中,流片意味着芯片设计大功告成,一般会在一年内投入商用。

2021-05-01 09:33:00 2960

2960

新思科技广泛的DesignWare IP产品组合包括逻辑库、嵌入式存储器、IO、PVT传感器、嵌入式测试、模拟IP、接口IP、安全IP、嵌入式处理器以及子系统。

2021-05-14 14:25:02 1350

1350 全面运算为中心的解决方案集成了新思科技的设计、验证和IP产品组合,助力高端消费设备实现更优性能功耗比。

2021-06-02 11:32:07 2740

2740 基于当今的先进制程技术、基础优化方案、遥测技术和分析方法,刚加入新思科技的Moortec所提供的芯片内传感技术始终是实现最高性能和可靠性的关键要素。

2021-06-28 11:46:43 459

459 通过与台积公司在早期的持续合作,我们为采用台积公司先进的N3制程技术的设计提供了高度差异化的解决方案,让客户更有信心成功设计出复杂的SoC。

2021-11-02 09:24:25 411

411 技(Synopsys)近日宣布其数字定制设计平台已获台积公司N3制程技术认证,双方将共同优化下一代芯片的功耗、性能和面积(PPA)。基于多年的密切合作,本次经严格验证的认证是基于台积公司最新版本的设计规则手册(DRM)和制程设计套件(PDK)。此外,新思科技

2021-11-16 11:06:32 1558

1558 新思科技(Synopsys)与芯耀辉(Akrostar)双方已达成数年期战略合作,新思科技授权芯耀辉运用新思科技12-28纳米工艺技术、适配国内芯片制造工艺的DesignWare® USB、DDR、MIPI、HDMI和PCI Express的系列IP核。

2022-03-16 15:31:17 1586

1586 新思科技推出了完整的USB4解决方案DesignWare® USB4 IP,可以确保USB4能够达到甚至超过预期,以帮助客户加快产品上市速度。

2022-05-16 17:31:55 1580

1580 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,众多领先的半导体和系统客户已成功采用面向 TSMC 5nm 制程技术的全系列 Cadence® 设计 IP 产品。

2022-06-24 14:52:46 1585

1585 新思科技数字和定制设计流程获得台积公司的N3E和N4P工艺认证,并已推出面向该工艺的广泛IP核组合。

2022-07-12 11:10:51 877

877 新思科技设计、验证和IP解决方案助力全新Arm Cortex CPU和新一代Arm GPU实现业内领先的性能和能效比。

2022-07-13 11:06:18 1015

1015 来自业界领先公司的多个成功流片案例展示了新思科技解决方案强大的可靠性,并为实现流片成功提供了更快路径 加利福尼亚州山景城2022年11月7日 /美通社/ -- 新思科技(Synopsys, Inc

2022-11-08 13:37:19 1358

1358 工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的基础IP、接口IP组合已经在台积公司N3E工艺上实现了多项成功流片,助力合

2022-11-10 11:15:22 502

502 为满足客户对异构计算密集型应用的复杂要求,新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)近日宣布,推出业界领先的全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N3

2022-11-16 16:25:43 877

877 Cadence 致力于扩大我们的 IP 产品组合,以满足客户不断变化的设计要求。客户现在可以信心满满地在 TSMC N5 工艺节点上利用 Cadence GDDR6 设计 IP 实现更高的带宽。

2022-11-22 10:24:51 738

738 新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N3工艺技术的2D/2.5D/3D多裸晶芯片系统。基于与台积公司

2022-12-01 14:10:19 486

486 新思科技连续12年被评为“台积公司OIP年度合作伙伴” 该合作推动了多裸晶芯片系统的发展和先进节点设计 奖项涵盖数字和定制设计、IP、以及基于云的解决方案 推出毫米波(mmWave)射频(RF

2022-12-14 18:45:02 534

534 的先进设计。另一款 CPU 设计采用 AI 赋能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的数字设计流程,借助台积电 N5 制程工艺,成功让功耗降低 8%,设计面积缩小 9%,同时显著提升了工程效率。

2023-02-06 15:02:48 1048

1048 新思科技一直与台积公司保持合作,利用台积公司先进的FinFET工艺提供高质量的IP。近日,新思科技宣布在台积公司的N3E工艺上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 452

452 (一次性可编程存储器)/NTP(少次可编程存储器)/MTP(多次可编程存储器)/eFlash(嵌入式闪存模块)技术,为客户提供全方位、一站式存储IP定制服务和IP授权服务,满足其广泛的应用需求。产品支持车规级可靠性 AEC-Q100 认证。瞩目的是,我司近期基于130纳米逻辑制

2023-06-15 15:44:54 1285

1285 Labs实现光学DSP SoC设计的一次性流片成功。2021年,Banias Labs采用了新思科技的IP,以充分利用该IP在低延迟、传输长度灵活性、以及在5纳米工艺技术上的成熟度等方面的技术

2023-06-19 18:05:01 180

180

、UCIe、LPDDR、DDR、MIPI等广泛使用的协议中,并在三星工艺中实现高性能和低延迟 新思科技基础IP,包括逻辑库、嵌入式存储器、TCAM和GPIO,可以在各先进节点上提供行业领先的功耗、性能和面

2023-06-30 13:40:14 341

341 的“耳目”。 新思科技一直走在芯片监控解决方案的前沿,而这些解决方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在台积公司N5和N3E工艺上完成了PVT监控IP测试芯片的流片 。这是一个里程碑式的成功。从此,那些准备在这些先进节点

2023-07-11 17:40:01 516

516 存储器、TCAM和GPIO,可以在各先进节点上提供行业领先的功耗、性能和面积(PPA) 新思科技车规级IP集成到三星的工艺中,有助于确保ADAS、动力总成和雷达SoC的长期运行并提高可靠性 三星工艺中集成了广泛的IP组合,并在新思科技经过认证的数字和定制设计流程的加持下,共同加速流片成功

2023-07-26 17:40:03 255

255 战略合作伙伴关系之上; 新思科技与英特尔近日共同宣布,双方已经达成一项最终协议,通过为英特尔代工客户开发针对Intel 3和Intel 18A制程工艺的IP产品组合,进一步扩大在半导体IP和EDA(电子设计自动化)领域的长期战略合作伙伴关系。新思科技针对英特尔先

2023-08-18 15:10:02 378

378

基于台积公司N3E工艺技术的新思科技IP能够为希望降低集成风险并加快首次流片成功的芯片制造商建立竞争优势

2023-08-24 17:37:47 657

657 合作伙伴关系。 英特尔和新思科技(Synopsys)近日宣布已经达成最终协议,深化在半导体IP和EDA(电子设计自动化)领域的长期战略合作伙伴关系,共同为英特尔代工服务的客户开发基于Intel 3和Intel 18A制程节点的IP产品组合。提供基于英特尔先进制程节点的关键

2023-09-12 16:36:24 175

175

内容提要 ● 经过验证的接口 IP,可显著提升 TSMC N3E 制程节点的性能和能效 ● 224G-LR SerDes PHY IP 在 TSMC N3E 制程上实现一次性流片成功

2023-09-26 10:10:01 320

320 。 Synopsys.ai™ EDA解决方案中的模拟设计迁移流程可实现台积公司跨工艺节点的快速设计迁移。 新思科技接口IP和基础IP的广泛产品组合正在开发中,将助力缩短设计周期并降低集成风险。 加利福尼亚州桑尼维尔, 2023 年 10 月 18 日 – 新思科技(Synopsys, I

2023-10-19 11:44:22 104

104 新思科技(Synopsys, Inc.)近日宣布,面向台积公司N5A工艺推出业界领先的广泛车规级接口IP和基础IP产品组合,携手台积公司推动下一代“软件定义汽车”发展,满足汽车系统级芯片(SoC)的长期可靠性和高性能计算需求。

2023-10-24 17:24:56 505

505 和 M-PHY ,以及 USB IP 产品都遵循了 TSMC N5A 工艺领先的车载等级设计规则。 新思科技宣布面向台积公司N5A工艺推出业界领先的广泛车规级接口IP和基

2023-10-31 09:18:44 709

709

电子发烧友App

电子发烧友App

评论