Holtek新推出单通道低功耗比较器IC – HT93111/HT93121。此系列低功耗比较器提供完整的轨对轨输入/输出操作,具有单电源供电、低功耗、低失调电压和低失调漂移等优点,

2024-03-15 18:13:34 524

524 IPP-1102 嵌入式分频器 – 组合器IPP-1102 是一款同相组合器-分配器,可组合 2 个相干输入信号或将 1 个信号分成 2 个信号。该组合器-分配器的工作频率为 20-1000 MHz

2024-03-03 12:36:48

IPP-1103 嵌入式分频器 – 组合器IPP-1103 是一款同相组合器-分配器,可组合 4 个相干输入信号或将 1 个信号分成 4 个信号。该组合器-分配器的工作频率为 20-1000 MHz

2024-03-03 12:36:27

IPP-1106 嵌入式分频器 – 组合器IPP-1106 是一款同相组合器-分配器,可组合 4 个相干输入信号或将 1 个信号分成 4 个信号。该组合器-分配器的工作频率为 80-1000 MHz

2024-03-03 12:36:09

IPP-1107 嵌入式分频器 – 组合器IPP-1107 是一款同相组合器-分配器,可组合 2 个相干输入信号或将 1 个信号分成 2 个信号。该组合器-分配器的工作频率为 400-1000

2024-03-03 12:35:47

IPP-1108 嵌入式分频器 – 组合器IPP-1108 是一款同相组合器-分配器,可组合 4 个相干输入信号或将 1 个信号分成 4 个信号。该组合器-分配器的工作频率为 400-1000

2024-03-03 12:35:20

IPP-1104 嵌入式分频器 – 组合器IPP-1104 是一款同相组合器-分配器,可组合 2 个相干输入信号或将 1 个信号分成 2 个信号。该组合器-分配器的工作频率为 500

2024-03-03 12:34:56

500-2500 MHz。总和端口的额定连续射频总功率高达 200 瓦 CW。IPP-1105 采用 3.00 x 4.00 英寸封装,带有插入式标签。该组合器/分配器的幅

2024-03-03 12:34:30

IPP-1109 嵌入式分频器 – 组合器IPP-1109 是一款同相组合器-分配器,可组合 2 个相干输入信号或将 1 个信号分成 2 个信号。该组合器-分配器的工作频率为 1000-4000

2024-03-03 12:34:03

MHz。 总和端口的额定连续射频总功率高达 500 瓦 CW。IPP-1130 采用 2.00 x 3.00 英寸封装,带有插入式标签。该组合器/分配器的

2024-03-03 12:33:38

UXD20P-预分频器低噪声 DC 至 20GHz 可编程预分频器UXD20P 是一款低噪声 DC 至 20GHz 可编程预分频器,具有 1 分频、2 分频、4 分频或 8 分频比。在除以 1 模式

2024-02-29 15:56:08

UXC20P是一款低噪声预设标器,具有2分频、4分频或8分频比。该器件具有差分输入和输出、可调输出幅度和高输入波形。格式控制输入是兼容式金属氧化物半导体与LVTTL兼容。UXC20P封装在24引脚

2024-02-29 15:53:58

UXN14M9PE是UXN14M9P的评估板,UXN14M9P是一款高度增强的整数分频器,覆盖8至511之间的所有整数分频比。该器件具有单端或增量输入和输出。硬件控制输入是互补式金属氧化物半导体

2024-02-29 15:51:56

具有双 40 GHz 预分频器的 8 GHz 鉴相器 ICMMFEB21PP6 是一款具有双高速预分频器的高频鉴相器 (PFD)。8 GHz PFD 允许在更高的参考

2024-02-29 14:46:47

UXN14M32K预分频器15 GHz、32位有效分频器UXN14M32KSuperDivider是一款DC-15 GHz、高度瞬时的整数分频器,顶部1和4,294,967,295

2024-02-29 13:59:41

UXN14M9P是一款高度灵活的整数分频器,外壳8至511之间的所有整数分频比。该器件具有单端或差分输入和输出功能。UXN14M9P封装在40引脚、6mm x 6mm无引脚塑料SMT中

2024-02-29 13:58:38

摆幅和高输入同等。控制输入是互补式金属氧化物半导体和LVTTL兼容。UXM15P封装在24引脚、4x4毫米无引脚表面贴装封装中。 UXM15P-预分频器

2024-02-29 13:57:30

PFD1K-鉴频鉴相器具有双40 GHz预分频器的8 GHz相位频率检测器ICPFD1K是一款具有全差分输入和输出的高频相频检测器。它具有双7位高速预分频器,允许PFD1K在

2024-02-29 13:56:31

UXD20K-预分频器 低噪声 DC 至 26.5 GHz 可编程预分频器UXD20K 是一款低噪声 DC 至 26.5 GHz 可编程预分频器,具有 1 分频、2 分频、4 分频或 8

2024-02-29 13:21:11

描述 ADF7012是一款低功耗ASK/FSK/GFSK UHF发射机,设计用于短程无线设备(SRD)。输出功率、输出通道、偏移频率和调制类型均可通过4个32位寄存器编程设置。 利用小数N

2024-02-27 10:08:35

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

2024-02-01 11:19:51 452

452 锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 311

311 经常有人问S3模组是怎么配置低功耗模式的?低功耗模式下功耗大概是多少?下面小启就跟大家讲下S3模组低功耗情况。01ESP32S3系列模组三种低功耗模式:•Modem-sleep模式:CPU可运

2024-01-26 08:03:56 529

529

的BRP(波特率预分频器)(CAN标称位时间配置寄存器高电平)

和

C1DBTCFGH内的BRP(波特率预分频器)(CAN数据位时间配置寄存器高电平)

两者的范围均为1 - 256

2024-01-22 06:36:03

全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布推出DA14592低功耗蓝牙(LE)片上系统(SoC),成为瑞萨功耗最低、体积最小的多核(Cortex-M33、Cortex-M0+

2024-01-19 16:37:30 586

586 美光科技近日宣布推出业界首款标准低功耗压缩附加内存模块(LPCAMM2),这款产品提供了从16GB至64GB的容量选项,旨在为PC提供更高性能、更低功耗、更紧凑的设计空间及模块化设计。

2024-01-19 16:20:47 262

262 我知道的是,每个IP都可以编程来选择它的时钟源,预分频是什么意思?分频的目的又是什么呢?

2024-01-17 07:34:27

蓝牙技术联盟于2010年推出了蓝牙4.0规范,其中低功耗蓝牙的出现满足了小型电池供电设备进行低功耗无线连接的需求,因此得到广泛应用。本文章将带你深入了解低功耗蓝牙的应用。低功耗蓝牙简介2010

2023-12-28 08:24:49 350

350

相比于云端AI,边缘AI具备实时性好、带宽资源要求低、隐私性高等特点,特别适合物联网应用。ADI的边缘AI低功耗微处理器领域的最新款产品是MAX78002,具备更高频率的MCU内核、更大存储空间

2023-12-15 12:36:21 519

519 本次与大家分享的是世健和ADI联合举办的《世健·ADI工业趴:放飞思路,解封你的超能力》主题活动的二等奖文章:《采用ADI公司ADF4107芯片研制C波段频率合成器》。作者:RF-刘海石01背景本文

2023-12-15 08:23:46 329

329

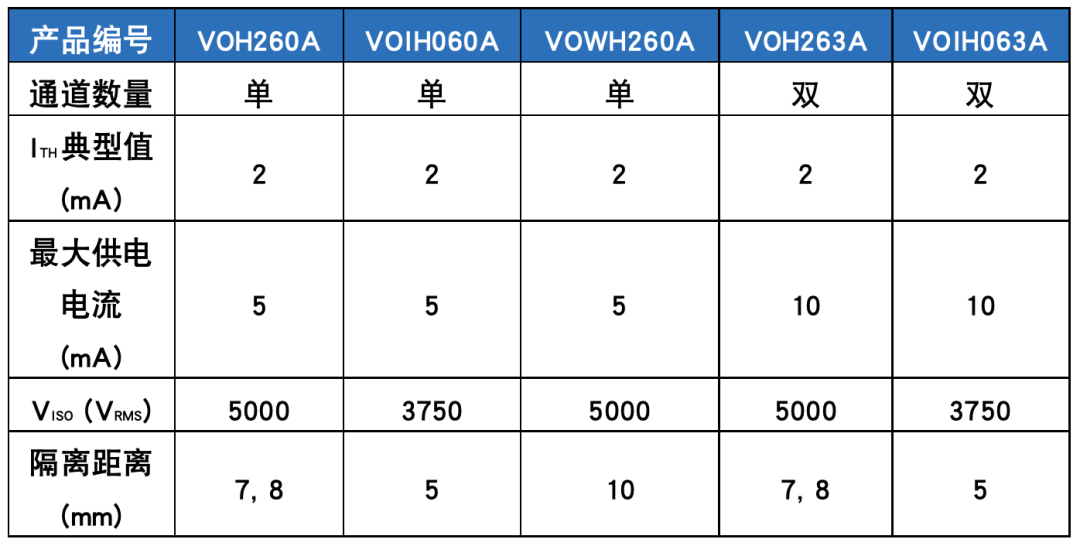

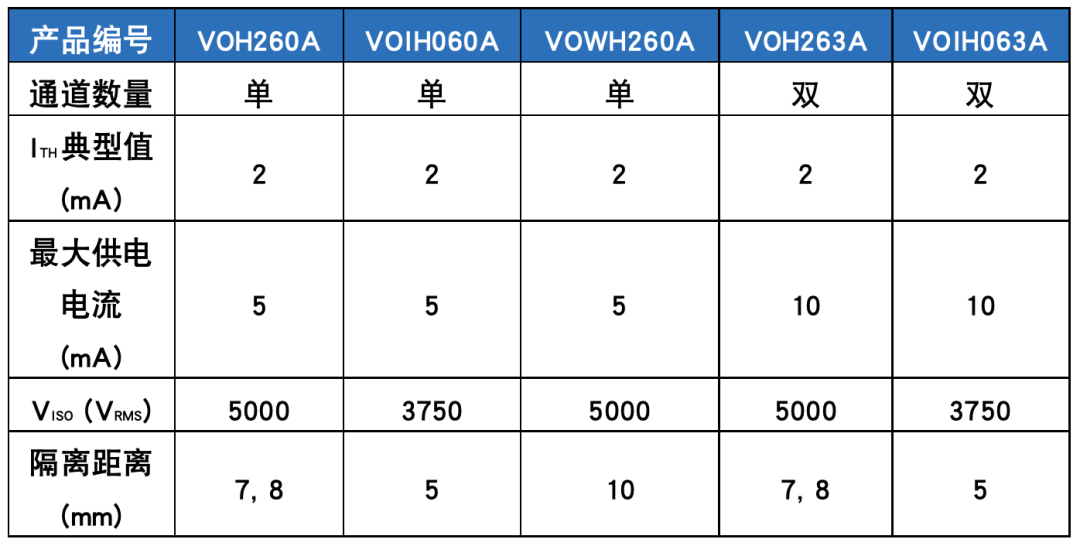

Vishay 推出五款新型 10 MBd 低功耗高速光耦,有助于工业应用节能。

2023-12-08 09:27:10 394

394

用sigmastudio开发AD1940,在分频器类型切换时,必需重新编译download一次才有效。能不能够做到像PEQ切换类型一样简单快捷?

2023-11-29 07:24:04

电子发烧友网站提供《ADI公司开发一款低成本、低功耗嵌入式成像平台BLIP MINI.pdf》资料免费下载

2023-11-28 10:51:29 0

0 电子发烧友网站提供《ADI公司开发BLACKFIN低功耗成像平台(BLIP).pdf》资料免费下载

2023-11-28 10:41:42 1

1 _sport_ConfigClock和adi_sport_ConfigFrameSync中的分频系数是多少?

2. adi_sport_ConfigClock这里的时钟分频系数和pcg clk的分频系数有什么关联,比如1中的时钟是由内部pcg生成的,pcg该如何配置,sport是否需要配置?

2023-11-28 07:27:37

。

测试程序是参照ADF4360-8修改的,用c8051f020单片机控制,芯片内部无2分频,与分频采用8/9,无锁定输出。

测试中R分频器有非常好的输出,200kHz梳状脉冲,这证明程序没有问题

2023-11-27 09:34:56

下面的寄存器设置实现:在外部晶振10MHz的条件下,主端口输出1.4G射频信号。

R5: 0x004005;

R4: 0x00950024;

R3: 0x000084B3;

R2

2023-11-24 08:29:03

电子发烧友网站提供《CareFusion与ADI之间的探讨:优化EEG放大器的性能并降低功耗.pdf》资料免费下载

2023-11-22 10:22:25 0

0 在进行数字电路设计的过程中,分频器是设计中使用频率较高的一种基本设计之一

2023-11-07 17:29:11 745

745

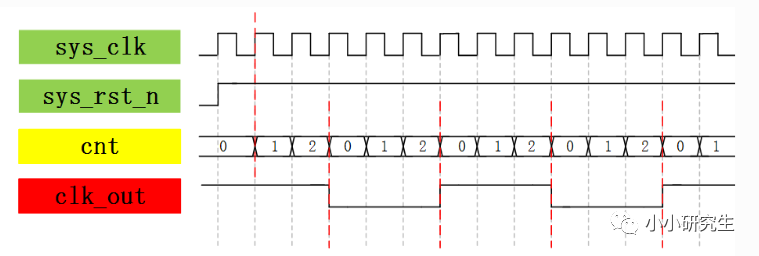

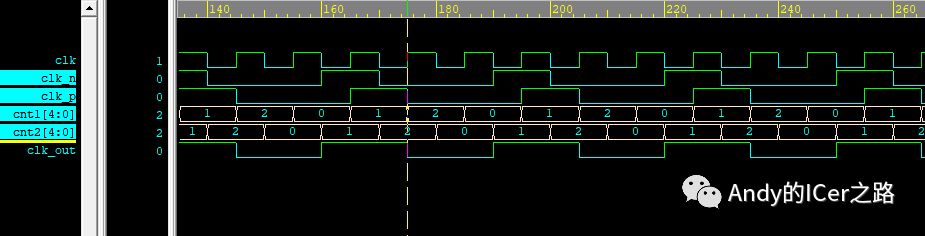

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 471

471

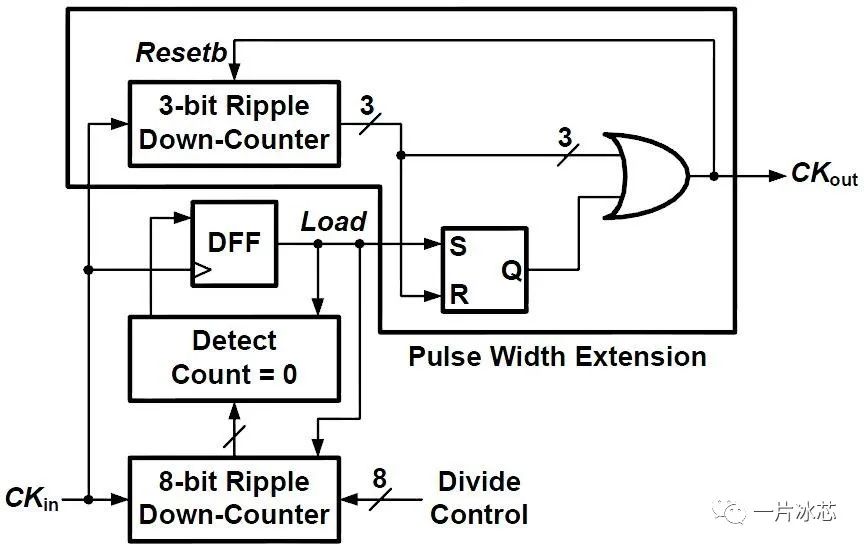

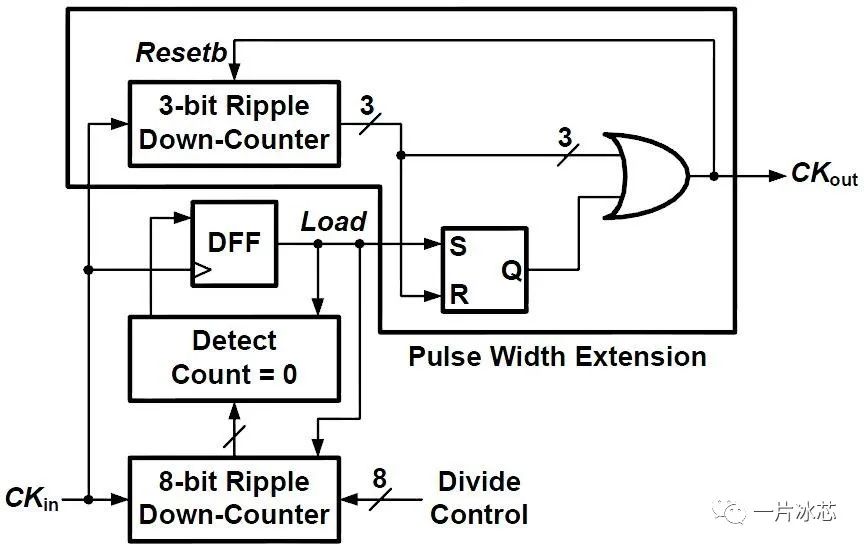

文献给出的分频器结构如图1所示。该分频器最高输入频率(f~in~)为16.3GHz,也就是一个周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

2023-10-31 12:54:56 766

766

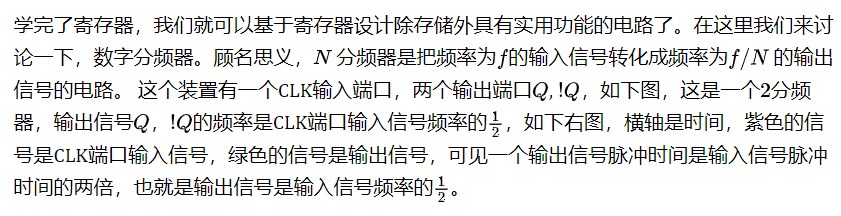

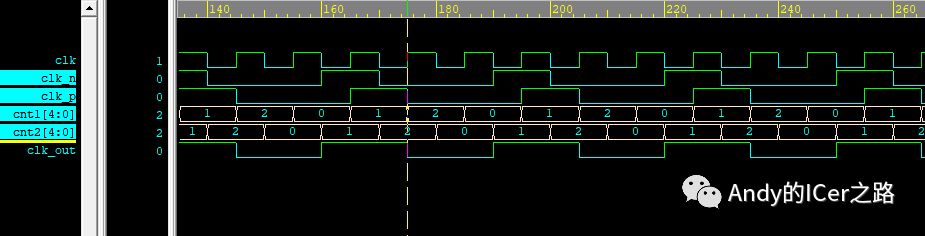

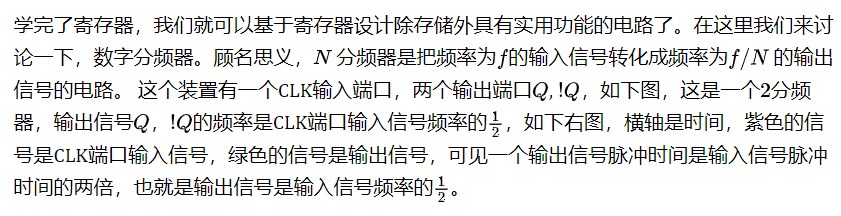

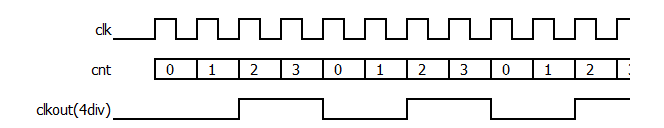

学完了寄存器,我们就可以基于寄存器设计除存储外具有实用功能的电路了。在这里我们来讨论一下,数字分频器。

2023-10-30 15:30:51 882

882

今天使用了STM32F10X定时器PWM输入模式,用来测量输入方波信号的频率和占空比,发现精度不高,设置定时器的时钟频率为36MHz,预分频为35,计数频率为1MHz,即精度为1us,当输入信号

2023-10-28 07:14:24

摘要:莱迪思(Lattice )半导体公司在这应用领域已经推出两款低成本带有SERDES的 FPGA器件系列基础上,日前又推出采用富士通公司先进的低功耗工艺,目前业界首款最低功耗与价格并拥有SERDES 功能的FPGA器件――中档的、采用65nm工艺技术的 LatticeECP3系列。

2023-10-27 16:54:24 235

235 低功耗单片机,怎么仿真

2023-10-20 06:32:01

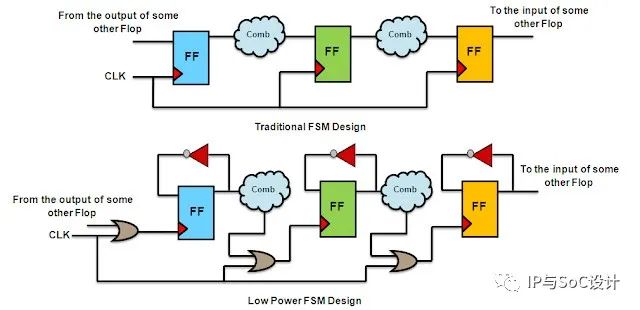

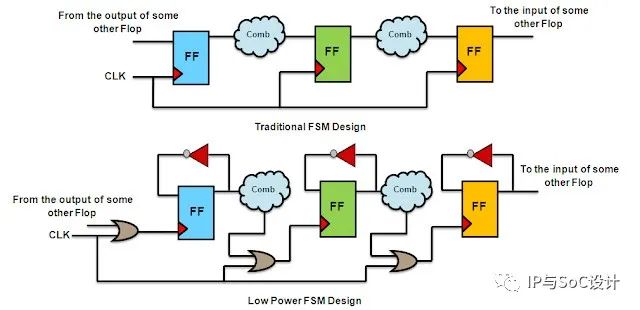

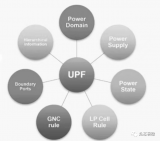

低功耗设计是当下的需要!这篇文章:低功耗设计方法论的必要性让我们深入了解了现代设计的意图和对功耗感知的需求。在低功耗方法标签下的时钟门控和电源门控的后续文章中,讨论了一些SoC低功耗设计的方法。在这篇文章中,我们将考虑一个这样的低功耗设计的FSM,可以推广到任何低功耗时序电路的设计。

2023-10-17 10:41:13 309

309

电子发烧友网为你提供ADI(ADI)最大500相关产品参数、数据手册,更有最大500的引脚图、接线图、封装手册、中文资料、英文资料,最大500真值表,最大500管脚等资料,希望可以帮助到广大的电子工程师们。

2023-10-11 19:16:44

电子发烧友网为你提供ADI(ADI)ADF4377 微波宽带合成器和集成VCO数据表相关产品参数、数据手册,更有ADF4377 微波宽带合成器和集成VCO数据表的引脚图、接线图、封装手册、中文资料

2023-10-11 18:54:41

电子发烧友网为你提供ADI(ADI)ADF4368:微波宽带合成器和集成VCO数据表相关产品参数、数据手册,更有ADF4368:微波宽带合成器和集成VCO数据表的引脚图、接线图、封装手册、中文资料

2023-10-10 19:02:33

和错误检测功能(奇偶和CRC)。在ACD模式下,读写器模块大部分时间处于休眠状态,由3K RC定时唤醒,以极低功耗侦测 13.56MHz的射频场和射频卡,检测到场或卡自动产生中断唤醒MCU。侦测场和卡

2023-10-08 16:01:27

NB-IoT的低功耗是怎么实现的

2023-10-07 07:05:52

RTC系统框图和组件 时钟源和分频器 硬件日历和警报 自动唤醒定时器 特色功能 数字粗略校准 参考时钟 外部引脚上的导出和导入功能 输出:警报、定时信号、校准时钟 输入:入侵检测 低功耗特性 STM32F2和STM32F1的RTC比较

2023-09-13 07:07:46

为什么单片机内置时钟源不经过pll也可以分频? 单片机内置时钟源不经过PLL也可以实现分频,原因在于单片机内置时钟源自带分频器,可以通过软件设置分频系数来控制内部时钟频率。 在单片机内部,通常会

2023-09-02 15:12:45 597

597 电子发烧友网站提供《KW45B41Z-EVK低功耗蓝牙射频系统评估报告应用.pdf》资料免费下载

2023-08-17 14:28:29 1

1 电子发烧友网站提供《K32W1低功耗蓝牙和802.15.4射频系统评估报告应用.pdf》资料免费下载

2023-08-17 11:00:45 0

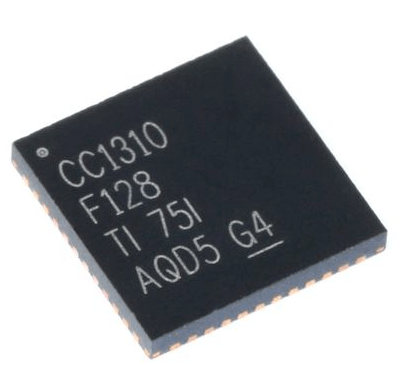

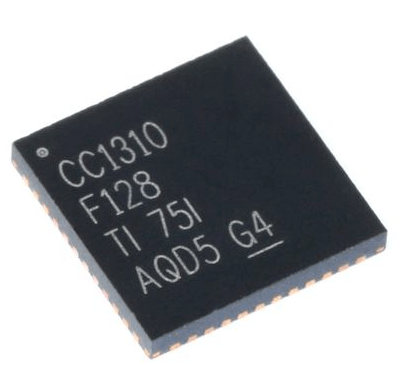

0 CC1310F128 是一款经济高效型超低功耗低于1GHz射频器件,凭借极低的有源射频和MCU电流消耗以及灵活的低功耗模式,CC1310F128可确保卓越的电池寿命,并能够在小型纽扣电池供电的情况下

2023-07-28 14:25:44 315

315

倍频器和分频器是两种常见的频率转换电路,它们的用途有一定的不同之处。

2023-07-14 09:27:46 799

799 分频器是一种电子设备,其主要作用是将输入信号的频率降低到较低的频率。它通过将输入信号分为若干个等分的周期,每个周期输出一个脉冲或波形,从而实现对输入信号频率的降低。

2023-07-14 09:26:18 697

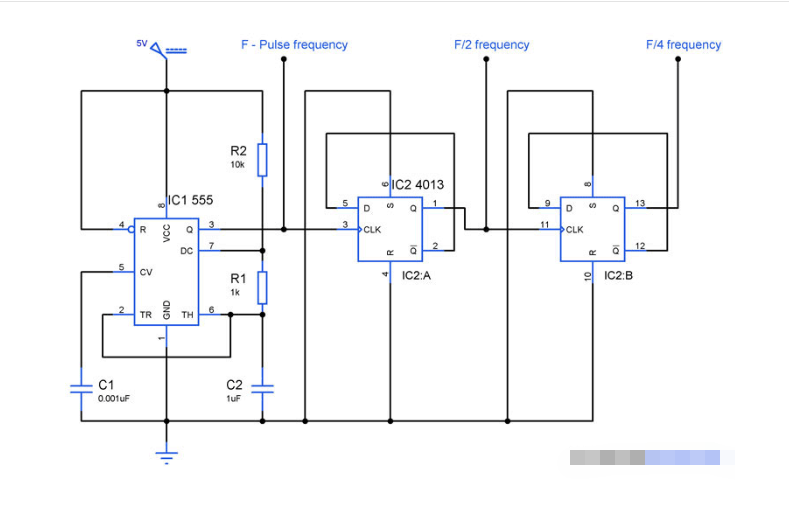

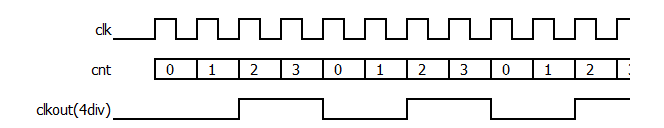

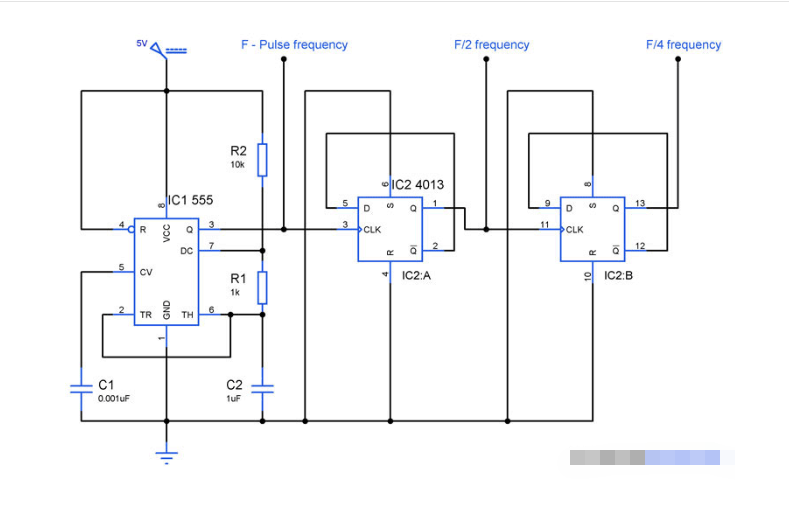

697 曾经遇到过这样一种情况,即您只有一个特定频率的信号源,需要获取多个频率的信号。如果是,这种电路可能是您需要在设计中使用的电路。上述电路是一个分频器,能够通过一定的因素对输入时钟频率进行分频。该分频器

2023-07-02 11:47:17 787

787

PHY6222

超低功耗蓝牙芯片

是一款低功耗蓝牙芯片,主要应用在数据传输的产品领域。例如,车载蓝牙、手环、医疗、蓝牙锁、蓝牙自拍杆、蓝牙健身器材等等。处理器为32位的ARM Cortex M0

2023-06-27 17:30:17

一般低功耗,是如何体现的呢?

2023-06-26 08:13:11

板载晶振提供的时钟信号频率是固定的,不一定满足需求,因此需要对基准时钟进行分频。要得到更慢的时钟频率可以 分频 ,要得到更快的时钟频率可以 倍频 。我们有两种方式可以改变频率,一种是 锁相环 (PLL,后面章节会讲解),另一种是用 Verilog代码描述。

2023-06-23 16:52:00 1149

1149

如题,这样一来,pwm的时钟哪怕是来自HCLK(029不支持PLL作为pwm时钟)最高50MHZ,经预分频器最少2分频的话,时钟最高只有25Mhz了?M0518pwm的预分频器可以设为0,不分频,并且可以用PLL作为时钟,最高频率可以达到100Mhz,相差4倍?

2023-06-19 08:14:45

;//clear interrupt flag

P31 =~ P31;

}

WKCON =0x04; //预分频配置256

RWK =255-78;//定时2s

2023-06-16 08:10:48

电子发烧友网站提供《在Verilog HDL中使用分频器的8位计数器的设计.zip》资料免费下载

2023-06-15 10:14:44 0

0 对于要求相位以及占空比严格的小数分频,建议采用模拟电路实现。而使用数字电路实现只能保证尽量均匀,在长时间内进行分频。

2023-06-05 17:20:51 956

956

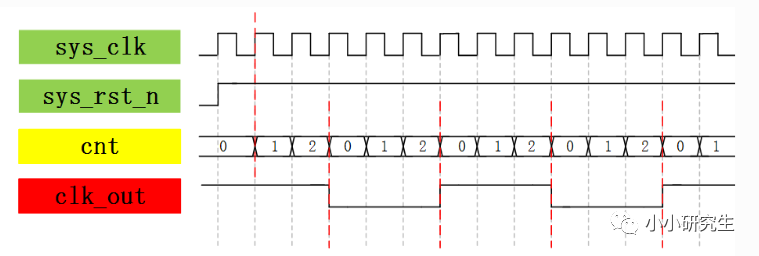

入门从简单开始,先来个三分频分析一下。三分频其实就是把输入时钟的三个周期当作一个周期,具体波形如图所示。

2023-06-05 16:57:23 751

751

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。

2023-06-05 16:54:33 680

680

我正在使用 S9KEAZN64AMLC MCU(定制板)。我使用内部振荡器 (32KHz) 在窗口模式下配置了看门狗。

配置的看门狗超时值为 500 毫秒。

当 启用256 时钟预分频器时看门狗

2023-06-02 09:46:17

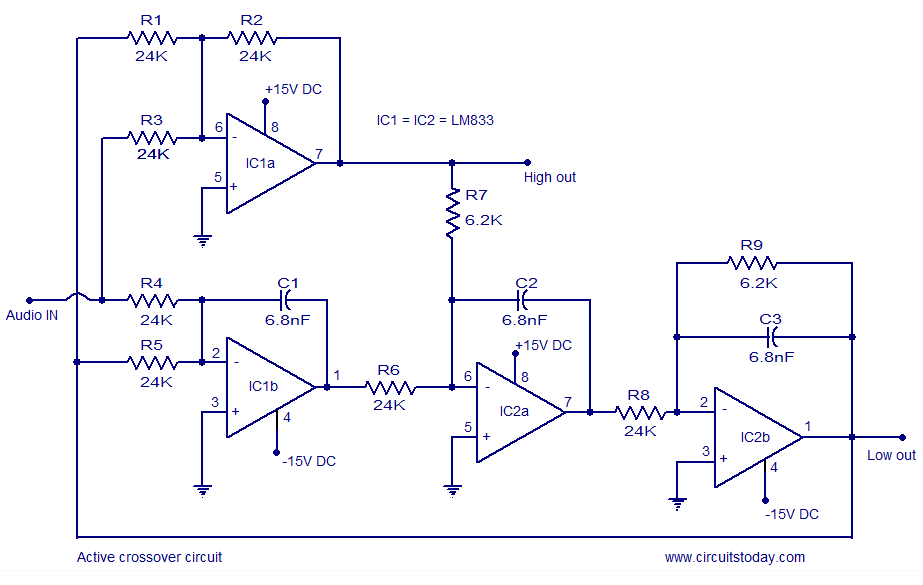

买了一个国产某jbl品牌的音箱,感觉唱歌声音发闷,不好听。分频器照片在这,拜托,谁能帮我画出电路图,我分析一下,红色白色蓝色黑色一边的4颗线接4个高音喇叭的,看起来这4个喇叭一样,但是说明书上面说

2023-06-01 22:41:05

)) *(以 Hz 为单位的时钟/预定标值)

对于 500 毫秒的超时周期,我在寄存器中加载了 250,预分频器为真,LPO 时钟配置。

但我并没有完全达到 500 毫秒,它仅在 480 毫秒时重置

我使用过操作系统,在每个 1ms 任务中我都在测试它

2023-05-24 08:00:17

FPGA分频器是一种常用于数字信号处理、通信系统、雷达系统等领域的电路,其作用是将信号分成多个频段。

2023-05-22 14:29:44 1025

1025

基于51单片机的分频器1(计数器实现)例程源代码

2023-05-18 09:54:09 0

0 基于51单片机的分频器2(外部中断实现)例程源代码

2023-05-18 09:53:28 1

1 想必各位ICer们在招聘JD上专门看到低功耗设计经验的要求,什么是低功耗设计呢?对于后端工程 师来讲,在物理实现方面就是引入多条电源线

2023-05-15 11:42:52 686

686

、 UART 、 SPI 、 QSPI 、 I2C 等通用外围通讯接口, ADC 、 OPA 、比较器等传感获取接口,以及 LPTIMER 、 WDT 等超低功耗模块接口,并内置 RC 高频和低频振荡器

2023-05-11 10:45:50

有可以进行mesh组网的低功耗蓝牙模块么?这种低功耗蓝牙模块组网支持多少个节点?是低功耗蓝牙模块BLE

2023-05-09 17:16:05

大家好,

我正在使用 S32K358 板,并在 OPWFMB 模式下配置了 4 个 PWM 输出通道,并使用下面列出的 EB tresos 为所有 PWM 输出通道使用相同的时钟预分频器和可配置周期

2023-04-27 06:16:07

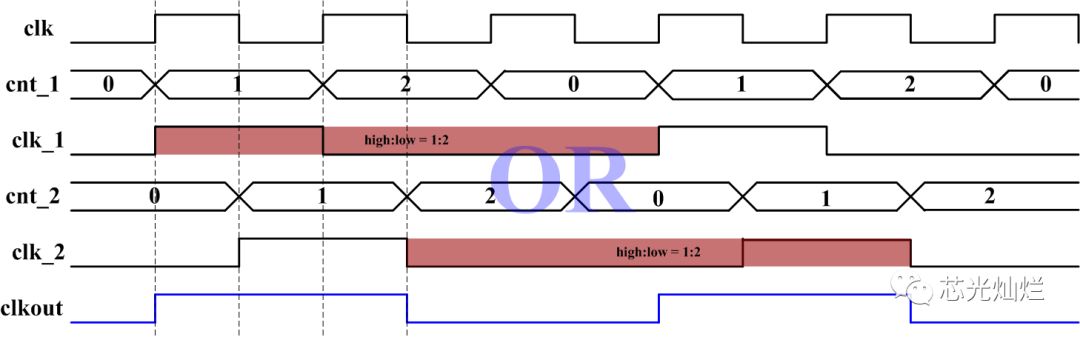

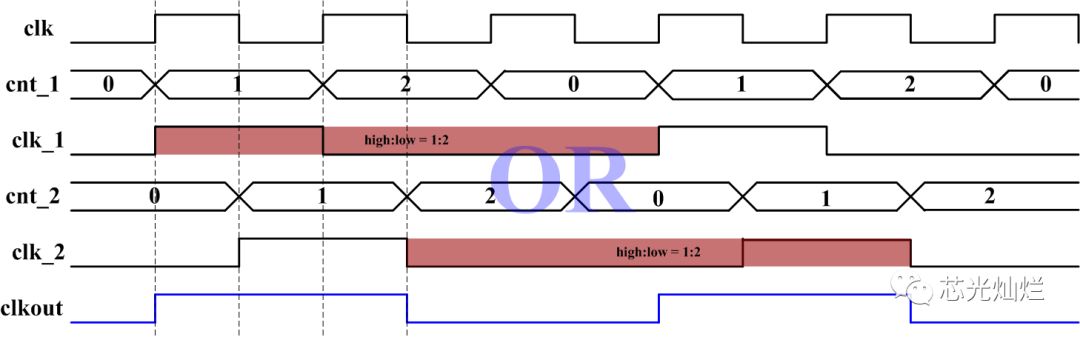

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1027

1027

时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。 比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

2023-04-25 14:46:25 5329

5329

---------- - --------------*/FMPLL.SYNCR.B.RFD = 0x2;/* PLL 斜坡 1 分频器:4 */ FMPLL.SYNCR.B.PREDIV = 0x00; /* 预分频器

2023-04-18 07:54:14

分频电路有两种类型,有源和无源。无源分频电路仅使用无源元件,它们非常简单,但它们浪费了大量能量并引起失真。有源分频器没有上述缺点,它们是HiFi音频系统的更好选择。有源分频器将输入的复杂音频信号分成

2023-04-02 14:53:58 2137

2137

我已经使用 PLL2_PFD2 (396 Mhz) 将 FLEXSPI 设置为 99 Mhz 时钟,所以我期望使用 4 分频器获得 99 MHz 总线时钟,或者分频器为 132 MHz 总线时钟3

2023-03-29 06:19:53

24级分频器和振荡器

2023-03-28 15:04:29

24级分频器和振荡器

2023-03-28 15:04:29

低功耗,低功耗,

500mA射频线性稳压器

2023-03-28 13:02:49

低功耗,低压差,射频线性稳压器

2023-03-28 12:44:46

低功耗,低功耗,500mA射频线性稳压器

2023-03-28 03:01:08

前面分别介绍了偶数和奇数分频(即整数分频),接下来本文介绍小数分频。

2023-03-23 15:08:04 655

655

上一篇文章介绍了偶分频,今天来介绍一下奇数分频器的设计。

2023-03-23 15:06:49 691

691

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 947

947

电子发烧友App

电子发烧友App

评论