图解半导体制程概论(2)

图解半导体制程概论(2)

逻辑IC

电子机器的动作所必需的内部信号处理大致可以分为模拟信号处理和数字信号处理。处理前者的是模拟用半导体器件,处理后者的数字信号处理的就是逻辑IC,逻辑IC中也有很多种类。

IC、LSI在制造程序上大致分为双极系列和MOS系列,还可以再分为混合两者的BiCMOS等复合型。

逻辑IC是执行数字信号处理的IC、LSI,双极系列(也就是双极逻辑)现在只有TTL和ECL,因此提及逻辑IC时,一般可以视为指CMOS逻辑系列以及BiCMOS系列。

而且,逻辑IC也可分为(1)通用逻辑、通用MPU之类的标准品;(2)ASIC(特殊用途用IC);(3)配合本公司规格开发的定制LSI专用产品这几类。

ASIC可以分成ASCP(顾客专用品)和ASSP(待业专用品),ASCP还能进一步细分成门阵列(GA)、可现场编程式门阵列(FPGA)、标准单元(SC)、嵌入式单元阵列(ECA)等。但是,即使是完全的定制IC,但通讯用或数码家电、车载系统中基本使用的电路及构件等都是相同的,开发上的平台大都由半导体生产厂家准备。通过以平台为基础进行设计,可以缩短开发时间。像这样定制IC和ASIC的界限没有明确区分,有时也将定制IC作为通用产品进行销售,由此可见,目前情况下这样的分类是非常困难的。

逻辑IC中有被称为MPR(microperipheral:微控制器周边设备)的器件。这是和于硬盘、图像处理、打印机等,主要用于计算机周边设备的专用LSI。各机器生产厂家大都采用ASIC的方法进行开发,和上述一样很难做出明确的分类。

逻辑IC可以分为制造工艺、应用领域、设计方法等3种,因此分类越来越困难。

逻辑IC、LSI的分类

О双极逻辑IC、LSI

TTL(Transistor Transistor Logic)

目前,只有部分生产厂家在生产,市场也在不断缩小。

ECL(Emitter Coupled Logic)

通过把NPN双极晶体管放在非饱和区域使用,并缩小理论振幅来获得高速特性,可用于要求高速性的IC测试器、通讯用等。

О代表性的CMOS逻辑IC/LSI

通用CMOS逻辑

MPU(Micro Processing Unit)

MCU(Micro Controller Unit)

DSP(Digital Signal Processor)

MPR(Micro Peripherals)

ASIC(Application Specific IC)

GA(Gate Array)

SC(Standard Cell)

DSP的例子

面向各种用途的逻辑IC

CMOS和反相电路

CMOS电路是由P通道能及N通道双方的MOS晶体管构成的电路。由于具有消耗电流少、高速化方便、抗杂音能力强、输入输出全摆式等特点,因此现在几乎所有的LSI都是在这种技术的基础上构成的。

CMOS技术

CMOS的结构是在N型基板中形成P通道的晶体管,在N型基板中做成较大的低浓度P型区域(叫娓娓动听 P井),在P井中形成N通道晶体管。还有与基相反,使用P型基板做成N井的。

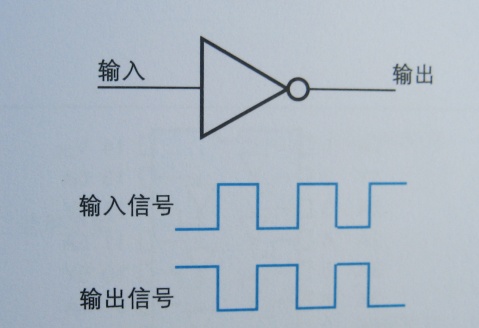

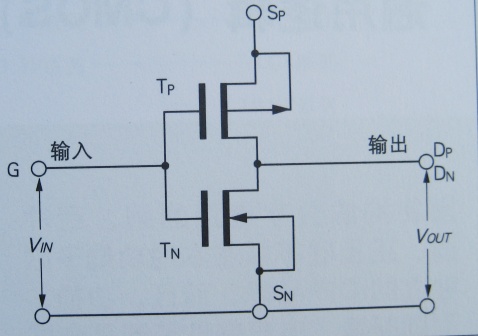

反相器

是逻辑IC/LSI的基本电路。如图所示,举例说明N型或P型晶体管(TN、TP)串联形成的反相电路。门极G上输入 “1”信号(SP电位)的话,TN将为ON,而TP则成为OFF。相反,输入“0”信号(SN电位)的话,TN为OFF,而TP则成为ON。对于任何输入,总有一个对应的晶体管是OFF状态,且由SP到SN的电流不会流通,因此消耗电流将减少(PMOS、NMOS的1/100-1/1000)。ONOFF切换时因寄生电容会充放电,因此随着工作频率增加,耗电量将增大。

优点

·非常少的耗电量

·快速的动作速度

·抗杂音较强

·和TTL可兼弱容性

·以低电压动作简单

缺点

·制作和序复杂且耗时长

用途

·标准逻辑(相当于TTL逻辑)

·几乎所有的数字LSI(MPU\MCU)\DSP\图象处理LSI\语音处理)

·电子计算器\钟表\游戏机

·掌上电脑

·电话机

·存储器(RAM\ROM)

·其他\客户规格逻辑电路等

CMOS反相器的图形记号和动作

CMOS反相器的电路图

例:CMOS反相器的结构图

通用逻辑(CMOS)

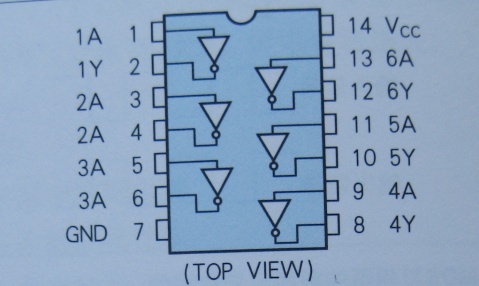

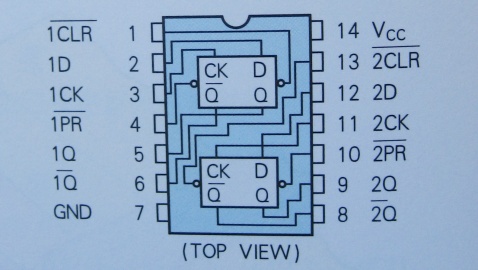

指将构成数字电路的闸、缓冲器、正反器等最基本的功能予以独立的IC产品群。而且,功能、引脚配置、电气特性等都是全球性标准化的产品群。在制程上还有CMOS、BiCMOS、双极等。

通用逻辑的主要功能

·逻辑运算功能(闸电路)图1

·开关功能

·数据的保持功能 图2

·总线驱动器(缓冲器)功能 图3

·计数器/除频功能

·电平移动功能

品名和标准化

附加74XXX的品名的标准逻辑作为74规格,其功能、引脚配置都加以标准化。如果品名(上述XXX的部分)相同,则功能、引脚配置无论哪个生产厂商、哪个系列都相同。系列名不同,数据处理速度、驱动能力等性能将不同,相反,如果系列名相同,则无论哪个生产厂商的性能大致相同。各系列中有数十品种到百数十品种的产品(功能)。

*通用逻辑最早以使用双极系列逻辑为主,现在能方便地实现低耗电量/低电源电压的CMOS逻辑已成为主流。而且,双极系列中,ECL也用于超高速应用领域(高速测试器等)。

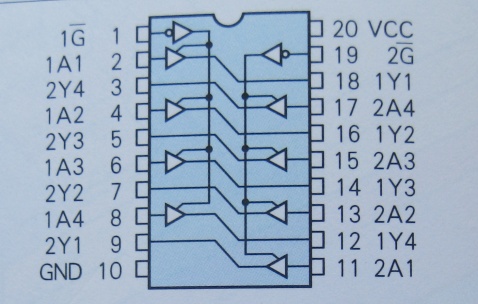

图1 闸IC例/74VHC04

图2 正反器IC例/74VHC74

图3 缓冲器IC例/74VHC244

品名的辨认证

通用逻辑的种类

微处理器(micro-computer,简称micon),作为计算机,通过LSI实现必要功能的小型计算机。从身边的家电产品到计算机及小型控制机器,被广泛应用在系统中。

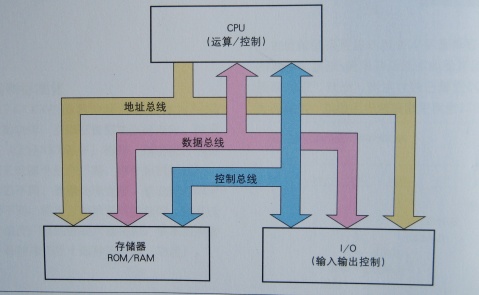

策处理器由进行运算、控制的CPU(中央运算处理装置)、进行记忆的存储器、进行和外部输入、输出的I/O的三部分构成。它们之间的信息交换,通过以下三务总线进行。

(1) 地址总线:用于指定存储器及I/O地址的信号线;

(2) 数据总线:用于将数据传输到地址总线指定的存储器及I/O的信号线;

(3) 控制总线:用于指示是否读取或写入存储器及I/O、或其他从CPU进行各种控制的信号线。

大规模系统中,将各种结构要素加以集成化后的LSI进行组合,小规模系统中,使用将这些集成到一块芯片上的LSI。

CPU和各种总线连接图

CISC和RISC

计算机心脏部分——CPU大致分为两类。一类是具有实现复杂且高度功能的命令,旨在提高性能的CISC。还有一类是将命令设置单纯化,旨在提高命令执行速度的RISC。

CISC方式

减少一个处理所需的命令数,旨在提高性能。通过1个命令就可以执行复杂的动作,因此叫做CISC(Complexed Instruction Set Computer:复杂命令集计算机)方式 。相反,命令长度可变,且比较复杂,因此解读需要一定的时间,用于执行的内部电路变得复杂,硬件设计的负担增加。

RISC方式

只具有少数的单纯性命令,旨在加快执行速度。命令长度固定,因此解码器电路及执行电路的规模较小。命令只有最基本的,因此叫做RISC(Reduced Instruction Set Computer:缩小命令集计算机)方式。命令数量少,因此需要软件的负担增加,但通过使用C语言等高级语言,可以提高开发效率。

CISC和RISO的特征

微处理器(MPU)

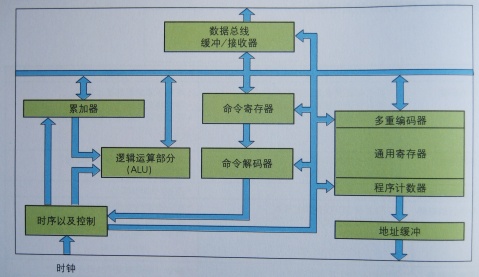

MPU是意气风发计算机所需的运算、控制功能集成到一块芯片上的LSI。随着半导体集成电路技术的不断发展,以往将多个IC进行组合后构成CPU的器件现在可以用一个MPU加以实现。

何谓MPU

我们将构成微处理器要素中的运算部分和控制部分合在一起的心脏部分叫做CPU,将这个CPU通过1个LSI加以实现的器件就是MPU(微处理器)。MPU不能单独作为计算机动作,因此将存储器及I/O进行组合后构成计算机。

MPU的基本动作

目前的大部分计算机都是从存储器读取命令、一个个逐步执行的被叫做诺依曼型的器件。MPU读取写在存储器内的程序,解读写在程序内的命令,按照指示,执行将数据存储到存储器内,或将数据取出等作业。

微处理器的功作单元例

微型周边设备(MPR)

所谓微型周边设备(周边LSI),是指存在于MPU和输入输出设备之间接口的LSI。主要分为支持MPU的LSI和控制周边设备以及传输数据的LSI,根据不同用途,有各种种类。

MPR用于减轻对MPU的负担,提高整个微控制器系统的性能。因为通过专用LSI控制周边设备,因此也可以减轻软件的负担。MPR不断在必须采取图形用及MPEG等图像处理、声音识别等高速处理的领域中得到应用。

MPU支持用MPR

存储器管理单元(Memory Management Unit:MMU)

采用大量且多种存储器的系统中,管理存储器变得复杂,因此要使用MMU,减轻MPU的负担。

可编程中断控制(Programmable Interrupt Control:PIC)

在需要多个中断输入的系统中,通过PIC扩大中断处理的功能。在连接很多周边设备等情况时,发挥整理交通的作用。

直接存储器存取控制器(Direct Memory Access Controller:DMAC)

通过使用DMAC,可以在不通过MPU的情况下,直接在周边设备及存储器之间高速传输数据。在DMAC传输数据期间,MPU也可以进行其它处理,因此可以大幅度提高系统的效率。

周边控制用MPR

实时时钟(Real-Time Clock:RTC)

这是用于系统的时钟专用LSI。使用MPU的数据总线,输入输出时刻数据。一般情况下,备有专用电池,即使系统电源断开,也将保持时钟动作。

硬盘控制器(Hard-Disc Controller:HDC)

这是用于控制硬盘驱动器的专用LSI。硬盘可以高速保存大容量的数据,因此成为计算机的辅助存储装置的主流。

除此以外,还有图像处理用图形显示控制器(Graphic Display Controller:GDC)、CD-ROM/DVD-ROM驱动用的伺服处理器、音频用数字信号处理器(DSP)等各种专用的MPR。

微控制器(MCU)

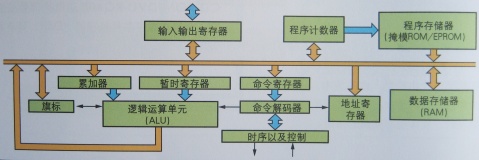

微控制器是将除了执行运算及控制的MPU功能以外,还有存储功能、输入输出控制功能集成在一块芯片LSI上的器件。也叫做单芯片微控制器。

何谓MCU

MCU在1个LSI中,收纳应用设备所必须的大部分功能,做成极为小型的电路,因此成本低,适合量产。作为安装在家电设备及产业设备等中的控制器,被大量使用。应该内置的周边功能根据应用设备不同而不同,因此针对特定用途的性格较强,根据各种用途,做成多品种的MCU。

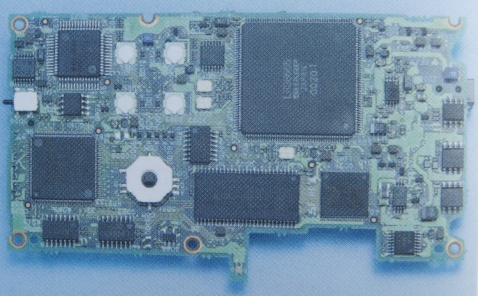

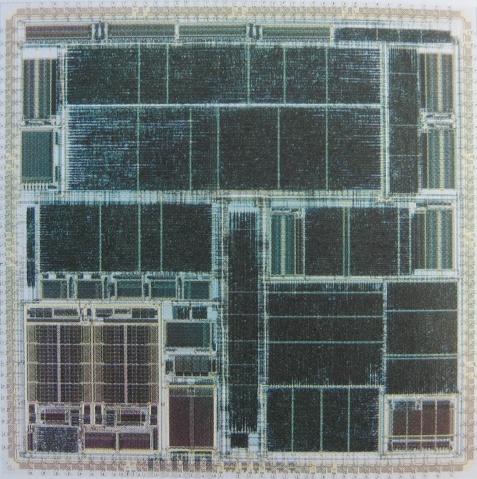

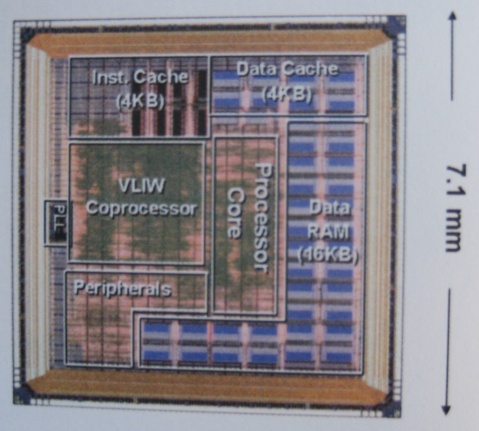

芯片放大照片

芯片的放框(左面照片)

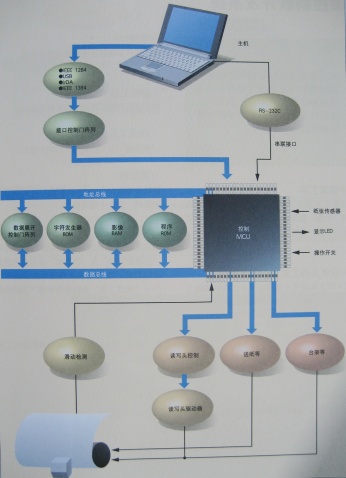

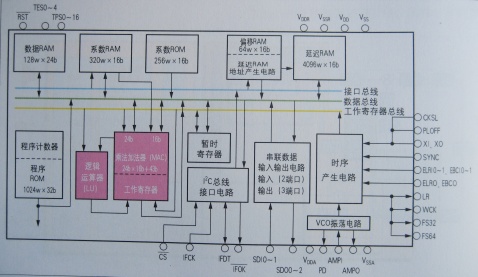

微控制器的内部结构例

MCU应用到彩色串联打印机的举例

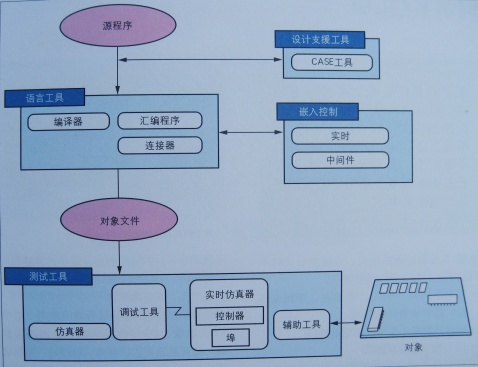

微控制器开发系统

开发应用了微控制器的产品时,必须开发产品本身(硬件)及使微控制器动作的程序(软件)。这些开发以及验证所必须的一套器材统称为开发系统。

★ 语言工具

语言工具是对用户源程序执行从编码到编译、汇编、链接等一系列作业,用于输出对象(执行)文件的系统的总称。

★ 设计支持工具(CASE工具)

CASE工具是用于支援以设计工程到编程工程以及文档制作为中心的维护工程的系统名称。

★ 嵌入控制

嵌入控制是对用户源编程提供特定功能的软件的总称。

<实时OS>

用于控制安装系统中多任务动作的软件。

<中间件>

通过软件实现以往靠硬件实现的功能。

测试工具

用于确认对象文件动作的系统的总称。

<调试工具>

“模拟器”及“仿真器”的用户接口。

<模拟器>

用软件模拟MCU动作的软件。无须控制器的系统,适合于理论调试。

<实时仿真器>

在实际设备系统上确认动作的方法,是将“仿真控制器”及“仿真埠”进行组合的系统的总称。我们将在此设备上加上用户接口——“调试工具”后的系统叫做“实时仿真系统”。

<辅助工具>

用于联结“实时仿真器”和用户对象的工具的总称。

开发系统的概念图

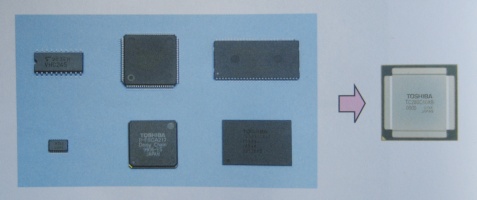

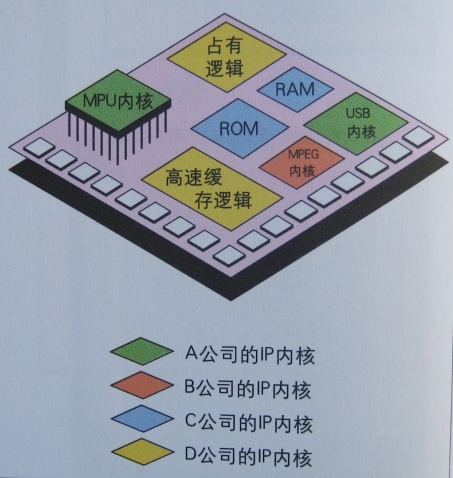

何谓系统LSI

主要将数码家电、手机等通信用、以及汽车用所必须的系牢进行集成的大规模设备专用的LSI即为系统LSI。随着应用领域的不断扩大,各种系统LSI的开发正在不断发展,超出千万栅的产品也陆续登场。

系统LSI没有明确的定义。好像各公司有不同的定义,以下是一般的例子。

·具有多内核(MPU、存储器、逻辑或模拟)的单块集成电路LSI;

·担当系统或子系统主要功能的LSI;

·10万栅以上规模的LSI;

·针对单个或多用户的特定应用所开发的LSI。

不包括单芯片的微控制器及电子计算器用、时钟用LSI、SRAM及快闪式存储器的多芯片封装产品、系统模块。

系统LSI的具体应用领域有数码家电(数字TV机顶盒、DVD数码相机、数码摄像机等)计算机及周边设备用(MPEG、图形等图像处理、硬盘用马达及磁头控制)、通信用(网络、手机等)、汽车用(引擎控制、导航、智能传输系统等)等,还有一部分为产业用而开发。

用于数码相机的系统LSI

系统LSI的具体应用领域有数码家电(数字TV\机顶盒\DVD\数码相机\数码摄像机等)

下一代多媒体LSI的系统图

手机的方框图

何谓DSP

DSP正如其名(Digital Signal Processor),是将数字信号处理加以特殊化的处理器。一般被称为DSP的信号处理用处理器的内部硬件或结构和一般的MPU有几大不同点。

DSP的重要特征如下所示。

·拥有高速乘法器(一般情况下也具有累加运算结果的功能);

·具有哈佛型结构(针对程序和数据拥有多个专用总线的结构);

·将程序存储器和数据存储器进行分离、独立;

·拥有高速化数据地址计算单元。

甚至还有根据需要,拥有AD转换器等。即以高速乘法器为中心的哈佛型结构、程序存储器和数据存储器加以分离、独立,具有高速化数据地址计算单元的处理器叫做DSP。通过这些结构,比如必须采用乘法及其运算结果的累加的数字式滤波器,可以在一般处理器十几倍的速度下进行运算。但是,一般的MPU也不断发展高速化,也开发出了具有上述特征的产品。今后,MPU和DSP的区别越来越难。促使区别越来越难的是用于实现上述共同的高速化的各种结构、硬件。因为速度要求越来越快,因此DSP和MPU一样,有使用相同结构的趋势。

应用领域

·数字TV等数码家电的各种信号处理用;

·数字手机的模拟、数字式基带处理、声音压缩、调制/解调制用;

·硬盘、DVD-ROM等存储设备的轴马达及磁头(读取器)传动器的旋转控制以及精密定位用;

·自动控制马达的转矩控制、速度控制、精密定位用。

而且,DSP的应用领域中采用高速的RISC处理器的情况也越来越多。在必须彩高速运算处理的应用领域中,过去好像不能将RISC和DSP绝对性的分开。今后,在RISC中安装DSP的主要功能、硬件的一部分,或者反过来安装,两者的分界线越来直不明显。

系统LSI应该以最适合的信号处理运算法则以及必须的结构,来符合其所需要的功能。无论是DSP还RISC处理器,甚至CISC处理器的主要功能、硬件,都是上述整合的方向。

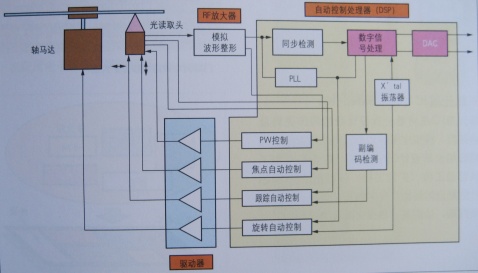

DSP IC的结构例

CD用DSP(将应用加以特殊化的专用DSP例)

ASIC

ASIC(Application Specific Integrated Circuit)是面向特定IC的总称,包括全定制LSI、半定制LSI等各种LSI。代表性的有门阵列、单元基IC、嵌入式阵列。

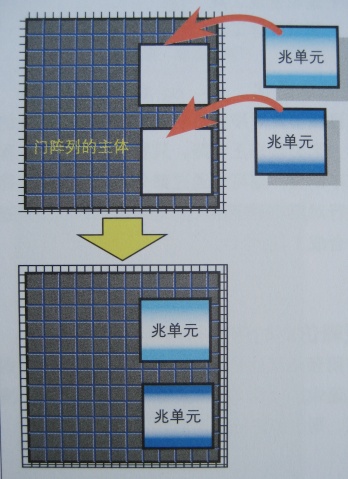

★门阵列(Gate Array)

门阵列是半定制LSI的一种,事先准备好的称为主体的晶圆。主体是晶体管呈阵列状铺设的结构。门阵列的制造是在逻辑设计结束后在主机上实施布线,构成希望的逻辑电路后完成。为此,具有开发时间短的特征。

★单元基IC(Cell Based IC)

单元基IC是将最合适设计后的内部逻辑及存储器、模拟电路作为单元事先准备好,再通过组合后设计LSI的器件。单元基IC为了从前道工程(扩散工程)开始制造,LSI芯片的制造时间比门阵列的长,但具有设计灵活性高、功能高、集成化高等特征。

单元基IC(Cell Based IC)

ASIC实施例(嵌入式阵列)

嵌入式阵列是在门阵列的主体内安装单元基IC的高集成存储器及高功能微单元的阵列。具有和单元基IC相同的集成度、高功能特征,同时也具有和门阵列相同的开发时间短的特征。

优点

·小型化、重量轻

·高可靠性

·开发效率的提高

·高速化

·低价格化

·保持机密

·低耗电

用途

·计算机、工程、工作站、计算机相关设备

·OA设备

·通信设备

·数字AV设备

·一般产业用电子设备

·家庭用电子设备、游戏机等。

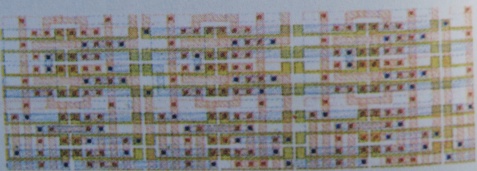

CMOS ASIC的芯片照片

主体芯片的部分扩大图

门阵列布线后的部分扩大图

单元基IC的说明图

各种ASIC的集成度和开发时间

嵌入式阵列的概念

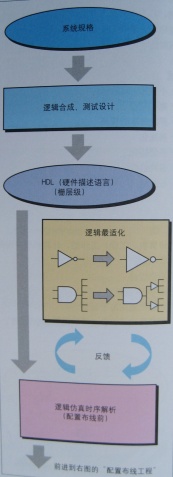

ASIC产品开发流程

ADIC产品开发,从确定系统规格到实际制造为止的工程中,难过各种EDA(Electronic Design Automation)工具进行处理、验证。

逻辑合成、测试设计

使用逻辑合成系统,从上位设计记述生成栅极的设计记述。还根据需要进行考虑了测试的设计。

★使用EDA工具

逻辑合成工具

测试设计工具

逻辑最适化

当逻辑仿真时序解析的结构发生违反情况的话,则必须修正电路。只要违反的地方、程序不明显,都可以通过部分修正原先的电路进行对应。时序违反的电路修正可以使用逻辑合成工具执行。

逻辑仿真时序解析(配置布线前)

使用预估值进行仿真。如果没有违反,则快速sign-lff(签名发布),但如果违反情况,则必须进行逻辑最适化。

★EDA工具

Verilog模拟工具

VHDL模拟工具

时序解析工具

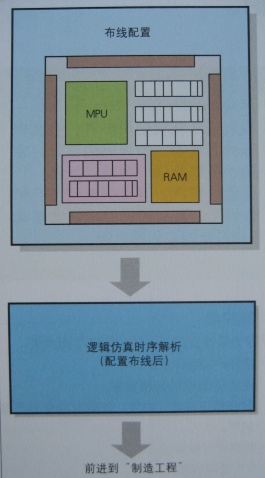

配置布线

以sing-off(签名发布)后的栅层级设计记述为基础,以满足时序之规定进行配置布线。一旦结束配置布线处理,将计算出基于实际配置布线的时序信息。

★使用EDA工具

配置布线工具

CTS(Clock Tree Synthesis)工具

论逻辑仿真时序解析(配置布线后)

使用实际的配置布线结果,进行验证。处理内容和配置布线之彰相同。如果结果没有问题,将第二次sing-off(签名发布),如果有违反的情况,则必须再次进行电路修正,反馈到配置布线工程。

Sign-off:就是半导体制造商和用户就LSI设计正确性相互进行确认并承诺。

ASIC产品开发流程

ASIC的完成(表面)

ASIC的完成(背面)

I P

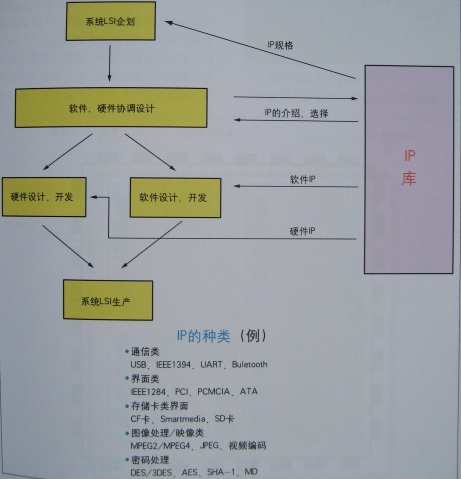

IP(Intellectual Property)一般表示专利和知识产权,但在半导体领域中,表示已经设计完成的功能电路块(内核、单元),即设计资产。可以分成硬件IP和软件IP,其利用已经成为大规模LSI设计效率化的关键。

IP的种类

IP作为设计资产,大体分为以下两大类。

·硬件IP(硬件宏)

用于LSI制造的掩模数据。

因模拟及配置(布置)使得时序变为严格的IP。

·软件IP(软件宏)

RTL或网络表

大部分的数字逻辑IP。

容易对应设计规则时代的变迁。

IP的流通和标准界面化的重要性

现在若由一家公司准备所有的IP,适时地提供是比较困难的。对系统机器生产厂商而言,用于提高功能的附加价值较高的IP由自己公司开发,除此以外的标准性IP从外部(从半导体供应商或IP专业供应商)调配的体制非常有必要。而且,为了将从不同供应商获得的IP进行组合,从而开发效率良好的系统LSI,需要公开的标准界面,现在除了VSI(Virtual Socket Interface)联盟以外,还有几个标准化团体正在不断推进该进程。

使用IP的有效性

随着LSI的高集成化的同时,集成在1块芯片上的功能的种类也不断多样化。例如,在多媒体相关系统中,图像处理、通信控制、数据控制、数据存储等多种功能组合在一起。为了将这些功能集成在1块芯片上,必须混合集成数字逻辑电路、模拟、存储器等不同的器件及电路技术。另一方面,对系统产品投入市场的交货期短的要求越来越强。

虽然LSI不断大规模化、多功能复杂化、高性能化,但目前尚处于不允许包括电路设计验证在内的LSI开发时间增大的情况。为了解决这些问题,使用已经得到验证的设计资产(IP)是极为有效的,可以大幅度削减设计时间。

将IP进行组合后的系统LSI

可编程器件(CPLD/FPGA)

可编程器件是指使用RAM或ROM,在可以实现程序的范围,使用者可以实现任意电路的器件。代表性的器件有CPLD、FPGA。

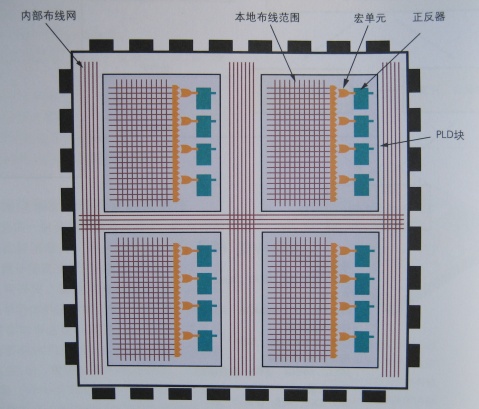

★CPLD(Complex Programmable Logic Device:复杂可编程逻辑器件)

拥有多个逻辑块(PLD块),可利用内部布线网连接任意块之间的结构。EEPROM、FLASH方式为主流方式。

CPLD的结构

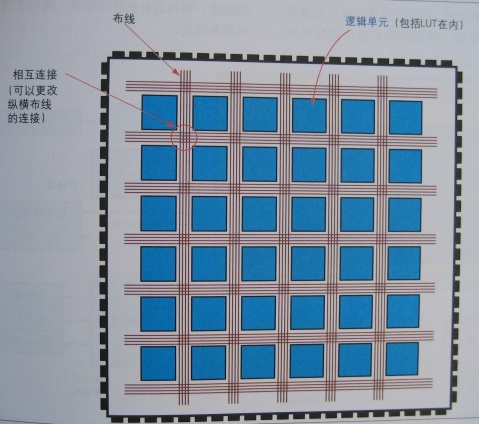

★FPGA(Field Programmable Gate Array:现场可编程门阵列)

是一种同时包括用户可以自由设定、更改功能的正反器等存储器件在内的集成电路,拥有整体可以相互连接的逻辑单元阵列,有2种类型。与CPLD相比,容量较大,适合于大规模的电路

(基于SRAM)可重复编程(reprogrammable)

指SRAM决定相互连接或是以检查表格(LUT)决定逻辑功能的器件,所以可以多次重写覆盖。但是,一旦电源断开,写入的内容不能保存下来,因此采取安装到线路板时,附上电池或准备好非挥发性存储器,将布线信息保存到内部,在接入电源时装载该内容的方法。

可一次编程(OTP)

以保险丝互相连接,一旦写入后,不可以重写覆盖。

优点

·较短的开发TAT(周转时间)

·低廉的开发费

用途

·个人计算机、工程工作站(EWS)、计算机相关设备

·备通信设备

·数字AV设备

·一般产业用电子设备

·家庭用电子设备、游戏机等通信机器

FPGA的结构

复合器件技术和混载技术

没有明确的定义,但作为复合器件技术,拥有将双极型和CMOS逻辑或功率器件等集成在单片电路的制造技术。混载技术是指将向系统LSI、ASIC等逻辑LSI中混合安装存储器的技术。

复合器件技术

电子设备中有数字信号处理、模拟信号处理、大功率控制,甚至还有高频信号处理等很多信号处理,使用符合各自用途的半导体。例如,复合器件技术是将数字和模拟信号处理集成在一块芯片上、或同样将数字信号处理和功率控制电路集成在一块芯片上所必须的半导体技术。

另外还开发了逻辑IC中混合安装模拟电路、功率器件(双极功率晶体管、功率MOSFET、IGBT等)的工艺,这些也可以叫做混载技术,一般情况下也可以将该技术叫做混合器件技术。这些代表性器件有BiCMOS、IPD(Intelligent Power Device)等。

这是将模拟信号处理电路、数字信号处理电路、功率器年、存储器等集成在一块芯片上的技术,根据混合安装的电路、器件不同,有很多种类。

目前,正在开发系统LSI内混合安装存储器、显示用专用LSI的器件、马达、螺线管等制动器的驱动器、逻辑LSI内混合安装一部分模拟电路等多种混合LSI、复合器件装置。

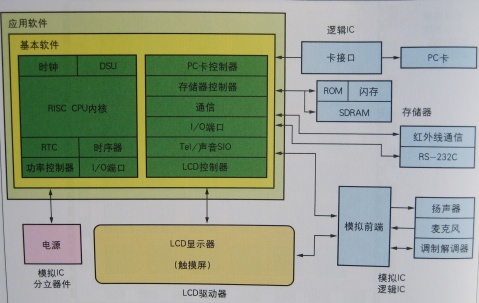

混载技术

电子设备很少有只采用一种半导体的应用,一般情况下使用很多半导体。例如,如图所示的PDA(便携式信息末端)中,只是信号处理电路中就使用了专用LSI、微控制器、存储器、驱动器IC等很多半导体。

将这些器件集成在一块芯片上,可以节省空间、减小体积、提高可靠性、降低成本等,但必须解决各种半导体制程工艺上的不同而引起的各种问题。

过去,曾经在高集成化的存储器工艺中混合安装了追求高速化的逻辑,而目前是在同一制程中将存储器和逻辑集成在一块芯片上,也就是混合化。

PDA的系统结构

系统LSI和混载技术

在图形等图像处理所必需的系统中混合安装了存储器,旨在提高信号处理速度。

当然在系统LSI中也采用了混载技术。但是,采用了和一些目的不同的其他小规模逻辑IC使用。也就是除系统LSI以外,都是集成在一块芯片上,这样可以提高可靠性、减小体积重量等,但很少是以提高信号处理上的特性为目的的。

系统LSI为了增加提高信号处理上的机能、缩短开发时间的目的,积极采用混合工艺。例如,将存储哭混合在一起后,将原来连接在外部的存储器不能灵活决定存储器总线长度变为可能,并可以通过并列处理实现高速化。也解决了外部连接存储器时因布线而产生的信号延迟问题。

另外,混合安装闪存,实现了程序的重复写入,从而提高了开发的灵活性,结果可以实现缩短从开发到大规模生产的时间。

微控制器一般为了储存程序等,搭载ROM或RAM等存储器,但这个不叫做存储器混载技术。

针对ITS(高度交通系统)的图像识别LSI

存储器混载技术

使用混合安装DRAM的系统LSI时,可以削减封装的总引脚数,除了实际安装时节省空间、高速化以外,还有很多优点。而且,混合安装闪存后,可以提高IC设计的灵活性,实现QTAT化。

相对于半导体的内部布线而言,外部布线较长,且延迟及与布线有很深关系的漂移电容较为严重,而且少了与布线的电阻较大的外部存储器的连接,即可减少延迟。甚至内部总线可以在半导体内部进行自由设定,因此可以通过灵活的并列处理实现高速化,特别是在信号处理方面具有高速化的优点。

而且,对EMI(Electro Magnetic Interference,电磁波干扰)采取对策方面也非常有效,还可以灵活设定存储器容量。像这样,混合安装存储器的LSI不是单纯的将外置存储器内置,而是积极用于图像处理或图形等超高速信号处理所必须的电路中。

混合安装了可以重复写入的闪存后,写入的程序在设计后也可以修正,因此可以实现灵活的开发量产体制。

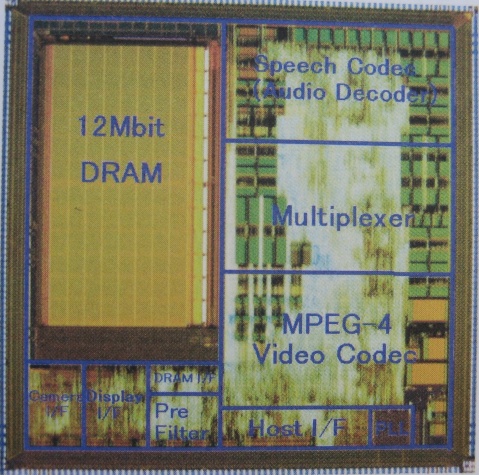

以下照片中的LSI中安装了个人电视电话及多媒体浏览器所必需的多个信号处理部分及12M位DRAM的同时,内置用于连接CMOS型固体摄像器件及液晶面板的图像输入输出接口电路。

内嵌针对手机用MPEG4混合安装DRAM的系统LSI

SOI、IPD、BiCMOS技术

作为器件之间的分离,从以往PN接合时到利用绝缘物氧化硅的制程技术就是SOI。作为混合功率器件、逻辑、模拟电路的制程技术,有IPD、BiCMOS技术。

★SOI

SOI(Silicon On Insulator)是一种在氧化硅的绝缘体上形成单结晶硅的制程技术。IC可以将很多器件集成在一块芯片上是因为将分离各器件之间的P型及N型半导体区域反偏置,在各器件之间进行电气性绝缘。将PN接合反偏置后进行绝缘的方法会由于寄生器件产生故障、或由于泄漏电流引起各种问题,通过采用绝缘体—氧化硅改善问题的制程就是SOI技术。

该技术大致可以分为功率系列和信号系列。

★IPD(Intelligent Power Device)

IPD是采用可以内置逻辑电路、模拟电路以及功率器件的数百个到数千个器件的较小规模复合器件技术的器件。

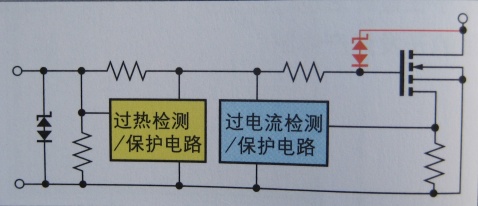

应用领域有汽车用(ABS、气囊)、各种马达驱动器、灯驱动器、螺线管驱动器等。该制程可以将输出PW-MOS、Nch MOS、Pch MOS、PNP Tr、NPN Tr、电阻、电容器等所有器件都集成在一块芯片上,适合于多功能产品。还有采用简单的制程,在MOS FET中内置过电流及过热保护功能电路的复合MOS FET。

★BiCMOS

这是一种将善于处理模拟信号的双极器件技术和善于处理逻辑信号的CMOS技术进行融合后的制程技术。

有可以处理功率的高耐压系列、大功率系列BiCMOS技术和不能处理大功率的高频(以及高精度模拟系列)以及可以处理逻辑信号的高频BiCMOS技术。

右图为发挥后者特征的TV用混合信号LSI方框图、芯片照片、结构图。TV用LSI中也不断发展引进模拟CMOS技术,以内置滤波电路。

IPD的芯片照片

复合MOSFET(混级驱动器)

TV信号处理LSI的方框图

LSI芯片

LSI的结构图

非常好我支持^.^

(2) 100%

不好我反对

(0) 0%

相关阅读:

- [电子说] 芯片为什么用铜作为互联金属?铝为什么会被替代呢? 2023-10-12

- [电子说] 芝识课堂【CMOS逻辑IC基础知识】—设计大业始于学会读数据表(下) 2023-09-21

- [电子说] 群创3.5 代线转为面板级封装,明年底量产 2023-09-18

- [模拟技术] 什么是FET?FinFET将半导体制程带入新境界 2023-07-12

- [电子说] Nexperia(安世半导体)率先推出纽扣电池寿命和功率增强器 2023-07-11

- [电子说] 揭秘半导体制程:8寸晶圆与5nm工艺的魅力与挑战 2023-06-06

- [电子说] 半导体制程280C高温耐酸碱PI基材双面胶带 2023-04-20

- [电子说] CD4051八选一模拟开关 逻辑IC 模拟电路 2022-05-05

( 发表人:admin )