鉴相器 ,鉴相器的分类和原理是什么?

鉴相器 ,鉴相器的分类和原理是什么?

鉴相器

鉴相器,顾名思义,就是能够鉴别出输入信号的相差的器件。它是PLL的重要组成部分。

PLL的概念

我们所说的PLL。其实就是锁相环路,简称为锁相环。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

目前锁相环主要有模拟锁相环,数字锁相环以及有记忆能力(微机控制的)锁相环。

PLL的组成

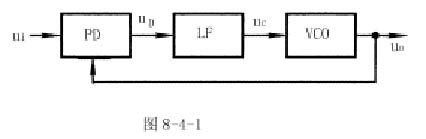

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

环路滤波器的基本概念和功能

其实它是滤波器中的一种类型,因为这种滤波器使用在环路中,因此得名环路滤波器。它是PLL(锁相环)电路中的重要组成部分,要了解它必须先要对PLL的原理有一定了解。PLL的原理如下:

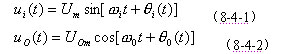

设外界输入的信号电压和压控振荡器输出的信号电压分别为:

式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为:

此时需要用低通滤波器LF将上式中的和频分量滤掉,快速衰减高频干扰,剩下的差频分量作为压控振荡器的输入,在环路跳出锁定状态时,提高环路以短期存储,并迅速恢复环路。

鉴相器,顾名思义,就是能够鉴别出输入信号的相差的器件。它是PLL,即锁相环的重要组成部分

鉴相器-原理特性

使输出电压与两个输入信号之间的相位差有确定关系的电路。表示其间关系的函数称为鉴相特性。鉴相器是锁相环的基本部件之一,也用于调频和调相信号的解调。常见的鉴相特性有余弦型、锯齿型与三角型等。

鉴相器特性用ud(t)=kdf【θe(t)】表示。式中kd为鉴相器的增益系数;θe(t)=θ1(t)-θ2(t),表示两个输入信号之间的相位差。函数f【·】表示鉴相特性,它反映鉴相器的输出电压 ud(t)与相位差的关系。常见的鉴相特性有余弦型、锯齿型与三角型等。

鉴相器

鉴相器-分类

鉴相器可以分为模拟鉴相器和数字鉴相器两种。

二极管平衡鉴相器是一种模拟鉴相器。两个输入的正弦信号的和与差分别加于检波二极管,检波后的电位差即为鉴相器的输出电压。其鉴相特性通常为余弦型的。鉴频鉴相器是一种数字鉴相器。两个输入信号是脉冲序列,其前沿(或后沿)分别代表各自的相位。比较这两个脉冲序列的频率和相位即可得到与相位差有关的输出。这种鉴相器的鉴相特性为锯齿形。因它兼具鉴频作用,故称鉴频鉴相器

二极管平衡鉴相器 这是一种模拟鉴相器,原理电路如图1。二极管D1、D2和C1R1、C2R2构成两个峰值检波器。两个输入的正弦信号u1(t)=U1sin(ωt+θ1)、u2(t)=U2sin(ωt+θ2) 的和与差分别加于检波二极管D1和D2,检波后的电压差即为鉴相器的输出电压ud。当U2U1时,ud∝U1cos(θ1-θ2)。在这种情况下,它的鉴相特性是余弦型的(图2a)。

鉴相器

鉴频鉴相器 这是一种数字鉴相器。两个输入信号是脉冲序列,其前沿(或后沿)分别代表各自的相位。比较这两个脉冲序列的频率和相位即可得到与相位差有关的输出。图3是一种鉴频鉴相器的框图。比相器可由触发器构成。当两个输入信号u1和u2同频同相时,触发器没有输出,充电电流等于零。当u1脉冲序列超前于u2时,触发器产生一个其宽度与相位差成正比的正脉冲,充电电路被充电,其输出电压为正值,大小与充电脉冲宽度成正比。若u1落后于u2,则触发器输出一个负脉冲,充电电路的输出为负值。这种鉴相器的鉴相特性为锯齿形(图2b)。这种鉴相器兼具鉴频作用,故称鉴频鉴相器。

鉴相器

取样鉴相器 由取样器和保持电路两部分组成。图4是原理电路,4个二极管构成取样器,电容器Cd构成保持电路。当被鉴相信号u0(f0,θ0)的频率f0正好等于取样脉冲ui(fi,θi)的频率fi的整数倍时,每次取样的电压值相等。鉴相器的输出电压ud为保持电容器Cd上的直流电压。当f0厵nfi时,每次取样的电压值不等,输出电压ud为阶梯形的交流电压。取样鉴相器输出的电压和相位差成正弦关系。

鉴相器

鉴相器-数字鉴相器

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的;此外,环路组成部件也全用数字电路实现,故而这种锁相环就称之为全数字锁相环(简称DPLL)。数字锁相环主要由数字鉴相器、可逆计数器、频率切换电路及N分频器四部分组成。数字鉴相器就是DPLL的主要单元。

基本原理:

在比相的信号虽然经过了一系列处理,但仍可能含有干扰信号。其信号的特点:

1.噪声的影响在转变成方波后只存在于理想方波的前后沿附近,而高低电平 中 间部分不受噪声影响;

2.被鉴相信号的频率一致,而且存在一定的相位差,使两路信号的沿互相错开 ,每一路受噪声影响的前后沿正好对应于另一路不受影响的电平部分。

而一般的鉴相器都没有抑制噪声的能力,即使是一点小的抖动也将导致鉴相的失败。故本设计利用触发器的边沿触发和锁存功能设计了高抗噪声数字鉴相器,采用VHDL语言编制调试了鉴相器功能。如图是经过编译以后生成的原理图。

鉴相器

输入信号的相位Φa与反馈输人信号的相位Фb的相位差Фe=Фa-Фb时,鉴相器输出低电平。当Фe > 0 时,鉴相器输出信号Ud(t) 输出正比于相位差的脉宽信号,Up(t) 输出低电平。当Фe < 0时,鉴相器的输出信号Up(t)输出正比于相位差的脉宽信号,Ud (t)输出低电平。线性鉴相范围为±л,线性鉴相增益kd =1/л(v/rad)。

下面对该鉴相器的抗干扰能力作定量分析。若设干扰信号是峰值为An的正弦信号,被鉴别的两路信号的相位差为α,其值为As,则有:

鉴相器

实际上,大多数干扰为随机白噪声,所以信噪比为:

鉴相器

从上式可以看出该鉴相器具有较强的抗干扰能力,这也保证了整个系统对恶劣环境的适应能力。

非常好我支持^.^

(9) 2.4%

不好我反对

(360) 97.6%

相关阅读:

- [电子说] 为什么叫Bang-Bang鉴相器? 2023-09-20

- [电子说] 锁相环的基本组成、工作原理和应用电路 2023-08-19

- [电子说] 硬件锁相环电路设计步骤简介 2023-08-08

- [电子说] 什么是锁相环 锁相环的组成 锁相环选型原则有哪些呢? 2023-08-01

- [电子说] 锁相环的构成和工作原理讲解 2023-07-24

- [电子说] 系统的频域性能指标有哪些 频率合成器是如果影响系统指标的呢? 2023-07-14

- [电子说] 关于锁相环(PLL)的工作原理 2023-04-28

- [电子说] 有关鉴相器的基础知识介绍 2023-05-02

( 发表人:admin )