无线基础架构离散式SerDes解决方案 - 全文

高端智能型手机与其供应生态系统显现出一个事实:消费者需要的移动宽带及应用必须能协助他们紧密地链接信息、家人与好友。因此,移动宽带已成为现今电信产业成长最显著的部分。即使经济成长趋缓,电信业者近年来在无线数据方面的营收仍大幅增加。Netbook及HSDPA-USB接口连接装置的迅速成长也显示出消费者在任何地方都需要宽带,而不只限于住家及办公室内。

消费者使用移动装置存取数据时,仍会因为下载速度过慢及图形显示效果不佳而感到不便。视频博客及在线游戏等应用需要较快的连接速度及较短的延迟。更快速稳定的联机有助于云端运算相关应用的开发,而且移动办公室应用将不会因为硬件处理能力而受到限制。

在43亿的无线网络用户中,大约有80%是单纯使用语音的GSM用户。因此行动系统供货商十分看好未来5?10年吸引30亿的使用者申办移动宽带的成长商机。IPTV及数字相机等具有移动宽带连接功能且可实现新型服务的装置也可能带来如此的成长,进而提高移动通信商的收益。

为应对愈来愈多的需求并且提供更快更稳的联机及更短的延迟时间,全球网络业者希望能够建立4G网络,而LTE是全球这方面的首例。

● LTE规格可提供超过100Mbps的最高下行链路(下传)速率与超过50Mbps的上行链路(反传),以及往返延迟低于10ms的无线电存取网络(RAN)。

● LTE也运用波束形成(beam forming)等进阶天线技术概念来扩大涵盖范围。透过多层天线解决方案可达到高尖峰数据速率,例如,2×2或4×4多重输入与多重输出(MIMO)。

虽然出现了具备所有绝佳功能的新标准,无线及行动网络业者也必须持续面对投资成本及网络建置的挑战,以符合未来对于带宽的激增需求。网络业者必须针对4G选择最符合成本效益的网络演进。若要部署LTE等4G标准的网络,所需的网络升级不仅必须平衡新范围有限的可使用性,也必须运用于现有范围。为有效管理日益复杂的标准,分布式开放基站架构(Distributed open base station architecture)概念便随着这些标准应运而生,以提供低成本、弹性的模块化环境来管理无线电存取演进。

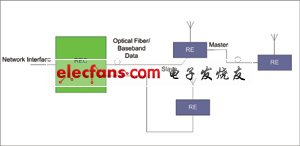

图1a显示的传统基站部署需要将无线电设备控制器(REC)及无线电设备(RE)连同天线塔放入单一机壳中。如此的做法会使网络业者在实际设置上面临体积尺寸增大、功耗提高及成本增加等不利因素。这类架构也会使连接天线与RE的电缆出现信号耗损的状况。

图1a 传统基站

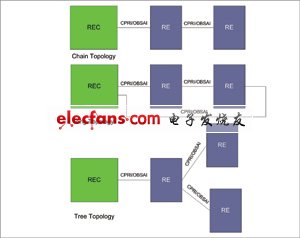

图1b至1c显示的分布式基站架构(DBSA)使得基站的其他部分完全不需要RF收发器。此架构能够使RE的位置更接近个别的天线,以便将图1b中介于RE与天线之间的电力损失减至最低,进而降低放大RF功率的成本。DBSA也允许各种不同的RE网络拓扑,例如,图1c所示的链状、环状或树状。如此的做法可确实缩小网络设置的规模,因为无线电设备可彼此连接,并不需各RE对单一REC进行通信。

图1b 分布式基站

图1c 分布式基站拓扑

开放式基站架构创始联盟(OBSAI)及通用公共射频接口(CPRI)标准适用于无线电设备控制器及无线电设备之间的基频数据通信,以及DBSA中的无线电设备网络。将REC与RE之间的接口标准化之后,不同厂商的REC及RE设备即可交互使用。同时,2G/3G/4G的REC 能够与不同的RE进行通信,因此可实现多种标准的结合与同时运作,并减少设备升级的需求。

CPRI及OBSAI均载明其无线电设备控制器及无线电设备之间的高速串行接口,以达到基频数据传输(I/Q数据),并且在相同接口进行指令/控制与同步(用于RE网络)信息的沟通。

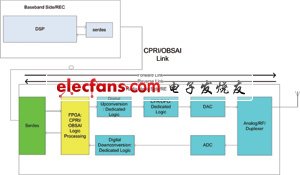

图2显示DBSA中的信号流向。对于上传(foward link)的RE,OBSAI/CPRI资料是由序列器/解除序列器(SerDes)所还原,其中会将高速序列数据转换为平行数据,然后将此数据传输至FPGA。FPGA会处理OBSAI/CPRI逻辑,然后将I/Q基频取样传输至数字升压转换器(专用逻辑),进而将I/Q基频取样调节至数位IF载波。经过向上转换的数据会接着经过数据处理引擎的处理,以减少波峰系数(专用逻辑),并且以数字方式将信号预失真(专用逻辑),以补偿功率放大器中产生的旁瓣(side lobe),并确保功率放大器能够在线性区域中运作。

图2 分布式基站架构信号流向

在上行链路中,无线射频模块包含所有的模拟功能,能够将RF频带向下转换为中频,然后以数字方式将个别载波向下转换为取样的基频同相及正交(I/Q)组。经过多任务处理的基频取样(I/Q)以及下传与反传中的控制及管理数据会被串行化,然后透过SerDes装置(例如,德州仪器的TLK3134)以光纤缆线进行传送。

若想借由分析4G演进方面的DBS以及所需突波来达到更快更稳定的数据联机,则会引起另一个重要问题。由于下行链路及上行链路的数据速率提升,而且愈来愈多的网络申办用户转而使用随选电视等高带宽应用,因此,REC与R之间的序列数据速率也随之增加。使用公式(1)可算出REC及RE之间的序列数据速率(SDR):

SDR=MAcSN2(I/Q)C (1)

其中,SDR是REC与RE之间的序列数据速率;M为天线数目;Ac为载波/天线数目;S为采样率(各载波每秒取样次数);N为取样宽度,位/取样;C为REC与RE之间串行传输期间的8b10b数据(10/8=1.25);2(I/Q)=2倍的同相及正交相位资料的倍增系数。

透过等式1及表1,对于4个W-CDMA载波、双天线系统,采样率为各载波每秒7.68百万次取样,I-Q取样宽度为 4b/sample的20MHz无线射频而言,其原始序列速率如式2所示:

SDR=2×4×7.68×4×2×1.25= 614.4Mbps (2)

同样地,透过式1及表1,对于四天线系统、单一载波/天线,LTE 载波采样率为各载波每秒30.72百万次取样,I-Q 数据取样宽度为16b/sample的20MHz无线射频而言,其原始序列速率如式3所示:

SDR=4×1×30.72×16×2×1.25=4.915Gbps (3)

对于八天线波束形成LTE系统而言,式3中的SDR会倍增为9.8Gbps。因此,I-Q取样宽度、信道宽度或天线载波数目的增加会直接造成REC与RE之间序列数据速率的提高。搭建基础架构的网络设备制造商应该要了解,在LTE演进中,序列数据速率必须从614.4Mbps的中等速率调整为9.8Gbps或12.2Gbps。DBSA的高SDR需要光纤缆线两端的SerDes发挥更高的效能,才能达到稳定的频率数据复原,并符合CPRI或OBSAI标准的抖动规格。为了进一步了解4G的SerDes及数据处理效用,以下将分析CPRI/OBSAI的通信协议堆栈。

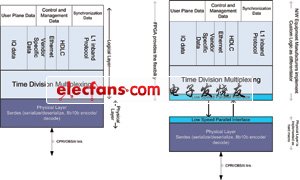

图3a显示CPRI通信协议层堆栈。一般而言,物理层包含不同通信协议都具备的固定功能。CPRI/OBSAI通信协议层的固定功能物理层是以硬件宏(hard marco)的方式进行实作,以达到严格的时序闭合需求。然而,逻辑层则允许客制化。由于新兴的标准演进,以及网络设备制造商期望透过专属功能建立附加价值,使得逻辑层会随之更新。在实作CPRI/OBSAI接口的逻辑层部份时,FPGA通常会提供所需的弹性。FPGA的逻辑项目能够利用程序加以设计,以支持自定义的逻辑层。

图3a CPRI通信协议层堆栈

图3b CPRI通信协议层堆栈(外部SerDes划分)

由于网络设备制造商改采4G部署,因此不仅需要相同弹性来实行逻辑层,也需要强化SerDes效能来满足增加的 SDR。网络设备制造商可选择采购已整合SerDes的FPGA,或选择采购FPGA与离散式SerDes,然后将两者结合(见图3b)。

以下是选择离散式SerDes-FPGA及整合型SerDes-FPGA时必须考虑的几项关键因素:

● 离散式SerDes加上FPGA的成本VS已整合SerDes的FPGA成本

● 离散式SerDes的效能VS整合于FPGA的SerDes效能

● 对于特定FPGA平台的熟悉程度

● 改用整合型SerDes-FPGA所节省的空间

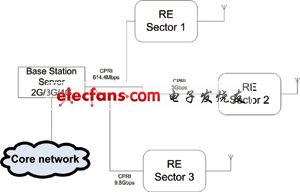

图4显示2G/3G/4G基站或REC连接到分别服务3个区块的3个RE。其中,3个CPRI设定分别为614.4Mbps、3Gbps及9.8Gbps线路速率,并假设9.8Gbps为更新过后的SDR,可支持4G。

图4 连接到3个RE的2G/3G/4G REC

状况A:假设网络设备制造商使用FPGA与离散式SerDes,而且已经在该特定FPGA平台的学习周期中投入时间与资源。若要在此状况下支持9.8Gbps:

● 制造商将SerDes升级,并持续使用同一个熟悉的FPGA平台。优点:达到规模效益,因为图4显示的3个RE区块都能具备类似的FPGA,同时以不同的SDR进行运作。如此一来,制造商便不需要变更FPGA平台而经历学习周期。

状况B:网络设备制造商使用已整合SerDes功能的经济型低阶FPGA。若要在此状况下支持9.8Gbps,制造商有3种选择:

● 改用不同制造商的9.8Gbps高阶FPGA(已整合SerDes)。缺点:成本增加,而且制造商必须经历新FPGA平台的学习周期。

● 改用相同制造商的低价9.8Gbps FPGA(已整合SerDes)。缺点:效能疑虑。

● 向同一个厂商购买不含SerDes的FPGA,并将系统切割为FPGA以及离散式SerDes。优点:制造商改用不含SerDes的FPGA可以节省成本,同时保留熟悉的FPGA平台。此外,使用相同的FPGA可切割出采用离散式SerDes的3个RE区块,进而达到规模效益,就如图4所示。缺点:离散式SerDes加FPGA的解决方案可能需要更多的PCB空间。

状况C:网络设备制造商使用已整合SerDes的高阶FPGA。若要在此状况下支持9.8Gbps,制造商有3种选择:

● 改用相同制造商的9.8Gbps FPGA(已整合SerDes)。缺点:制造商可能必须为具备9.8Gbps SerDes功能的FPGA付出相当高的成本。

● 改用不同制造商的9.8Gbps低阶FPGA(已整合SerDes)。缺点:学习周期、效能疑虑、缺乏降低成本的规模效益。

● 向同一个厂商购买不含SerDes的FPGA,并将系统切割为FPGA及离散式SerDes。优点:与状况B类似。

在9.8Gbps或12Gbps等高SDR的情况下,要满足离散式SerDes设计中对于稳定频率数据复原、抖动容差、信号调节及信号完整性的需求已经相当不容易,更不用说在整合型SerDes-FPGA设计中,数字逻辑项目区块(芯片的大部份)内敏感模拟电路的噪声隔离会造成设计上更大的挑战。有时候,为达到所需的效能,已整合SerDes的FPGA需要高成本的电源供应滤波,并选择使用电压控制的晶体振荡器或成本较低的晶体振荡器。这些需求会增加实施的成本。概括来说,将SerDes整合于FPGA会造成相关的成本,而且当整合难度因为SDR升高而增加时,这些成本也会增加。这正是为何当数据速率在3Gbps或更低的状况下,FPGA加离散式SerDes的解决方案比整合型解决方案更符合成本效益的一个主要原因。

结论

当网络设备制造商建置4G的基础架构时,对于分布式基站架构部署中无线电设备控制及无线电设备之间的高序列数据速率需求将大幅升高。要满足如此需求,光纤缆线两端的SerDeson必须发挥更高的效能。网络设备制造商可将系统切割开来,便能使用同一个熟悉的FPGA平台进行逻辑层处理。为达到高序列数据速率,网络设备制造商可改用离散式 SerDes 解决方案,单独就SerDes部份进行升级。如此的切分可达到所需的效能而不必采用新FPGA平台所需的学习周期,并且有助于提升规模效益,最终能降低制造商的成本。

- 第 1 页:无线基础架构离散式SerDes解决方案

- 第 2 页:分布式基站

- 第 3 页: CPRI通信协议层堆栈

本文导航

非常好我支持^.^

(4) 80%

不好我反对

(1) 20%

相关阅读:

- [移动通信] 5G 3GPP全球频谱介绍 2023-10-24

- [电子说] NB-IOT无线倾角传感器用于伊利智能货架安全监测的具体案例 2023-10-24

- [电子说] 环旭电子推出Pisces企业级无线路由器助力企业应对高密度数据挑战 2023-10-24

- [电子说] 首批高通骁龙8 Gen3旗舰入网 2023-10-24

- [RF/无线] 5G-A时代的室内网络建设解决方案 2023-10-24

- [电子说] 无线模拟信号采集器0-10v0-5v 4-20mA数据wifi通讯 2023-10-24

- [电子说] 物联网无线传感器节点可使用国产铁电存储器PB85RS2MC 2023-10-24

- [电子说] 御芯微亮相2023年世界物联网博览会 2023-10-24

( 发表人:叶子 )