L1实时软件子系统 - 基于DSP的3G LTE应用设计

L1实时软件子系统

飞思卡尔提供LTE L1支持软件库,包括一个定制操作系统、驱动器和主要信号处理功能。

LTE L1软件包括3GPP标准中定义的物理基带信道处理和无线传输信道功能。飞思卡尔提供一套综合的内核模块,覆盖物理下行链路共享信道和物理上行链路共享信道的L1处理。内核被进一步组合为上行链和下行链,它们以SmartDSP实时操作系统为参考实时运行。所有以上提到的软件在开发上都能使用ANSI-C语言调用,而且提供完整的开发文档。

简而言之,物理层处理功能包括:调制、信道编码、传输方案、复用、MIMO/分集、信道估测、均衡(3GPP范围之外)。

更多详细资料列举如下:

L1软件包包括

信号处理库:包含LTE L1信号处理管理器和内核库功能。这种信号处理内核是基本的处理单元,而信号处理管理器则是一系列内核的链路集成,包括DL传输信道包、DL物理信道包、UL传输信道包、UL物理信道包。

MATLAB模型包:用于生成测试矢量的已编译的Matlab参考链路。

多核MSC8156上的上行/下行链路功能集成(PDSCH/PUSCH):采用SmartDSP OS实时运行。

在一个典型 LTE 应用中使用 MSC8156

MSC8156 DSP支持广泛的配置组合。需考虑小区规模、上行和下行吞吐量、扇区数量、活跃/已连接用户数量、信号处理算法复杂度(MMSE、SIC等)、天线数量等参数,以决定器件数量和它们的分区。

一个典型的20MHz LTE FDD基站示例将表明一个完整的L1解决方案如何映射到MSC8156上。

典型的基站宏参数考虑如下:一个扇区;小区规模:10km;下行链路 4×4 MIMO;上行链路 2×4 MIMO;4 RX 天线、4 TX 天线;数据速率:下行链路290Mbps,上行链路120Mbps;应用上行链路的MMSE均衡器。

两个MSC8156 DSP实现对LTE物理信道的综合支持。一个器件负责所有上行链路处理,而另外一个被分配负责所有下行链路处理。

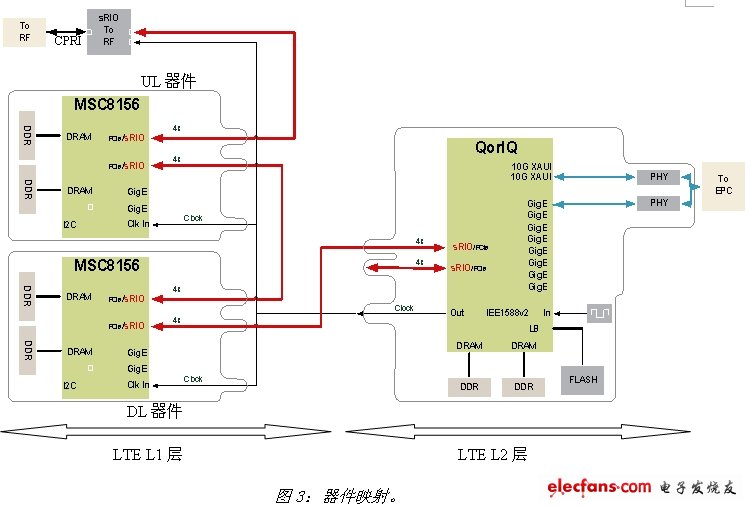

下图说明了器件映射的原理。

MSC8156可以通过PCI Express控制器、Gigabit以太网或sRIO连接器连接。sRIO链路以一种串行方式使用,被称为菊花链(daisy chaining)。这省去了对sRIO转换器的需求。

无线频率模块通过CPRI链路连接。一个小型FPGA器件负责从CPRI到sRIO的转换。这是系统中需要的唯一一个FPGA。然后就是链中的上行链路器件,接下来是下行链路器件。此器件被连接到L2器件,在这里被映射到一个QorIQ处理器上。

LTE信号处理任务可以在StarCore SC3850内核或MAPLE-B协处理器上执行。一个典型的分区如下所示:

上行链路器件:

3个内核用于共享信道

1个内核用于 随机接入信道(RACH)和声音

1个内核用于控制信道

最后一个内核用作主内核,在其他内核上安排和分配信号处理任务

下行链路器件:

3个内核用于共享信道

1个内核用于控制信道

1个内核用于物理广播信道(PBCH)、物理多播信道(PMCH)、物理控制格式指示信道(PCFICH)和物理HARQ指示符信道(PHICH)

最后一个内核作为任务调度器

下行链路器件的负载通常低于上行链路器件的负载。

下列表格详细列出了内核与MAPLE-B在功能上的分工。

通过这种方法,内核被专门用于预先确定的任务,但是如何分配任务则由调度器负责。为发挥器件能力以便实现1ms的时延要求,该模块具有很高的重要性。

例如,在上行链路器件上,当接收到参考信号的时候,信道估测将首选被分配到内核1、2和3上。然后,当接收到最后的数据符号的时候,可以在三个内核上安排均衡处理。接下来是解映射/解扰以及解交织。通常在空闲时隙安排测量。

上行链路器件利用所有的MAPLE-B处理部件,而下行链路器件仅将其用于最后的快速傅立叶反变换(IFFT)。对于更高的上行链路吞吐量,上行链路器件能够远程利用来自于下行链路器件的Turbo Viterbi处理部件(TVPE)。

- 第 1 页:基于DSP的3G LTE应用设计

- 第 2 页:L1实时软件子系统

本文导航

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

相关阅读:

- [移动通信] 5G 3GPP全球频谱介绍 2023-10-24

- [电子说] HOLTEK新推出BH66F2475连续血糖监测MCU 2023-10-24

- [处理器/DSP] 高通Hexagon NPU架构技术详解 2023-10-23

- [控制/MCU] Holtek新推出HT67F2452红外线驱动A/D与LCD型Flash MCU 2023-10-23

- [电子说] 车载DSP:新应用孕育国产“芯”机遇 2023-10-22

- [电子说] LightCounting复盘ECOC 2023:LPO热潮延续 2023-10-22

- [电子说] ADI ADAU1701DSP数字音频处理方案 2023-10-20

- [电子说] LTE系统TDD无线帧结构特点 2023-10-21

( 发表人:大本 )