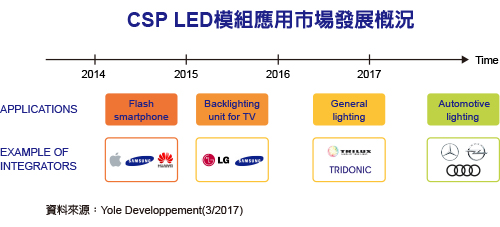

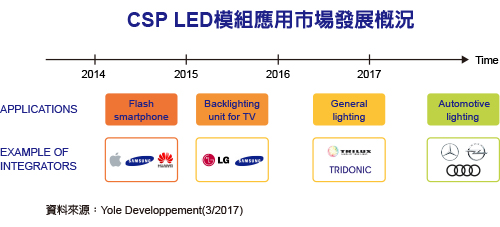

发光二极体(LED)封装厂在生态系统将日趋边缘化。上游LED晶粒厂为降低制造成本与微型化晶片尺寸,竞相展开晶粒尺寸封装(Chip Scale Package, CSP)技术布局,且该技术省略封装制程,遂让磊晶厂未来营运模式将跳过封装厂,直接与下游灯具系统商合作,导致封装厂在供应链的重要性大幅下降。

2014-05-06 09:03:50 1776

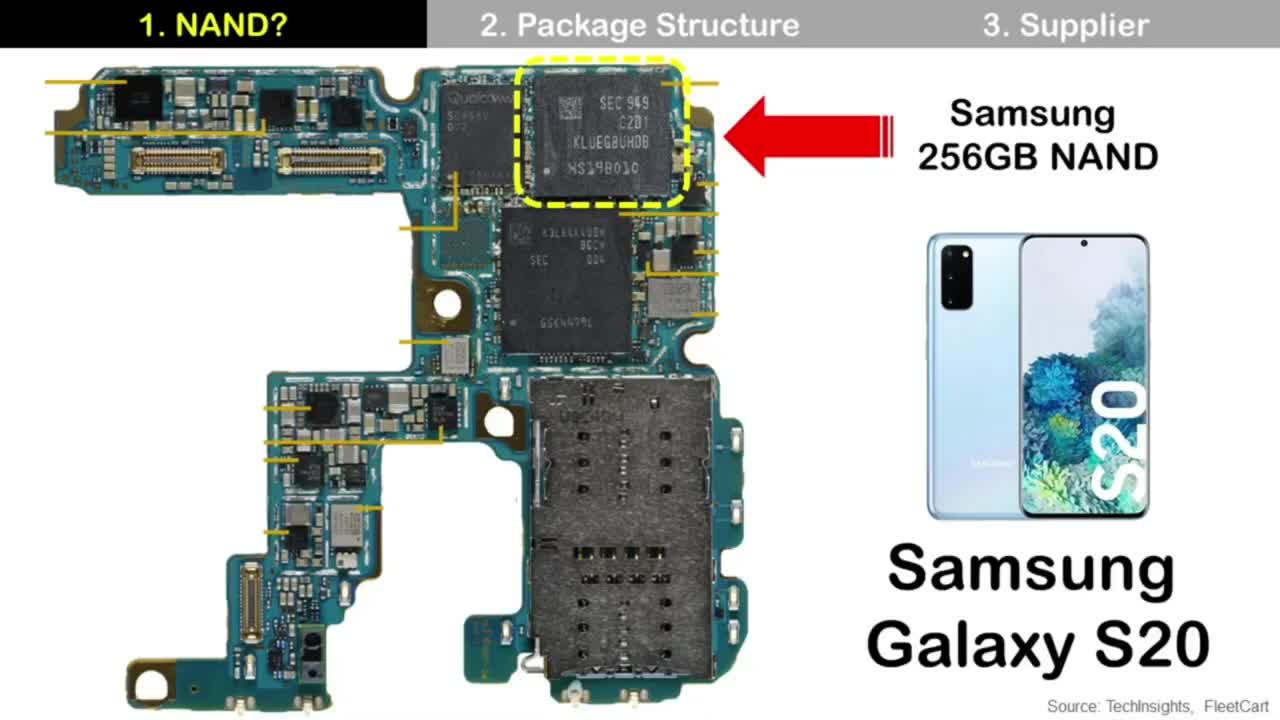

1776 LED封装技术出现新面孔。一般半导体厂商已经相当熟悉的芯片级封装(Chip Scale Package, CSP),正逐渐渗透到LED领域,如手机闪光灯与液晶电视背光用的LED皆已开始导入此一技术。

2017-03-27 09:32:36 2770

2770

1. BGA和CSP封装技术详解 2. 干货分享丨BGA开路金相切片分析 (BGA Open Cross-Section) 审核编辑:彭静

2022-07-26 14:43:18 5181

5181 请问大家,0.4pitch的CSP封装是怎么布线的,间距太小了

2016-06-29 21:36:01

在便携式、低引脚数和低功率产品中应用广泛,主要用于闪存、RAM、DRAM存储器等产品中。目前,超过100家公司开发CSP产品:Amkor、Tessera、Chip-scale、Sharp等,市场潜力巨大。

2020-03-18 09:01:54

csp模式不知道是哪里出现了问题?csp模式为什么不能让电机转起来?

2021-09-24 06:24:56

、无阻抗IC白/蓝膜片、长期高价求购封装测试厂淘汰的废旧QFN、PLCC、BGA、CSP、WL-CSP等各种封装后的IC芯片、Blue tape、chip、wafer.蓝膜片、白膜片、IC硅片、IC晶

2020-12-29 08:27:02

在电子产品开发的实践过程中,往往会碰到很多干扰方面的问题,这些问题对产品的可靠性和性能指标都会产生严重影响,同时需要大量时间和资源去进行排查修正,成为产品量产的瓶颈。在测试测量产品设计中,共地干扰就是较为常见的一类干扰。

2019-02-21 11:29:56

EtherCAT igh主站是如何控制松下伺服(csp模式)的?怎样去编写其代码?

2021-10-08 06:12:54

本帖最后由 eehome 于 2013-1-5 10:01 编辑

便携式应用本质存在空间限制,因此解决方案的大小至关重要。裸片可以最小化尺寸但是缺乏封装的诸多优势,如:保护、行业标准以及能够被

2011-06-16 16:12:03

初学者,请老师们帮忙解疑!PBGA,CSP,SOP分别是什么意思.

2013-01-17 16:52:09

SMT组件中时,技术遇到的困难最大。在一级封装组件应用中,倒装片广泛用于BGA和CSP,尽管BGA和CSP已经采用了引线-框架技术。在板级组装中,采用倒装片可以带来许多优点,包括组件尺寸减小、性能提高

2013-10-22 11:43:49

技术,由于减小板尺寸的市场需要,人们对0201元件十分关注。自从1999年中期0201元件推出,蜂窝电话制造商就把它们与CSP一起组装到电话中,印板尺寸由此至少减小一半。处理这类封装相当麻烦,要减少

2018-09-10 15:46:13

与CSP一起组装到电话中,印板尺寸由此至少减小一半。处理这类封装相当麻烦,要减少工艺后缺陷(如桥接和直立)的出现,焊盘尺寸最优化和元件间距是关键。只要设计合理,这些封装可以紧贴着放置,间距可小至150m

2010-12-24 15:51:40

小,击穿电压稳定,良率高,钳位 电压一般,电容有低容,普容和高容,6寸可以做回扫型ESD产品;第三代TVS主要以8寸晶圆流片为主,以CSP晶圆级封装为主(DFN),这种产品是高性能的ESD,采用8寸的先进

2020-07-30 14:40:36

适用于BGA,QFP,QFN.LGA.CSP,DIP.SOP,PLCC等一系列封装测试的一家微电子公司,主要用于芯片的不良产品的检测(开短路,电流等),兼容性检测,及芯片烧录资料,芯片老化,失效分析等一系列列的产品制作,联系人张生,***,微信1749001524

2016-11-21 13:31:44

1、准备工作:量产第一件事就是先用最新版芯片精灵(ChipGenius)检测自已U盘的主控型,做到心中有数,再根据上面的链接下载量产工具。再根据主控型号在站内搜索一下,多看几篇量产教程。做到

2013-06-24 10:54:51

`什么? 你对CSP的了解还不够?赶快来围观吧! 首先,得知道什么叫CSPCSP(Chip Scale Package),又称为芯片级封装器件, 其技术性主要体现为让芯片面积与封装面积之比超过1

2017-02-24 16:36:32

定义的CSP分类中。晶片级CSP是多种应用的一种低成本选择,这些应用包括EEPROM等引脚数量较少的器件,以及ASIC和微处理器。CSP采用晶片级封装(WLP)工艺加工,WLP的主要优点是所有装配

2018-08-27 15:45:31

单片机的中测和成测是指什么意思,封装的测试还是功能

2023-11-09 07:48:40

已经采用这些新的设计。一些半导体供应商采用CSP技术制造ASIP,从如何包装芯片的角度来看,CSP技术与传统的标准塑料封装技术不同。CSP技术不再需要传统塑封中芯片需要的引线框和包装芯片的塑料封装体

2018-11-23 16:58:54

和CSP也可达1000条。除了上述指标外,还有一个封装成本问题。一般讲,DIP、SOP价格最低,QFP较高,因而对于低、中引脚数的封装,它们是优先考虑的形式,当然它们的封装成本也还取决于引脚数的数目。TAB

2018-11-26 16:16:49

= 同一封装中集成的die数。以一个带有]为了提高良率,企业需要遵循两个原则:1、确定并且仅在封装中集成已知合格die]2、集成后,验证跨die的功能,以检测集成过程中的缺陷,以及其他难以通过测试单个die

2020-10-25 15:34:24

如果复制当前原理图1到原理图库2,新建的元器件能够复制,但是新器件的封装无法复制过去,即自己建的元器件封装却没有,这是为什么?如何在复制原理图时,在原理图2中复制过去的新器件封装也能复制过去(或自建的器件及封装都存在)?

2018-06-02 16:59:36

怎么选择晶圆级CSP装配工艺的锡膏?

2021-04-25 08:48:29

CSP具有更突出的优点:①近似芯片尺寸的超小型封装;②保护裸芯片;③电、热性优良;④封装密度高;⑤便于测试和老化;⑥便于焊接、安装和修整更换。因此,九十年代中期得到大跨度的发展,每年增长一倍左右。由于

2018-09-12 15:15:28

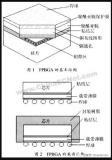

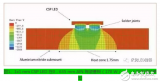

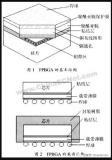

引言 无引线导线封装(LLP)是一种基于导线架的晶片级封装(CSP),它可以提高芯片的速度、降低热阻并减小贴装芯片所需要的PCB面积。由于这种封装的尺寸小、高度很低,所以此封装是高密度PCB

2018-09-10 16:37:26

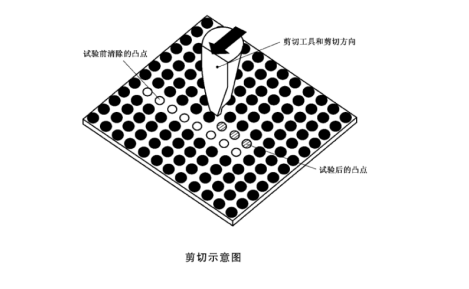

晶圆级CSP的返修工艺包括哪几个步骤?晶圆级CSP对返修设备的要求是什么?

2021-04-25 08:33:16

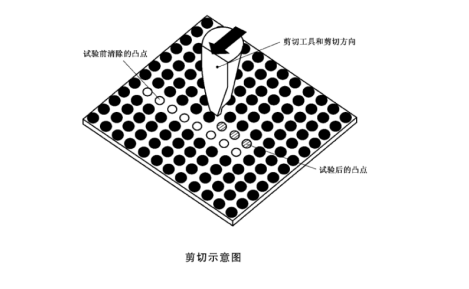

细间距的晶圆级CSP时,将其当做倒装晶片并采用助焊剂浸蘸的方法进行组装,以取代传统的焊膏印刷组装,如图2所示,首先将晶圆级CSP浸蘸在设定厚度的助焊剂薄膜中,然后贴装,再回流焊接,最后底部填充(如果有要求)。关于锡膏装配和助焊剂装配的优缺点。图1 工艺流程1——锡膏装配图2 工艺流程2——助焊剂装配

2018-09-06 16:24:04

等。这些测试在一般的工厂内很难完成,这里推荐一些较简单且容易在工厂完成的 简易评估方法: ①正常情况下印刷结果检查——可以选择含0201/BGA/CSP/QFP等元件的印刷电路板,连续印刷10块板

2018-11-22 16:27:28

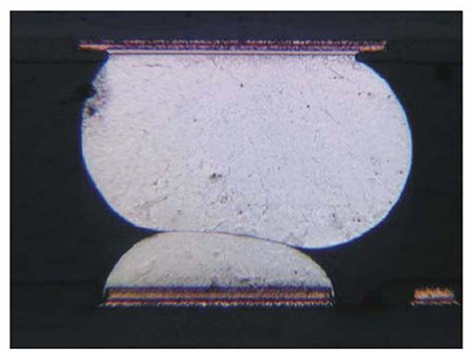

人们对一些应用在手持设各如手机和数码相机等上的CSP的机械连接强度和热循环可靠性非常关注。由于 组件中的各种材料的热膨胀系数不匹配,轻微的热变形就会导致应力存在于细小的焊点中。为了改善这种现 象

2018-09-06 16:40:03

晶圆级CSP的装配对贴装压力控制、贴装精度及稳定性、照相机和影像处理技术、吸嘴的选择、助焊剂应 用单元和供料器,以及板支撑及定位系统的要求类似倒装晶片对设备的要求。WLCSP贴装工艺的控制可以参

2018-09-06 16:32:18

和热循环测试,以及机械测试(推拉,跌落,振动,扭转和弯曲)等。例如,可以用X-Ray检查返修前后 焊点的情况,是否短路,在焊点内是否有空洞存在等。如图1所示。图1 X-Ray检查返修前后的焊点

2018-09-06 16:39:59

经底部填充的CSP装配,其稳健的机械连接强度得到很大的提升。在二级装配中,由于底部填充,其抵御 由于扭转、振动和热疲劳应力的能力得以加强。但经过底部填充的CSP如何进行返修成了我们面临

2018-09-06 16:32:17

。由于CSP具有更突出的优点:①近似芯片尺寸的超小型封装;②保护裸芯片;③电、热性优良;④封装密度高;⑤便于测试和老化;⑥便于焊接、安装和修整更换。因此,九十年代中期得到大跨度的发展,每年增长一倍左右

2023-12-11 01:02:56

芯片封装测试流程详解ppt•按封装外型可分为:SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;• 决定封装形式的两个关键因素:Ø封装效率。芯片面积/封装面积,尽量接近1:1

2012-01-13 11:46:32

问题,CSP不但具有裸芯片的优点,还可像普通芯 片一样进行测试老化筛选,使MCM的成品率具有保证,大大促进了MCM的发展和推广应用。目前MCM已经成功地用于大型通用计算机和超级巨型机中,今后将用于工作站

2018-11-23 16:59:52

请问ADN4670BCPZ焊接温度曲线有么?以及这种CSP封装的焊接需要注意的事项有哪些?

2019-01-18 16:44:20

安卓开饭量产测试是有专门测试程序么?像firefly和友善的RK开发板都有特别多的接口,还有的带屏幕各种传感器,那么量产的时候要如何测试呢?是专门的测试工具和测试程么,那么多的接口一个个手工测是不是太慢?

2019-04-01 03:47:10

由于叠层CSP封装的复杂性,其振动特性很难用精确的理论模型表示。同时,由于传统的共振准则没有考虑到系统的变异性和模糊性,导致分析结果与真值具有较大偏差。该文利用

2009-02-27 15:37:11 9

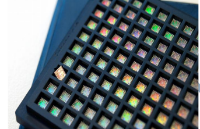

9 CSP產品簡介封裝完成後之面積(Footprint)約為晶片(Die)之1.2倍依其結構可分為四類Flex Circuit InterposerRigid Substrate InterposerLead Frame (Lead-on-Chip)Wafer Level Assembly可靠度簡

2009-07-06 09:28:14 12

12 基于进程代数的CSP 方法是一种重要的形式化协议分析验证方法。本文首先简单介绍了CSP 相关理论,并以NSPK 协议为例系统概述了安全协议的CSP 建模方法。为更好的查明协议的安全缺

2009-08-06 11:22:16 12

12 可以解决众多封装难题的CSP-ASIP

无线手持设备、掌上电脑以及其他移动电子设备的增加导致了消费者对各种小外形、特征丰富产品的需要。为了满足越来越小的器件同时具有

2009-03-28 17:02:02 927

927 摘要:本文详细讨论了Maxim的晶片级封装(WL-CSP),其中包括:晶圆架构、卷带包装、PCB布局、安装及回流焊等问题。本文还按照IPC和JEDEC标准提供了可靠性测试数据。 注

2009-04-21 11:30:27 8552

8552

SMT最新技术之CSP及无铅技术

CSP、0201无源元件、无铅焊接和光电子,可以说是近来许多公司在PCB上实践和积极*价的热门先进技术。

2009-11-16 16:41:10 1405

1405 晶圆级CSP的返修工艺

经底部填充的CSP装配,其稳健的机械连接强度得到很大的提升。在二级装配中,由于底部填充,其抵御 由于

2009-11-20 15:42:17 483

483 晶圆级CSP的装配工艺流程

目前有两种典型的工艺流程,一种是考虑与其他元件的SMT配,首先是锡膏印刷,然后贴装CSP,回流焊接

2009-11-20 15:44:59 1348

1348 半加成法SAP于载板之量产

当线宽线距小于50μm(2mil)者,传统CCL的减成法几已无用武之地。而目前CSP或FC覆晶等载板的Line/Width已逼近到了15μm/15μm

2009-12-22 09:29:33 18193

18193 CSP封装内存

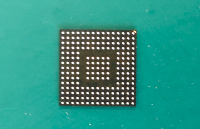

CSP(Chip Scale Package),是芯片级封装的意思。CSP封装最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封装可以让芯片面积与封装面积之比超

2009-12-25 14:24:49 636

636 高级封装,高级封装是什么意思

晶片级封装CSP(Chip Scale Package)。几年之前以上所有的封装其封装本体面积与芯片面积之比通常都是

2010-03-04 11:13:29 1420

1420 什么是CSP封装

近几年的硬件发展是日新月异,处理器已经进入G赫兹时代,封装形式也是经历了数种变化。不过,光有一颗速急力猛的芯还远远不够

2010-03-04 11:43:25 14777

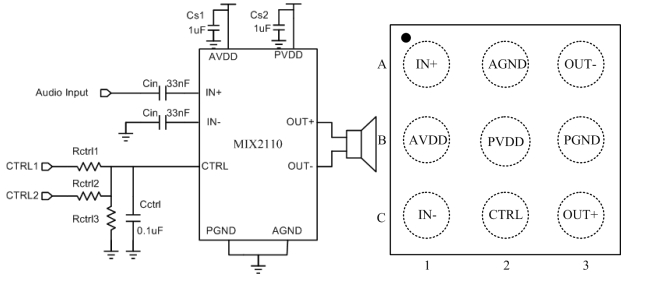

14777 上海矽诺微电子针对目前的便携式市场推出全系列兼容的CSP-9封装的D类音频功放。该系列产品目前有三颗,分别是MIX

2011-01-11 09:15:17 1444

1444

2007年由飞利浦Lumileds推出的CSP技术,历经五六年的沉寂,从2013年起渐渐被业界提及,去年开始更是频频登上各大展会和论坛。台湾新世纪光电更预测CSP具备单位亮度更高,厚度更薄及成本低

2016-05-12 16:29:52 2687

2687

OV2715_CSP3_Datasheet

2016-12-25 23:00:49 4

4 芯片级封装介绍本应用笔记提供指引使用与PCB安装设备相关的芯片级封装。包括系统的PCB布局信息制造业工程师和制造工艺工艺工程师。 包概述 倒装芯片CSP的包概述半导体封装提供的芯片级封装代表最小

2017-03-31 10:57:32 45

45 超级CSP——让倒装芯片获得最大可靠性一种晶圆片级封装

2017-09-14 11:31:37 22

22 CSP封装的芯片测试,由于其封装较小,采用普通的机械手测试无法实现,目前主要采用类似晶圆测试的方法,在芯片完成置球封装后,先不做划片,而直接用探针卡进行测试,测试完成后,再实行划片、分选和包装。

2017-10-27 15:11:10 7297

7297 模型检测是通信顺序进程(communicatmg sequential processes,简称CSP)形式化验证的重要手段.当前,CSP模型检测方法基于操作语义,需将进程转化为迁移系统,进而

2018-01-23 16:03:53 1

1 CSP(chip scale package)封装是指一种封装自身的体积大小不超过芯片自身大小的20%的封装技术(下一代技术为衬底级别封装,其封装大小与芯片相同)。为了达成这一目的,LED制造商

2018-06-07 15:40:00 945

945

近几年大陆背光产品价格持续下滑,亿光等LED厂商在背光市场出货比重仍不低,为避开陆厂价格竞争,今年亿光将以mini LED、CSP封装产品抢攻高端背光应用。

2018-04-27 11:20:00 2560

2560 目前CSP LED的主流结构可分为有基板和无基板,也可分为五面发光与单面发光。所说的基板自然可以视为一种支架。很显然,为了满足CSP对封装尺寸的要求,传统的支架,如2835,的确不能使用,但并不

2018-07-12 14:34:00 10628

10628 CSP(chip scale package)封装是指一种封装自身的体积大小不超过芯片自身大小的20%的封装技术(下一代技术为衬底级别封装,其封装大小与芯片相同)。为了达成这一目的,制造商尽可能

2018-08-10 15:43:52 14433

14433 CSP(Chip Scale Package)封装,是芯片级封装的意思。CSP封装最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封CSP封装装可以让芯片面积与封装面积之比超过

2018-08-17 15:25:38 18203

18203 CSP(chip scale package)封装是指一种封装自身的体积大小不超过芯片自身大小的20%的封装技(下一代技术为衬底级别封装,其封装大小与芯片相同)。

2018-09-05 08:36:00 13375

13375 CSP封装是最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,绝对尺寸也仅有32平方毫米,约为普通的BGA的1/3,仅仅相当于TSOP内存芯片面积的1/6。与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。

2019-06-24 14:12:36 19779

19779 11月19日消息,据报道,台积电与Google等美国客户正在一同测试,合作开发先进3D堆栈晶圆级封装产品,并计划2022年进入量产。台积电将此3D堆栈技术命名为“SoIC封装”,可以垂直与水平的进行芯片链接及堆栈封装。

2020-11-20 10:56:30 2161

2161 电子发烧友网为你提供TE(ti)CAT-CSP-5T相关产品参数、数据手册,更有CAT-CSP-5T的引脚图、接线图、封装手册、中文资料、英文资料,CAT-CSP-5T真值表,CAT-CSP-5T管脚等资料,希望可以帮助到广大的电子工程师们。

2021-07-08 21:00:04

接近为1,而且电器性能以及可靠性也有大幅提升。正因于此,CSP封装不断渗透更多的应用市场,并且还在不断扩大,而与此同时,与其相关的测试技术也在迅速发展。 CSP封装的芯片测试,由于其封装较小,无法采用普通的机械手测试实现,只有通过

2021-12-03 13:58:36 2405

2405 先进封装形式μBGA、CSP的回流焊接技术介绍说明。

2022-05-06 15:17:46 4

4 倒装芯片 CSP 封装

2022-11-14 21:07:58 19

19 CSP封装(Chip Scale Package)是指芯片级封装,其封装尺寸和芯片核心尺寸基本相同,一般芯片面积与封装面积的比例约在1:1.1。CSP封装最先规模应用在消费电子和个人电脑,与我们的生活息息相关。

2023-03-28 14:52:09 10625

10625 CSP2510C 数据表

2023-04-26 19:29:44 1

1 CSP(Chip Scale Package)封装芯片是一种高密度、小尺寸的封装形式,它在集成电路行业中具有广泛的应用。对于CSP封装芯片的测试方法而言,主要涉及到以下几个方面:

2023-06-03 10:58:16 1142

1142 光电传感器WL-CSP封装芯片底部填充胶应用由汉思新材料提供光电传感器芯片(CCD)经过联系客户工程技术和研究其提供的封装工艺流程。了解到以下信息。客户用胶项目是:光电传感器芯片(CCD

2023-05-18 05:00:00 546

546

电子封装是现代电子产品中不可或缺的一部分,它将电子元件组装在一起,形成了一个完整的电子系统。其中,BGA和CSP是两种常见的电子封装技术,它们各有优缺点,广泛应用于半导体制造、LCD显示器等领域

2023-06-14 09:11:18 850

850

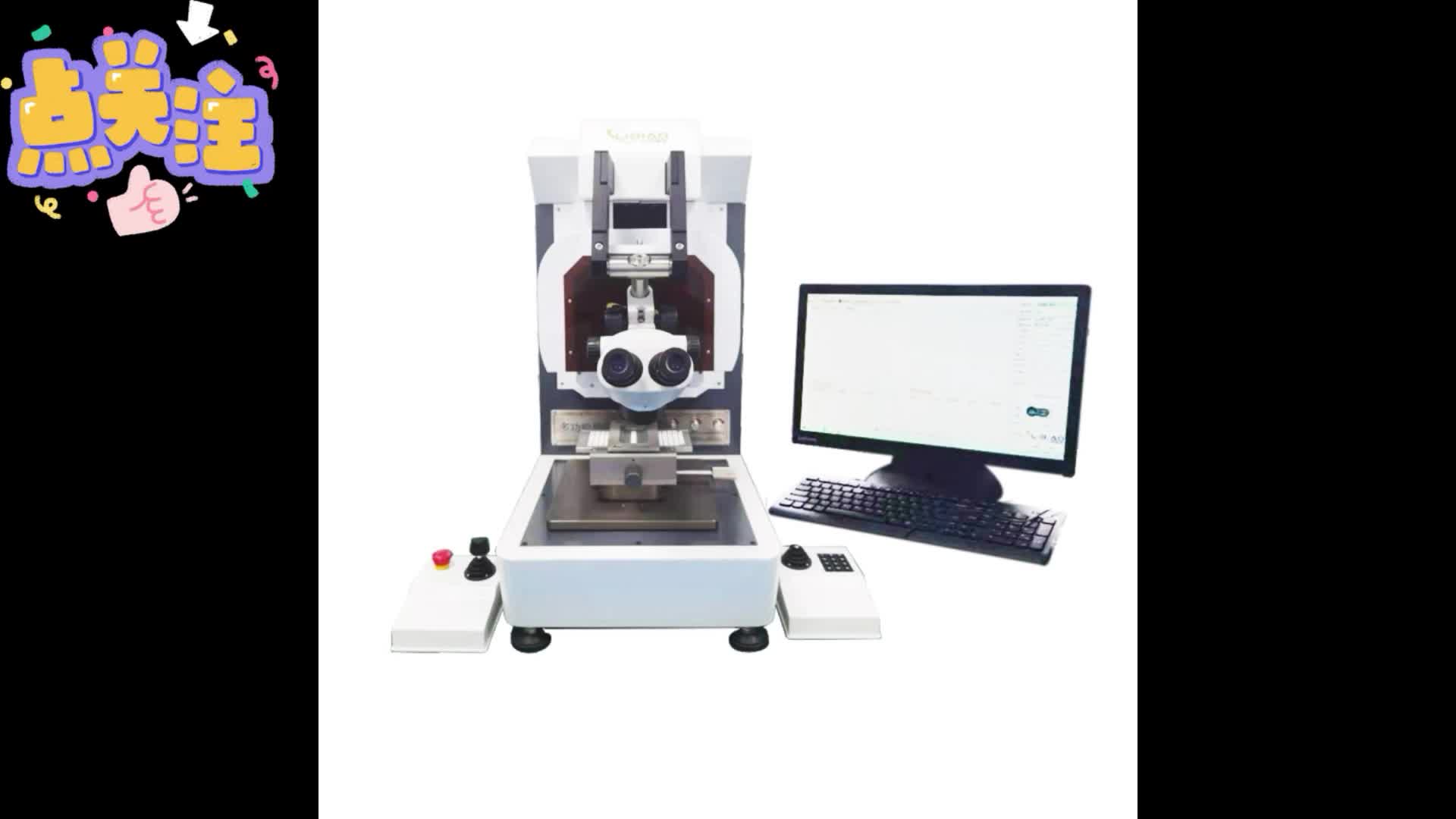

包括球栅阵列封装(BGA)、无引线封装(QFN)、芯片级封装(CSP)等。 本文科准测控的小编将介绍半导体封装推拉力测试机的技术参数和应用范围,并探讨其在BGA封装测试中的重要性。 一、测试内容 引脚连接强度:测试封装器件引脚与

2023-06-26 10:07:59 581

581

短1/5~1/6左右,同时CSP的抗噪能力强,开关噪声只有DIP(双列直插式封装)的1/2。这些主要电学性能指标已经接近裸芯片的水平,在时钟频率己超过双G的高速通信领域,LSI芯片的CSP将是十分理想的选择。

2023-08-20 09:42:07 1110

1110

芯片封装测试有技术含量吗?封装测试是干嘛的? 芯片封装测试是指针对生产出来的芯片进行封装,并且对封装出来的芯片进行各种类型的测试。封装测试是芯片生产过程中非常关键的一环,而且也需要高度的技术含量

2023-08-24 10:41:57 2322

2322 晶圆封装测试什么意思? 晶圆封装测试是指对半导体芯片(晶圆)进行封装组装后,进行电性能测试和可靠性测试的过程。晶圆封装测试是半导体芯片制造过程中非常重要的一步,它可以保证芯片质量,并确保生产出的芯片

2023-08-24 10:42:07 1311

1311 CSP是近几年才出现的一种集成电路的封装形式,目前已有上百种CSP产品,并且还在不断出现一些新的品种。尽管如此,CSP技术还是处于发展的初期阶段,因此还没有形成统一的标准。不同的厂家生产不同的CSP

2023-09-08 14:09:40 294

294 BGA和CSP封装技术详解

2023-09-20 09:20:14 951

951

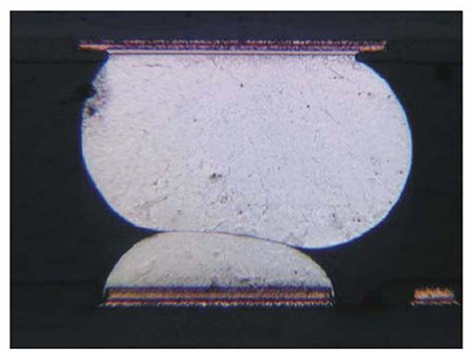

简要解读BGA、CSP封装中的球窝缺陷

2023-10-08 08:47:53 339

339

CSP的高效优点体现在:用于板级组装时,能够跨出细间距(细至0.075mm)周边封装的界限,进入较大间距(1,0.8,0.75,0.5,0.4mm)区域阵列结构。 已有许多CSP器件在消费类电信领域

2023-10-17 14:58:21 321

321 2023年10月18日,昆山同兴达芯片和金凸块全过程的封装测试项目量产仪式在昆山隆重举行,下游客户包括奕力科技股份有限公司的ic设计等世界级大工厂莅临参加,标志同兴达先进封装测试项目大规模量产化和市场化与上游公司的合作模式,进一步深化。

2023-10-20 09:46:43 507

507 为了实现集成电路芯片的电通路,一般需要将芯片装配到在塑料或陶瓷载体上,这一过程可以称为CSP。CSP的尺寸只是略大于芯片,通常封装尺寸不大于芯片面积的1.5倍或不大于芯片宽度或长度的 1.2

2023-12-22 09:08:31 535

535

提及CSP封装基板领域,兴森科技目前每月的产量约为3.5万平方米,其中广州基地生产能力达到了2万平方米/月,已处于饱和状态;而广州兴科与珠海基地的产能分别为1.5万平方米/月,且利用率都超过了50%。

2024-01-30 09:59:33 260

260 立錡推出的低压输入、CSP 小封装降压转换器系列,不仅满足各式小型穿戴式和 IoT 物联网应用的需求,更在性能和尺寸上取得了绝佳平衡。

2024-03-14 15:03:10 192

192

电子发烧友App

电子发烧友App

评论