ADI公司的ADUX1020是集成了14位模数转换器(ADC)和20位突发累加器的高效率光度传感器,采用单点检测改善了应用的可靠性,同时所需元件数更低,因而为系统开发人员降低了设计复杂性和成本;同时

2016-10-18 13:59:59 1801

1801

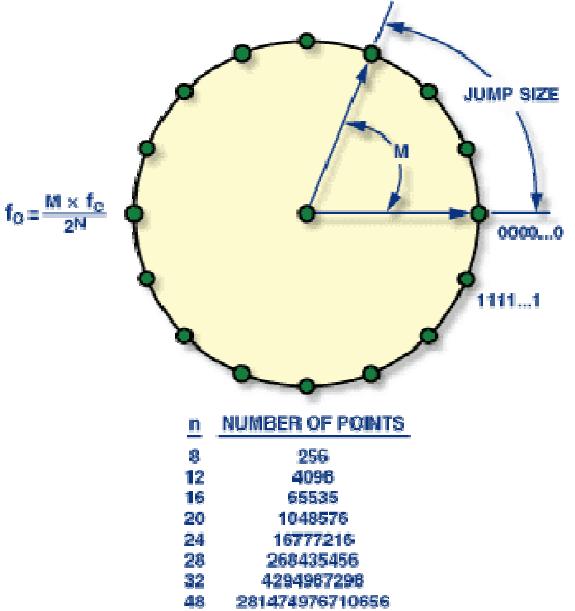

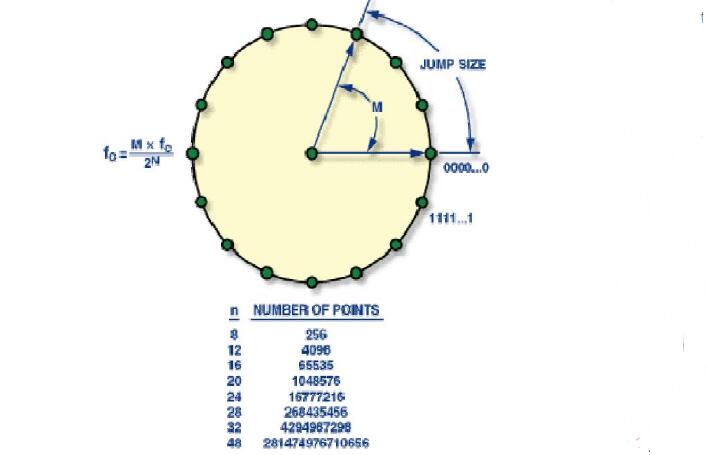

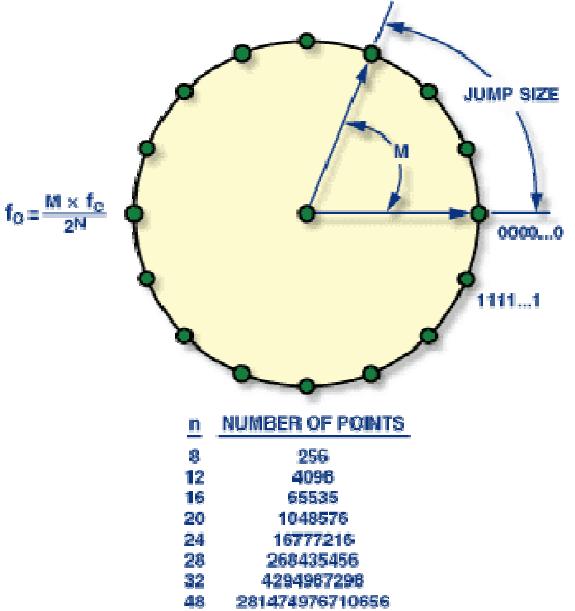

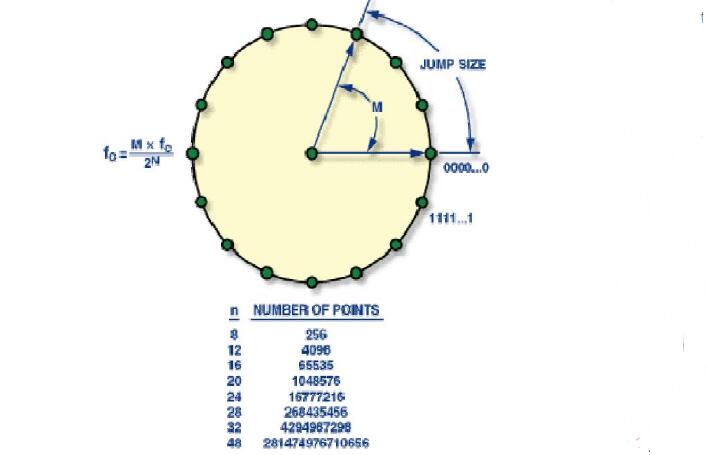

发生器中有极其重要的应用。DDS主要由以下几部分组成: a) 相位累加器 b) RAM数据读取 c) D/A转换器 d) 低通滤波器 直接频率合成法的流程图,有固定模块,输入频率控制器,输出固定频率的波形。如下图: 此电路最主要模块是相位累加器,通过相位累加器循环计

2020-11-29 10:19:00 4144

4144 51单片机只有对累加器操作的指令会影响Z(结果为零)标志吗?如果不是对累加器A的操作如decRn,对z标志没有影响吗?

2016-07-23 11:39:50

51单片机怎么用汇编语言把累加器A中的数据移入到P0.0中,不影响p0口其他的口

2016-01-13 20:46:30

的数据送入累加器112MOVA,#data88位立即数送入累加器212MOVRn,A累加器内容送入寄存器112MOVRn,direct直接地址单元中的数据送入寄存器224MOVRn,#data88位

2012-06-08 14:56:14

写,分别为:加:MAIN:ANL A,#0FH ;屏蔽累加器的高4位MOV DPTR,#TAB;将数据表格的首地址 0100H存入16位的数据地址指针DPTR中MOVC A,@A+DPTR;查表MOV

2014-11-26 21:57:09

直接地址单元中。 ANL A,@Ri ;累加器A的内容和工作寄存器Ri指向的地址单元中的内容执行与逻辑操作。结果存在累加器A中。 [6]. 逻辑或操作指令(6条) 这组指令的作用是将两个单元中的内容执行

2014-10-03 10:49:33

助记符操作数指令说明字节数周期数 (数据传递类指令) MOVA,Rn寄存器传送到累加器11 MOVA,direct直接地址传送到累加器21 MOVA,@Ri累加器传送到外部RAM(8 地址)11 MOVA,#data立即数传送到累加器21 MOVRn,A累加器传送到寄存器

2021-11-18 08:34:42

影响标志位的寄存器的是不是只要有累加器的参与就可以影响标志位吗?? 还是其他的寄存器也可以影响标志位呢

2015-12-02 23:01:51

,每满15个gary_value输出一个累加结果,同时累加器清零。我写的代码如下:module accumulator (clk, rst_n,a_en,gary_value,accumulation

2015-05-23 20:09:34

累加器使用的注意点及自定义累加器

2020-04-02 09:31:37

成就更好的自己AT89S51的CPU由运算器和控制器构成;一.运算器算数逻辑运算单元ALUALU功能强大,可以进行各种数学运算和逻辑运算,此外还具有位操作功能;累加器A累加器A在特殊功能寄存器区

2021-12-01 07:52:08

您好,我在ASM中开发了一个小代码,用于更快的执行,但我没有设法阻塞累加器。下面的代码给了我编译的错误:所以我试图简化情况,我做了这个简单的代码:这给了我编译的错误:我在寻找答案。在互联网上很长

2018-11-23 15:16:49

设计时没有加入溢出清零的进程。频率累加字不断累加到最后应该是大于2的n方减1,溢出后应该要清零重新加吧。可是我没有加入这个进程,modelsim仿出的波形毫无问题。请问这是为什么呢?难道不要清零吗?可这样加下去不会超出量程,越来越大?

2014-06-30 22:14:54

E1332A 4通道计数器/累加器模块服务手册

2019-10-12 10:32:28

E1332A 4通道计数器/累加器模块用户手册

2019-09-29 11:08:55

EPWM_EnableAcc(EPWM1, 0, 10, EPWM_IFA_ZERO_POINT);

这个是控制自动产生10个累加器然后自动关闭PWM输出吗?

void

2024-01-15 07:31:58

EVAL-AD9834EBZ,AD9834直接数字频率合成器(DDS)评估板。 AD9834是一款数字控制振荡器,采用相位累加器,正弦查找表和10位DAC。 AD9834的时钟频率最高可达75

2019-08-08 08:52:02

的输出和查找表地址有什么关系,资料里说高M位进行寻址是怎么回事?Q2: 相位累加器溢出一次的累加次数就是NCO的周期,上面例子中累加次数为16,要把正弦表256个点寻址时addr = addr + 16

2016-03-10 20:10:36

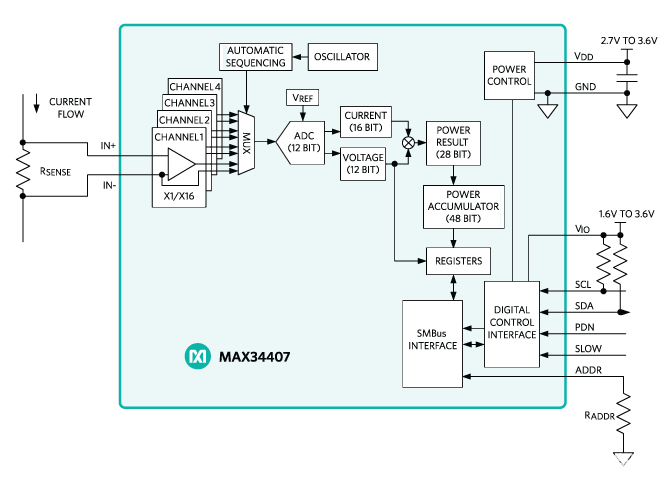

`★M0累加器(Accumulators)◆ ADC 后方配置三组硬件累加器(Accumulators)◇模式一:三组累加器可同时提供个别三组ADC的累加计算◇模式二:单一累加器可累加多组ADC资料

2020-03-27 15:42:01

,它变得稳定,大约30秒后它又变得不稳定,然后开始另一个30秒的循环。在规模的中心附近,它保持不稳定。因此,我试着使用16b未分配和15b有符号输入,关闭中断,查找累加器溢出,改变输出缩放,改变K1

2020-04-08 07:18:26

初始值init初始化累加器acc,然后用acc = acc修改它来完成的+ *i或acc = binary_op(acc, *i)按顺序在[first, last]范围内的每个迭代器i。如果序列为空,Accumulate返回init。Binary_op不应该有副作用。

2023-08-08 07:54:13

用流水线技术设计相位累加器,时序上可以工作在更高工作频率,但需要n个周期才能到达反馈(假设是n级流水线),也就是说实际相位输出频率是clk/n ,还是没有提高采样频率不是吗,怎么改进呢

2019-04-21 22:58:11

本帖最后由 区幺幺 于 2020-6-30 21:24 编辑

照大佬给的答案在累加器代码里增加了对y_out,y_ou的初始化[code]always @(posedge res or posedge clk)beginif (res == 1'b1)beginyoutput

2020-06-28 11:33:51

,#data立即数传送到累加器21 MOVRn,A累加器传送到寄存器11 MOVRn,direct直接地址传送到寄存器22 MOVRn,#data累加器传送到直接地址21 MOVdirect,Rn

2011-11-28 10:49:01

为什么rom送片外ram需要累加器清零呢?是何原因?请问一下大神

2023-03-28 11:35:57

主要有内部RAM区和特殊功能寄存器SFR区。例如,指令MOV A,3AH执行的操作是将内部RAM 中地址为3AH的单元内容传送到累加器A中,其操作数3AH就是存放数据的单元地址,因此该指令是直接寻址

2016-01-13 14:54:46

联合文件“模拟乘法累加器”中找到: - 我输入的IP参数 - 我获得的结果谢谢你的帮助!乘法累加器的模拟.doc 140 KB

2019-10-25 09:44:50

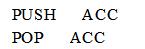

累加器A与ACC区别累加器写成A或ACC在51汇编语言指令中是有区别的。ACC在汇编后的机器码必有一个字节的操作数,即累加器的字节地址E0H,A在汇编后则隐含在指令操作码中。所以在指令中A不能

2012-10-16 20:38:20

结果存入寄存器中;控制器由程序计数器、指令寄存器、指令译码器、时序发生器和操作控制器等构成,是一个下达命令的“组织”,用于协调整个系统各部分之间的运作;寄存器主要有累加器A、数据寄存器DR、指令寄存器

2021-12-01 06:18:25

,与外部存储器RAM打交道的只能是A累加器。所有需要传送入外部RAM的数据必需要通过A送去,而所有要读入的外部RAM中的数据也必需通过A读入。在此我们能看出内外部RAM的区别了,内部RAM间能直接进行数...

2021-12-03 06:45:00

AW60CPU寄存器包括一个8位的累加器A、一个16位的变址寄存器H:X、一个16位的堆栈指示器SP、一个16位的程序计数器PC和一个8位的条件码寄存器CCR。累加器A(Accumulator):8位通用寄存器

2018-10-22 14:53:00

你好,有没有任何形式可以像累加器那样使用计数器?我想使用一个计数器,因为它的资源使用率要低得多。例如,纹波计数器可能有效,但我需要在每个时钟周期有一个可变数量的脉冲,具体取决于要与前一个值相加的数字

2019-01-16 10:55:22

嗨,我做这个累加器加法器:库IEEE;使用IEEE.STD_LOGIC_1164.ALL;使用IEEE.STD_LOGIC_ARITH.ALL

2019-01-22 06:20:50

在我的Quartus13.0和13.1的MegaWizard Plug In Manager里找不到altaccumulate这个累加器IP?搜索安装文件夹有相关文件,你们的Quartus13有这个IP吗?

2016-05-17 15:51:32

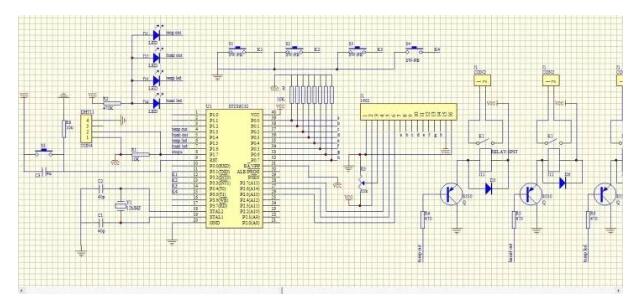

求一个基于FPGA的DDS信号发生器设计,最好有DA模块和相位累加器模块的代码。

2019-03-18 22:09:03

;***itSDI=P1^5; //定义数据输入端口 ***itCLK=P1^7; //定义时钟端口 ***itACC7=ACC^7;//定义累加器A的第8位 ***itACC0=ACC^0;//定义累加器A

2014-09-30 22:29:00

在合泰单片机中 怎么实现对累加器ACC的位操作 求各位大神帮忙给个范例 谢啦

2014-03-25 23:35:21

更慢。累加器的作用在运算器中,累加器是专门存放算术或逻辑运算的一个操作数和运算结果的寄存器。能进行加、减、读出、移位、循环移位和求补等操作。是运算器的主要部分。在中央处理器 CPU 中,累加器

2020-10-14 07:18:39

,执行该条指令后,R7中的数据会送到累加器A中,累加器A中的数据就变为10101001。 寄存器寻址 4寄存器间接寻址是在指令的操作码后给出寄存器,该寄存器中存储的不是数据,而是一个地址

2021-01-20 15:33:50

增加到25 V。 此电源电压范围与L99ASC03内部+ 5V稳压器限制相匹配,但在使用许多LiPo时可能会浪费太多功率。 当VS和VSMS直接连接到LiPo累加器时,是否可以将开关稳压器的+ 5V输出

2019-02-26 16:00:34

请问怎样利用ADuC7060的累加器和计数器来计算平均值?如何配置?当ADC0RCR = ADC0RCV时会产生中断,那请问这是什么中断类型?在哪里配置?

请问“和ADC0RCR配合使用,可屏蔽主通道ADC中断,从而产生较低的中断速率”怎么理解?我怎样才能配合ADc0ACC进行平均值的计算?

2024-01-15 06:18:12

怎么由布尔控件控制开始和停止累加器的运行

2019-06-04 22:09:14

就是那个用移位寄存器和全加器组合做的累加器。。。相关理论还没学,看书看不懂,想不出来了。。。求助啊。。。

2012-11-07 21:44:16

各位大佬,请问图中两个列子中累加器B的结果是怎么计算出来的?

2021-10-22 22:35:01

本帖最后由 eehome 于 2013-1-5 10:06 编辑

我是新手求助pic12f629单片机如何运用累加器溢出,设置按键开关档位,按一下。使I/O口输出高电平,求大侠帮帮忙

2012-11-30 17:14:41

在C语言中很简单:if a=1, b++;

昨天刚学Labview,只会做累加,不会加条件啊。我是把a的值作为条件结构的输入,在条件结构里加个循环一次的for循环结构,直接用循环变量i做累加器,初值是零。但是这样每次都是i=0, i=i+1=1,累加器一直是1啊……求问大佬怎么破?

2017-03-03 23:27:06

ORG 0000HMAIN:MOV R0,#DATAB;将DB存储的内容的首地址给R0,MOV R1,#08H;LOOP2: MOV A,@R0;把R0的内容放到累加器A中,MOV P0,@R0

2016-04-06 18:26:15

配置三组硬件累加器(Accumulators)->模式一:三组累加器可同时提供个别三组ADC的累加计算->提供二:单一累加器可累加多组ADC资料nADC累加器优势->ADC信号积分

2020-02-11 15:21:00

若 累加器 中值为 1的 位数是奇数 ,则 P置 位 (奇 校验);否 则 ,P清 除--------这句话要怎么理解,

2020-06-23 18:03:21

累加器的概念在中央处理器中,累加器(accumulator)是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算(加法,乘法,移位等等)后就必须要把结果写回到内存

2021-08-30 08:57:54

cin; output[7:0] sum/*synthesis keep*/; output cout;assign {cout,sum}=a+b+cin;endmodule8位寄存器

2016-10-13 12:00:26

请问一下AD9910并行端口控制相位时,并行数据是输入到相位累加器中还是输入到相位偏移字中?

2018-12-25 14:02:29

请问怎样利用ADuC7060的累加器和计数器来计算平均值?如何配置?当ADC0RCR = ADC0RCV时会产生中断,那请问这是什么中断类型?在哪里配置? 请问“和ADC0RCR配合使用,可屏蔽主通道ADC中断,从而产生较低的中断速率”怎么理解?我怎样才能配合ADc0ACC进行平均值的计算?

2018-11-09 09:28:18

通用寄存器于累加器的联系与区别是什么?

2012-09-15 00:13:49

EVAL-AD9832SDZ,AD9832评估板是一款数控振荡器,采用相位累加器,正弦查找表和集成在单个CMOS芯片上的10位数模转换器。为相位调制和频率调制提供调制能力

2019-03-01 10:12:41

TMS320F24X 指令集累加器、算术与逻辑指令附件

TMS320F24X 指令集累加器、算术与逻辑指令

助记

2008-10-17 22:41:11 1070

1070 相位累加器一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。DDS 正是利用了这一特点来产生正弦信号。如图 2,根据

2009-09-03 08:43:21 7736

7736

课件教程

本课程是微机原理课程的ing用。

2015-11-12 16:42:39 0

0 本文开始介绍了累加器的概念和相位累加器原理,其次介绍了累加器的作用,最后介绍了流水线相位累加器的设计与累加定时器在PLC控制程序中的应用。

2018-04-11 11:40:16 68819

68819

本文开始介绍了单片机的概念和工作原理,其次介绍了单片机累加器作用和单片机累加器A与ACC区别,最后阐述了单片机复位电路原理及单片机复位电路的作用。

2018-04-11 12:40:10 11301

11301

本文首先对寄存器、累加器、暂存器做个哥介绍,其次解答了累加器是不是寄存器,最后阐述了寄存器、累加器、暂存器的区别。

2018-04-11 16:31:42 9102

9102 自1994年以来,累加器便成为了学术界非常关注的一个话题。其类似于默克尔树(Merkle Tree),并被用于以密码方式承诺一组数据的知识。稍后,可通过发布证明来证明数据集中子集的成员身份。在默克尔树(Merkle Tree)结构中,证明被称为默克尔分支(或默克尔证明),并且承诺数据的大小是以对数形式增长的。

2019-01-09 10:54:02 3254

3254 一、 加法指令 1、不带进位Cy加法指令 ADD A,Rn(寄存器加到累加器) ADD A,direct(直接寻址字节加到累加器) ADD A,@Ri(间址RAM 加到累加器) ADD A,#data(立即数加到累加器)

2019-09-05 17:27:00 7

7 运算器以完成二进制的算术/逻辑运算部件ALU为核心,再加上暂存器TMP、累加器ACC、寄存器B、程序状态标志寄存器PSW及布尔处理器。累加器ACC是一个八位寄存器,它是CPU中工作最频繁的寄存器

2019-05-07 15:36:44 14535

14535 假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

2019-07-22 08:52:56 7290

7290 寄存器是中央处理器内的组成部份。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。

2019-07-22 09:03:52 4863

4863 加1,请注意这条指令中的A只是一个符号,而不是一个操作数,累加器在指令中只有写成ACC时才是一个操作数。编译程序在编译的过程中将ACC编译为累加器的直接地址OEOH。

2019-10-04 17:00:00 5903

5903

累加器 (accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到 内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

2020-10-14 16:00:00 8

8 本文档的主要内容详细介绍的是Arduino的累加器实验程序和工程文件免费下载。

2021-01-13 17:24:00 5

5 助记符 操作数 指令说明 字节数 周期数 (数据传递类指令) MOV A,Rn 寄存器传送到累加器 1 1 MOV

2021-11-11 19:06:00 34

34 累加器A与ACC区别累加器写成A或ACC在51汇编语言指令中是有区别的。ACC在汇编后的机器码必有一个字节的操作数,即累加器的字节地址E0H,A在汇编后则隐含在指令操作码中。所以在指令中A不能

2021-11-23 09:06:01 105

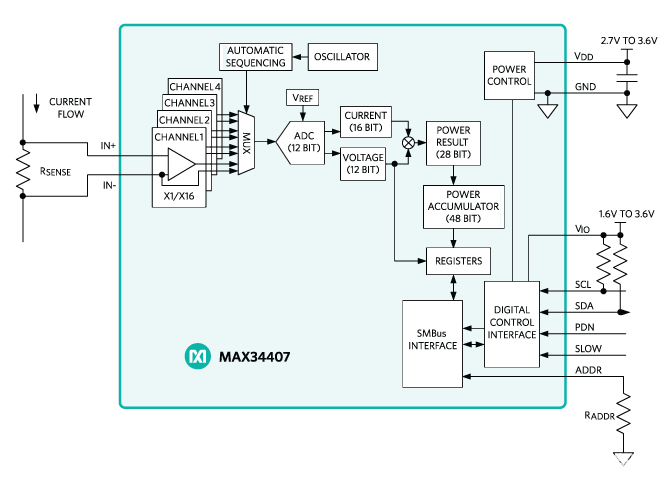

105 对于许多需要平均功率测量的应用,功率累加器是一个很好的解决方案。考虑实时测量开关转换器效率,这样就可以评估转换器效率随时间变化和在不同工作条件下的变化。通过将这种方法扩展到多个电源轨,您可以监控电池

2023-01-03 12:00:19 1114

1114

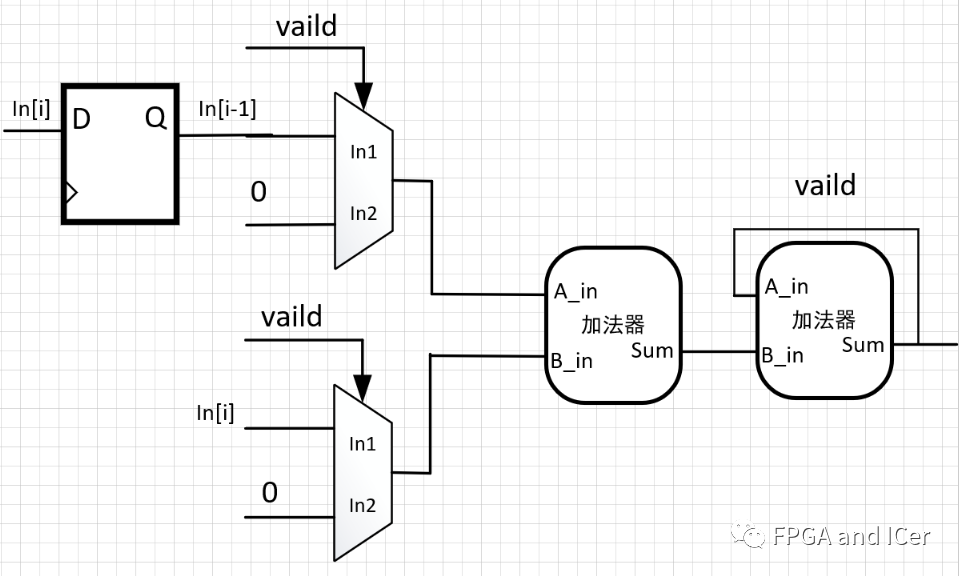

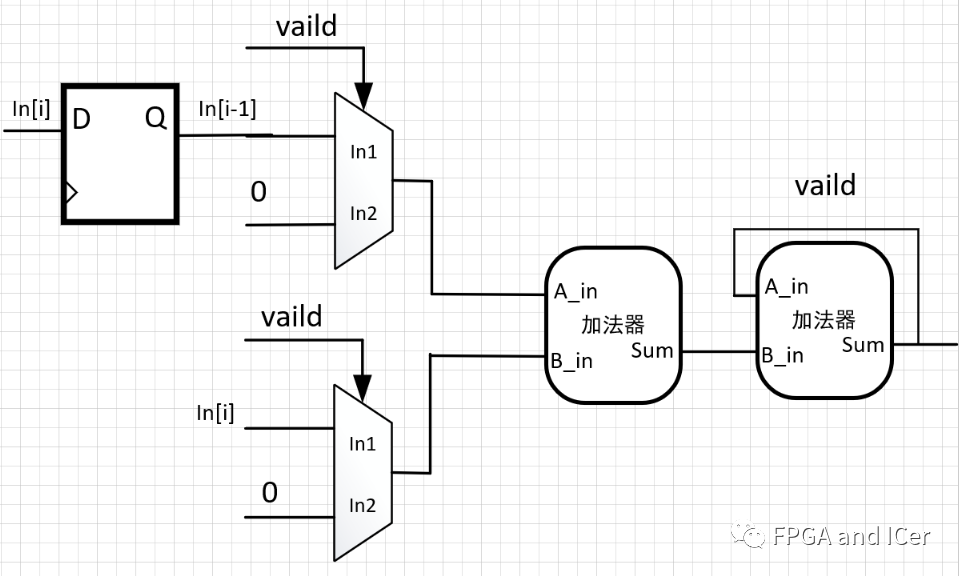

实现累加器的加法器例化的个数。按照原文大佬的设计方法,因为数据连续且加法器的延迟周期是2,使用使用一个实现累加,会有一半的数据丢失。

2023-06-02 16:35:40 1616

1616

电子发烧友App

电子发烧友App

评论