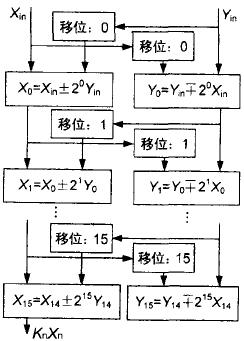

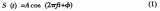

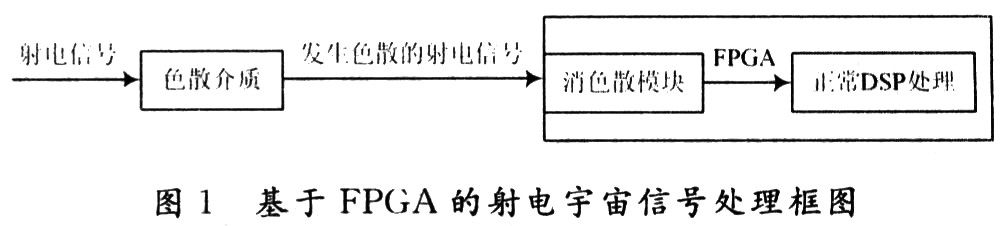

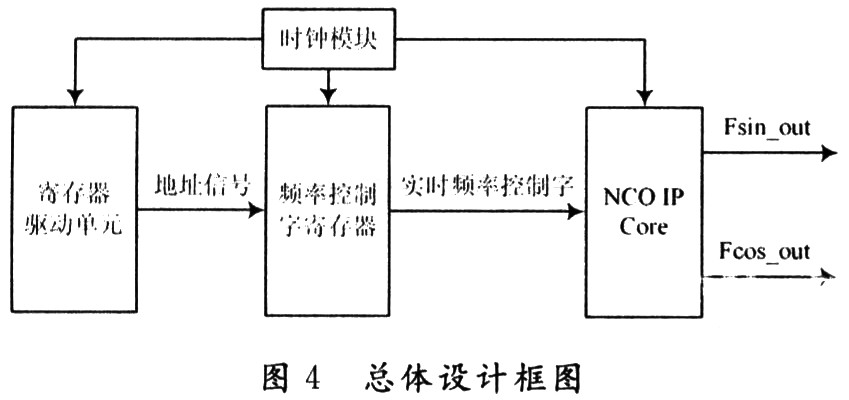

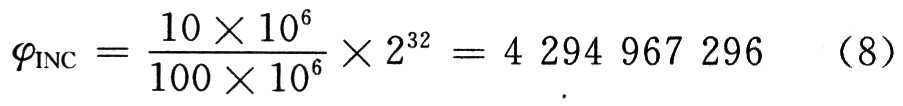

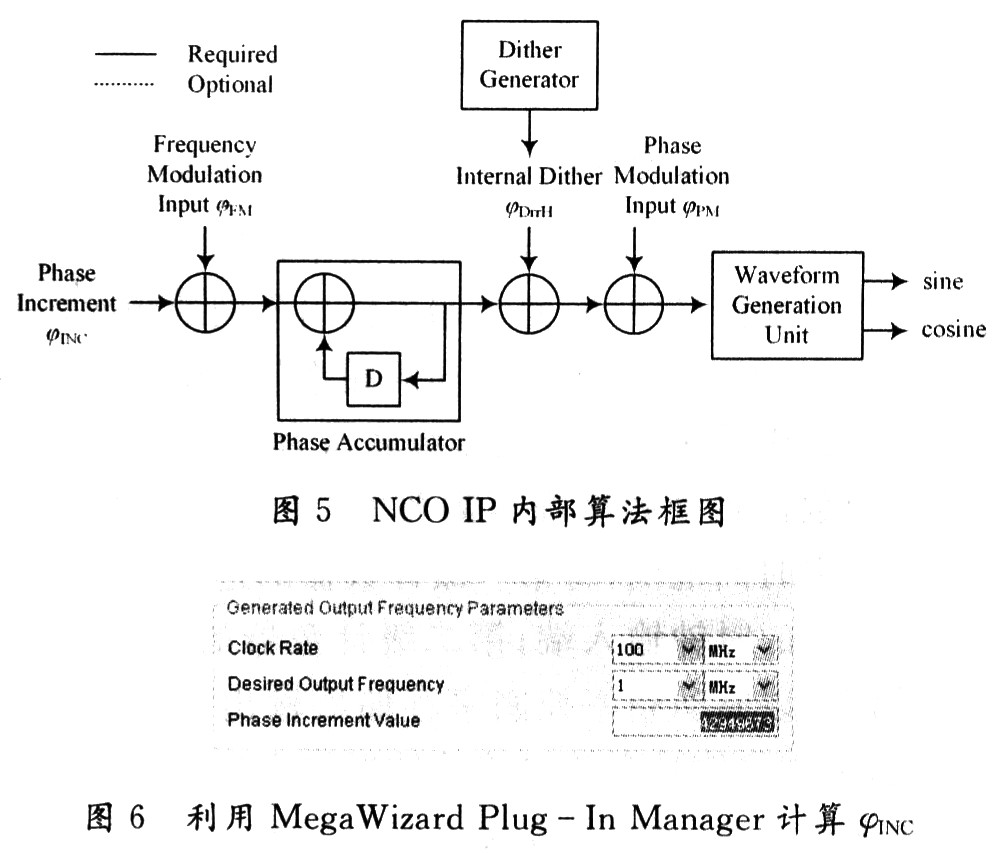

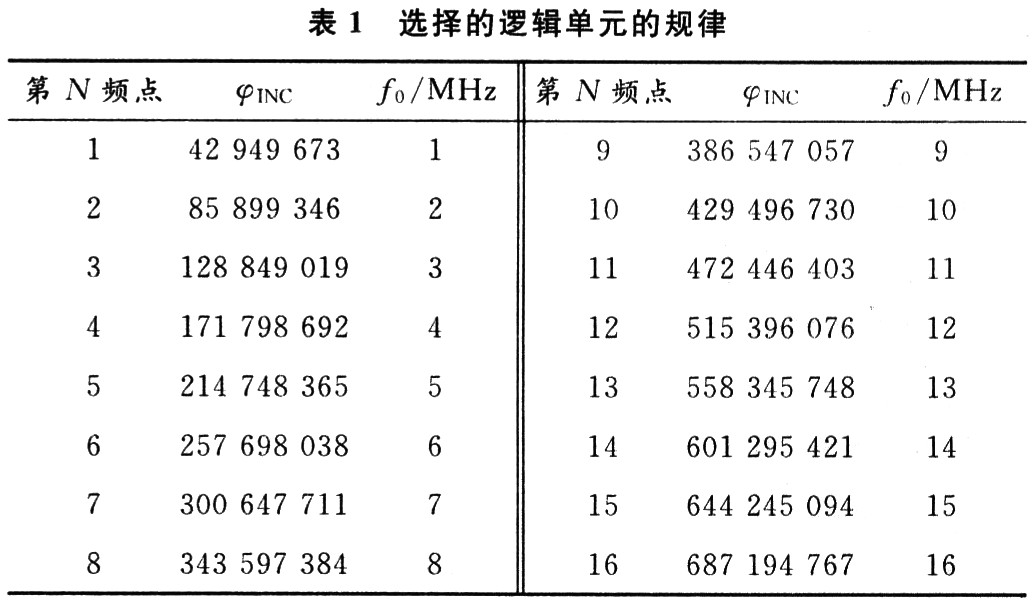

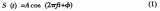

本文给出了一种基于FPGA 的正交NCO 设计方法,可以实现正交的、连续相位、高性能、高精度、可重利用的数控振荡器。

2012-01-06 15:00:07 6457

6457

IP CORE10/100 UNLIMITED RTL

2023-03-22 19:59:35

IP CORE10/100 ETHERNET MAC

2023-03-22 19:59:35

KIT DEVELOPMENT FOR IP CORE1553

2023-03-30 11:49:30

HARDWARE FOR IP CORE1553

2023-03-30 11:49:35

IP MODULE CORE1553 BUS CTLR

2023-03-30 12:03:00

IP MODULE CORE1553 BUS CTLR

2023-03-30 12:03:01

IP MODULE CORE1553 BUS/REMOTE

2023-03-22 19:59:24

IP MODULE CORE1553 REMOTE TERM

2023-03-22 19:59:23

IP MODULE CORE1553 REMOTE TERM

2023-03-22 19:59:26

IP MODULE CORE1553 REMOTE TERM

2023-03-22 19:59:23

IP MODULE CORE1553 REMOTE TERM

2023-03-22 19:59:26

KIT DEV FOR CORE429 IP MODULE

2023-03-30 11:49:29

DAUGHTER CARD IP CORE429

2023-03-30 11:49:29

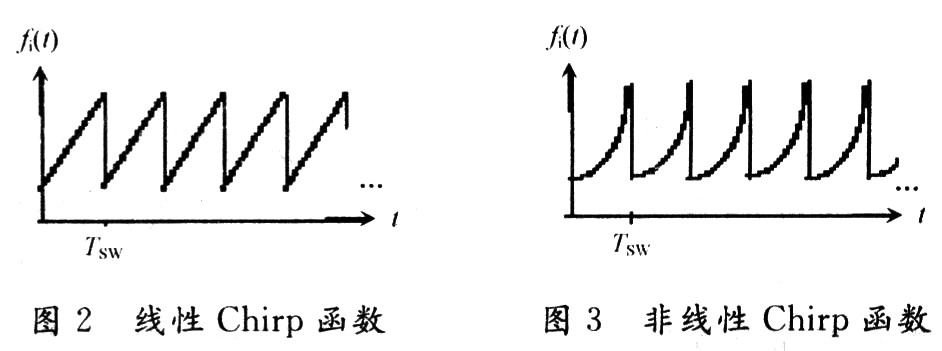

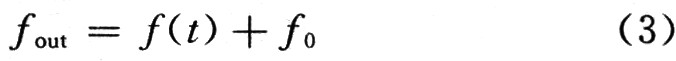

方波脉冲、高斯脉冲、Hermite脉冲和正交椭球波函数等。随着声表面波器件(SAW)的发展,可由低成本、低功耗、低复杂度的声表面波滤波器利用脉冲压缩技术产生和检测线性调频信号(Chirp)。由于

2019-06-14 07:24:09

ISE软件,使用IP core调用DDS,产生正弦载波,使用调频200M时钟做为DDS输入,功能仿真没问题,但后仿真却不显示波形,只是一根红线,是不是频率过高啊,还是什么设置问题,请各位高人赐教,小弟初学FPGA

2013-03-20 20:37:32

已经破解了NCO这个IP核,如图:但是生成的时候一直卡在这里:并且设置参数的时候无论怎样修改参数,生成的波形实际频率都显示为1Hz,如图:

2017-03-23 19:33:51

你好:我想用我自己的项目生成一个IP Core,其他人只能使用这个Core,而不能读取或写入我的代码。如何能够这样做?该软件是ISE8.2.03以上来自于谷歌翻译以下为原文Hi:I wantto

2019-05-24 13:49:21

IP CORE NCO/DDS ECP3 USER CONF

2023-03-30 12:01:18

SITE LICENSE NCO/DDS ECP3 CONF

2023-03-30 12:02:08

IP CORE NCO/DDS ECP2 USER CONF

2023-03-30 12:01:19

SITE LICENSE NCO/DDS ECP2 CONF

2023-03-30 12:02:08

IP CORE NCO/DDS ECP2M USER CONF

2023-03-30 12:01:19

IP CORE NCO/DDS SC/SCM CONFIG

2023-03-30 12:01:19

IP CORE NCO/DDS LATTICEXP2 CONF

2023-03-30 12:01:19

SITE LICENSE NCO/DDS LATTICEXP2

2023-03-30 12:02:08

IP CORE NCO/DDS LATTICEXM CONF

2023-03-30 12:01:19

大家好,我是一个新的用户与PICS,我正在实验中的NCO外围设备在PIC16F15313生产PFM输出。我有一个关于NCO增量寄存器的问题:NCO1ON/NCO1CUL寄存器决定NCO输出高或低

2018-11-26 15:54:42

core开发板的库函数有何功能?core开发板是如何实现GPIO引脚的读写操作呢?

2021-10-26 08:02:52

大家好。可以直接由ISE使用EDK IP Core,例如将其安装到ISE并成为theISE的IP之一。如果不能,那么必须将它用作EDK生成的子系统(microblaze或powerpc)吗?我想要

2019-01-23 10:21:55

以前写过一个SDRAM 的控制程序,现在想玩下IP core,请问该如何使用呢?在 quartus 13的Tools--》Megawizard Plug-in Manager中没有找到SDRAM controller IP Core。请高手指教,谢谢!

2015-08-29 16:24:23

嗨,我已经创建了一个带有IP-Core的硬件设计。但它不能正常工作。对于我提到的调试问题,我创建了一个IP-Core,然后通过AXI Stream。所以我可以检查我的IP-Core是否不起作用

2020-04-14 09:25:10

项目中需要用到OTP来做存储,eMemory (OTP) hard IP core怎么读写?时序要求?有没有人做过相关的?

2017-05-09 14:07:29

s_axis_tdata的实数和虚数位为16位。我想知道使用的定点格式?分数是多少?这样我就可以将它与MATALAB输出进行比较。用户可以在fft ip core中定义固定点格式吗?如果是的话怎么样?

2020-05-12 08:32:53

本帖最后由 tcf8426 于 2017-6-25 10:32 编辑

情况是这样利用quartusII 13.1生成了一个nco 核,进行模块例化和tb文件编写编译通过,没有问题,点击run

2017-06-25 10:28:56

本帖最后由 liu1032042013 于 2017-5-3 22:16 编辑

使用quartus 12.1生成NCO IP 核失败,进度条一直卡着不动,经百度得网友分享的方法,成功解决问题

2017-05-02 21:39:22

nco_run_msim_rtl_verilog.do文件在第41行停止了,文件中的第41行如图 以前在仿真FIR核时出现过类似问题,我的解决方法是改掉模块例化名,原来的模块例化名如图 原来编译好的IP核

2017-06-25 10:36:35

前言shineblink core 开发板(简称Core)的库函数支持PWM通信功能,所以只需要调用两三个API,即可实现PWM功能。PS:Core 仅用五、六行代码即可实现Wifi/Ble/NB

2022-02-11 07:16:42

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

本帖最后由 蛙蛙蛙 于 2021-4-12 17:51 编辑

本视频是Runber FPGA开发板的配套视频课程,主要通过PLL的工程实例讲解高云IP core的使用,课程主要介绍什么是IP

2021-04-12 16:45:11

除了在Xilinx官网上在哪里能下载到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

SPI4-P2接口形式可直接采用Altera公司的IP Core实现。Altera的主流FPGA均实现了硬件DPA功能,以Stratix II器件为例,在使能DPA的情况下使用SPI4-P2 IP Core可实现

2012-11-09 18:43:41

custuom ip core with generic bus width. Inside the core I have to use a addsub ip from xilinx.

2019-04-18 07:12:26

各种 IP Core和参考设计

2012-08-17 23:49:44

如何使用FPGA和IP Core实现定制缓冲管理?

2021-04-29 06:01:33

IP就是知识产权核或者知识产权模块的意思。在EDA技术和开发领域具有十分重要的作用,在半导体产业中IP定义为用于ASIC或FPGA/CPLD中预先设计好的电路功能模块。IP可以分为软IP,固IP和硬IP三种。

2019-11-04 06:36:56

我现在用labview自带的chirp函数生成调频信号,但是我想改变其相位,请问怎么实现

2015-05-28 22:36:52

求chirp generator.VI 不懂哪里可以下载

2014-12-23 16:58:15

跪求chirp generator.VI感谢感谢感谢

2014-12-23 16:57:09

esp-at项目的component/at/include/esp_at_core.h文件中的很多函数在src目录下找不到实现,但是lib文件中很多.a的库。本来想参考一下这些函数的代码实现,请问这些是不开源的吗?印象里早期的AT固件是都开源的。

2023-03-08 08:22:35

项目需要使用FIR和FFT IP core,我下了破解版的quartus,dsp builder和matlab,用dsp builder的基本库建了一个正弦发生器,matlab和modelsim仿真

2015-09-11 11:23:41

大家好,我有一个问题。当我设计DDS IP CORE时,我不知道如何创建不同振幅的sin波。通常我可以创建相同的振幅但不同频率的sin波要叠加。但是,我不知道知道如何实现幅度控制.SFDR的功能是什么?谢谢!

2020-05-13 08:58:43

esp-at项目的component/at/include/esp_at_core.h文件中的很多函数在src目录下找不到实现,但是lib文件中很多.a的库。

本来想参考一下这些函数的代码实现,请问这些是不开源的吗?印象里早期的AT固件是都开源的。

2023-04-24 08:35:26

请问基于labview的chirp信号测距仪的设计中的chirp信号的匹配滤波器怎么设计?最好有设计图,谢谢各位大神!!

2016-03-24 14:27:07

详细分析8 位微处理器IP core PicoBlaze 的结构、原理与设计方法; 介绍PicoBlaze 的指令集和调试工具pblazeIDE,讨论PicoBlaze 的编程方法和应用设计实例;列举几种PicoBlaze 的应用方案。

2009-04-15 11:43:25 17

17 USB Function IP Core

The Universal Serial Bus (USB) has evolved to the standard

2009-06-14 09:03:23 45

45 本文介绍一款USB 设备控制器IP CORE 的设计与实现。论文首先介绍了USB 设备控制器的设计原理,模块划分及每个模块的功能。然后介绍了该IP CORE 在ModelsimSE 中的功能仿真及FPGA 验证结

2009-08-06 11:39:00 8

8 本文利用Altera 公司开发的RS、NCO 和FIR IP core 以及Simulink、DSP_Builder中的模块快速搭建了一个RS(204,188) +DQPSK 的低中频调制解调系统。分别在Simulink、Modelsim 中验证了系统的功能,

2009-08-10 11:09:07 10

10 基于CORDIC 算法的NCO 实现田力, 冯琦(西安电子科技大学 电路设计研究所,陕西 西安 710071)摘要:NCO 在信号处理方面有着广泛的应用。而函数发生器是NCO 中的关键部分,

2009-12-15 14:30:33 23

23 利用SoPC技术设计了一种通用性强、细分数可编程、升/降速曲线可编程的步进电机控制器IP Core,并利用Altera的DE2开发板进行了设计验证。

2010-07-30 11:37:09 23

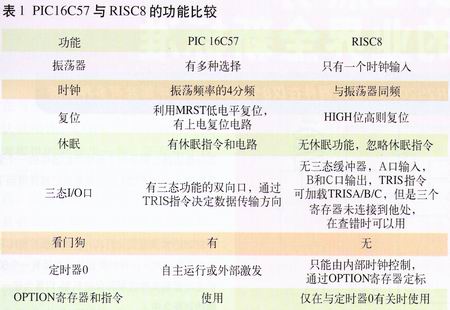

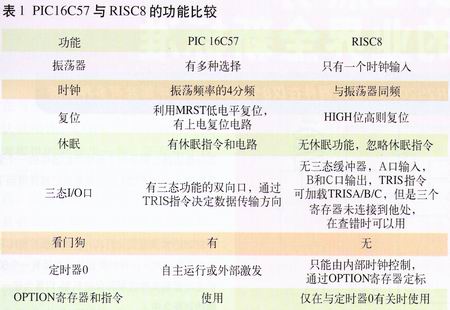

23 摘 要:本文介绍了与免费IP Core运作有关的问题以及免费资源的若干来源,然后通过对两个不同来源的、免费的八位RISC CPU进行比较和分析,给出了若干选用免费核

2006-03-24 13:33:18 855

855

利用FFT IP Core实现FFT算法

摘要:结合工程实践,介绍了一种利用FFT IP Core实现FFT的方法,设计能同时对两路实数序列进行256点FFT运算,并对转换结果进行求

2008-01-16 10:04:58 6709

6709

各种 IP Core和参考设计

以下各种 IP Core和参考设计是由相关设计者提供,可以免费下载学习或使用。

[使用注意事项]

大部分设计是针

2008-05-20 10:17:24 5481

5481 PicoBlaze处理器IP Core的原理与应用

详细分析8位微处理器IP core PicoBlaze的结构、原理与设计方案;介绍PicoBlaze的指令集和调试工具pblazeIDE,讨论PicoBlaze的编程方案和应用设计实

2009-03-28 15:17:30 820

820

摘要:详细分析8位微处理器IP core PicoBlaze的结构、原理与设计方案;介绍PicoBlaze的指令集和调试工具pblazeIDE,讨论PicoBlaze的编程方案和应用设计实例;列

2009-06-20 10:54:39 741

741

基于DSP Builder的Chirp信号源设计

DSP Builder是Ahera公司提供的一个系统级(或算法级)设计工具。它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL级(硬件实现)两

2009-10-04 09:47:11 1104

1104 本文通过分析数控振荡器的实现原理和性能,给出了通过FPGA来实现NCO的具体方法,同时通过QUARTUSⅡ中的仿真验证了本设计的正确性。

2011-05-09 11:11:07 14048

14048

在论坛中经常有人会问起 altera 软件fft ip 中使用方法,有些人在使用这个fft ip core 的时候没有得到正确的结果,事实上,这个ip core 还是比较容易使用的。有些人得不到正确的仿真结果

2011-05-10 15:19:24 0

0 分析Chirp函数在频域上的一般特性,提出利用FPGA的嵌入式软核NiosⅡ处理器在嵌入式操作系统μC/OS-Ⅱ上实现Chirp的方法

2011-06-15 11:02:13 1014

1014

文中采用Dechirp信号处理的思想,给出了基于Chirp变换的宽带DRFM实现技术,该方法通过Dechirp变换,DRFM和Chirp变化重构雷达信号,理论分析和仿真验证表明,能较好保留雷达照射信号的时频特征

2012-01-10 17:16:05 23

23 PCI总线是目前最为流行的一种局部性总线 通过对PCI总线一些典型功能的分析以及时序的阐述,利用VetilogHDL设计了一个将非PCI功能设备转接到PC1总线上的IP Core 同时,通过在ModeISim SE PLU

2012-04-01 15:06:44 40

40 Chirp信号是一个典型的非平稳信号,在通信、声纳、雷达等领域具有广泛的应用,为了更好的显示其特性,文中首先介绍了各个算法的定义和公式,然后用各种时频分析方法对该信号以

2013-02-22 16:15:37 107

107 Xilinx FPGA工程例子源码:LCD IP CORE

2016-06-07 14:13:43 10

10 Xilinx FPGA工程例子源码:摄像头的硬件函数(IP核)

2016-06-07 15:07:45 13

13 Xilinx FPGA工程例子源码:麻省理工实验室的MIPS IP CORE

2016-06-07 15:13:15 9

9 因为自从13.0开始,就开始有Qsys了,而关于FFT和NCO的仿真特别麻烦,网上有关资料又少之又少,所以特写此教程介绍怎么使用modelsim工具仿真附带有QSYS的fft和NCO的ip核的工程教程

2017-02-27 19:02:57 45

45 基于PCI桥接IP Core的VeriIog HDL实现

2017-10-31 09:28:57 22

22 本页包含通过LabVIEW FPGA模块可用的Xilinx CORE生成器IP的列表。LabVIEW通过Xilinx IP节点实现该IP。 下列IP名称和说明来自于Xilinx数据表。LabVIEW

2017-11-18 05:55:51 4465

4465 信号。为了解决上述问题,即仅依靠少量快拍实现对宽带线性调频(chirp)信号的高分辨率DOA估计,提出了一种FrFT-SPICE算法。首先,将宽带chirp信号进行特定阶次的分数阶傅里叶变换(FrFT),将时域的chirp波形变为FrFT域的单频正弦波形;其次,推导出F

2018-01-16 10:57:16 0

0 这些结果表明,我们的软件正弦 NCO 的线性度和噪声都处于理论水平,远远超出了测试市场上大多数高精度 ADC 所需的阈值。

2022-06-20 11:55:13 877

877

这些结果表明,我们的软件正弦 NCO 的线性度和噪声都处于理论水平,远远超出了测试市场上大多数高精度 ADC 所需的阈值。

2022-07-24 16:44:02 867

867

在本系列的第1部分中,我们将了解如何设计基于直接数字频率合成(DDFS)原理的非常精确的正弦波发生器,但在浮点DSP处理器上通过软件实现。在第 2 部分中,我们将介绍如何在软件中实现高精度 NCO。

2022-11-28 17:06:37 880

880

IP_数据表(A-23):Analog Switch IP Core

2023-03-16 19:28:40 0

0 电子发烧友网站提供《Chirp PubNub聊天应用程序.zip》资料免费下载

2023-06-13 10:50:23 0

0 IP_数据表(A-23):Analog Switch IP Core

2023-07-06 20:14:57 0

0

![]()

电子发烧友App

电子发烧友App

评论