设计用于SoC集成的复杂模拟及射频模块是一项艰巨任务。本文介绍的采用基于性能指标规格来优化设计(如PLL或ADC等)的方法,可确保产生可制造性的鲁棒性设计。通过这样的设计,开发者能在保证成本效益和不超预算的前提下,高效、及时地将产品或器件推向市场。

对于当今复杂系统级芯片(SoC)设计,尤其是含有复杂模块如PLL或ADC等的设计,利用综合平台设计者能获得以下好处:1) 可根据性能规格来创建最优的模块设计;2) 可对性能与设计余量空间(如芯片面积与速度之间等)之间的折衷进行评估;

当使用者输入性能指标规格时,综合平台通过将电路公式表示为凸出的优化问题,可同时对器件尺寸及布局布线综合进行优化。这样,对设计者的挑战就只有通过合成来验证综合过的设计是否正确,以及能否满足所有工作条件下的预期性能需求,而不必对每一个实例都进行详尽的硅验证。

我们都清楚,在减少芯片体积并使功能最大及功耗最小方面,设计者面临着巨大的压力。因此,可靠性余量空间有所减小,这就使得鲁棒性模拟及射频IC的制造成为一项艰巨任务。以下几种因素需要关注:

1. 电路性能主要取决于晶体管的行为;

制造过程中的很小改动都会导致电路性能的极大变化。在生产期间,改变技术参数可导致电路失败。针对可制造性设计的目标是以设计为中心,以至于多数被制造的电路能满足性能规格,同时还能使面积开销最小化。这就要求不同工艺下都需使用精确的晶体管模型。

2. 由于诸如快速开关数字电路等而产生的基底噪声耦合,会极大地降低敏感模拟信号的质量;

因此,设计者必须进行仔细的版图设计以减少器件错配及寄生效应,这对确保正确的电路行为极为关键。不像数字电路,模拟电路要求设计者记住大量性能规格,因此对模拟模块进行重新设计是一件非常耗时的工作。对于采用0.13微米及以下工艺的设计来说,必须满足HCE、NBTI及STI应力效应以获得最佳的模拟及射频性能。在这些挑战面前,旨在控制可靠性目标的现有商业工具却不精确。

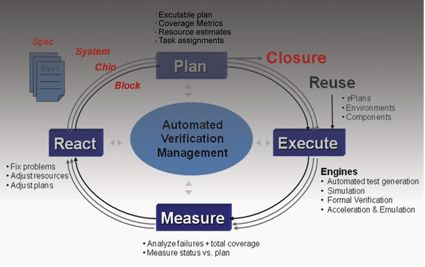

如何验证鲁棒性?

通过考虑各种会反向影响制造成品率及性能的因素并将其整合到综合平台中,设计者可实现鲁棒性设计。

在描述电路行为及性能规格的相同公式中,设计者也可加入多种技术变量。如果边界设计可行,则意味着只要设计处于可行性范围内,即无需对每一种新的实例进行验证。

提高成品率的一项传统策略是运行多次Monte Carlo模拟,但Monte Carlo分析却是一项保证成品率最优化的艰苦工作。

Monte Carlo分析可创建一批具有容差元件的电路,并对电路性能进行统计测试。每一种电路都由多个元件(从与用户定义容差及分布类型相匹配的大批元件中随机选出)构成。其结果是一条设计约束分布曲线。从此数据可分析出可靠性、成本及制造电路的能力。此概念是在优化程序中使用多次Monte Carlo模拟。

环路的组成为:先由优化器推荐一种候选电路,然后再由评估引擎对每一候选电路的质量进行评估。如此循环反复,直至满足规格指标为止。此过程被称为设计中心化方法,实际上只能用于后设计优化。一些商用工具采用SPICE及一个或一组数值搜索引擎。优化者(器)可以是:设计工程师;模拟退火法(Simulated annealing);牛顿法(Newton's method);或任何其他类型的经典优化方法。

不用说,Monte Carlo方法是一种CPU密集型的方法,实际上不可能用于超过数十个晶体管的电路设计中。更重要的是,该方法要求模拟电路设计者及优化专家进行以下工作,即:先由经验丰富的模拟设计者输入SPICE架构及测试基准,然后再由优化专家选择步骤规模、搜索空间及搜索方法。总而言之,Monte Carlo方法要求由专家来对资源进行规划,而且极为耗时,所有这些因素使得我们需要一种优化成品率的新方法。

凸起优化

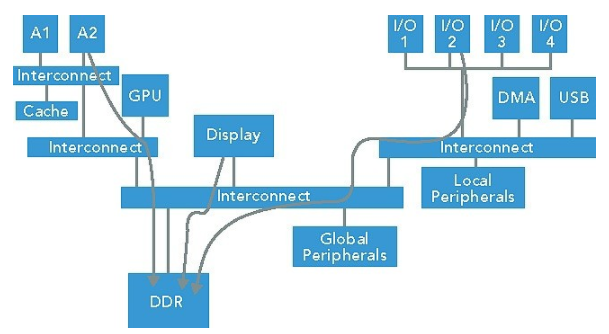

模拟及射频元件(如锁相环及数据变换器等)的晶体管行为及性能指标,都能用设计变量的多项式来表示。(见图2)

如果设计者将其设计问题表示为几何程序,则他能创建一种特殊类型的凸起优化问题。最终解决方案完全独立于起始点(甚至起始点不可行,且不可行指标能被清楚地检测到)。设计者能获得非常有效的整体优化法所带来的好处,即使是很大的问题,他也能获得迅速计算出来的结果。如果有这样的解决方案,则保证程序能获得收敛。事实上,这是一种能决定全局优化设计的快速综合方法。

通过改变变量并考虑相关函数中的标记,几何程序可用公式被重新表示为一种凸起优化问题。在使用几何程序对电路建模时,设计空间被表现为一种凸起集,而凸起问题则具有特殊的性质:它们的可行集就是凸起。

鲁棒性模拟电路创建

正如我们所知,电参数(如晶体管增益等)中的统计变化是由制造工艺中的变化所致,并能影响电路的性能及成品率。通过保证制造及电路设计之间的紧密耦合,综合平台可产生出鲁棒性设计。

这些工艺变化是由于随机制造变化所致,且传统上都被合并到工艺模型中。例如,在制造器件时,掺杂扩散或沉积中的非一致性条件,可导致氧化厚度及扩散深度的改变。氧化厚度及基板、聚合、植入及表面电荷中掺杂水平的变化等,都会对门限电压值造成影响。照相平版印刷工艺中的分辨率可引起MOS晶体管中的W/L改变。而这些参数改变又会引起电参数(如表面电阻及门限电压等)发生变化。

例如,用500 MHz统一增益带宽来将运放限制在一个特定功耗上。为满足这一约束条件,可在多个工艺阶段对设计进行优化,并且还能将电源电压变化及诸如电阻变化这样的因素包括在内。表1列出了一些与工艺有关的指标,这些指标作为优化程序的一部分被包括到综合平台中。

现在对表1中所列的参数进行说明。电源电压变化百分比可进行设置,例如设为10%。在1.8 V电源上,优化可保证所有指标都能在1.62V及1.98V(亦即Vdd ± 10%)上达到。例如,当功耗在1.98V上为最差情况时,饱和余量将在1.62V上为最差情况。如果任何片上电阻的百分比变化都为20%,则优化可保证所有指标都能在± 20%电阻值上达到。由于电阻可用于电压参考及环路滤波电路中,并由此而对制造成品率产生很大影响,因此优化时将考虑参考电流变化及其稳定性余量。

在选择鲁棒设计的工艺阶段时,应按以下要求进行:

?每一工艺阶段都必须能保持每一项指标,且报告指标值为所选阶段的最差值;

? 针对目标的报告值在所有阶段上都应为最差值。

参数匹配

除不同晶圆批次之间的工艺变化外,模拟设计者们必须密切注意器件性能,因为同一芯片上的器件性能也会有变化。

晶体管及电路失配对模拟设计性能的极限有极大的影响。像数据变换器分辨率、运放的CMRR及PSRR等典型性能参数,都取决于晶体管的匹配。这些匹配(或失配)效应可严重地影响设计鲁棒性。

设计者可利用晶体管门限电压中的失配来计算设计中的噪声成分。他既可将这种失配建模成面向特定晶体管的门限电压及面向该工艺的额定门限电压的变化,也可将这种失配建模成带有与器件面积成反比偏差的随机变量。他可将标准电流偏差建模成特定晶体管饱和电流Id,sat与该工艺中晶体管额定饱和电流Id,sat之间的一个百分比变化。由于制造过程中的随机变化,位于差分对两边的晶体管将在门限电压及饱和电流中表现为失配。

噪声及电源变化

像噪声及电源电压变化这些因素,它们对模拟及射频设计的影响比对数字设计的影响要大得多。例如,模拟设计中的增益及带宽等一级参数能被很好地满足。但由于有噪声,因此像SNR这些指标就不能很好地实现。

优化设计不仅必须能在噪声环境下具有鲁棒性,而且还应能抵抗电源变化。为满足这些约束条件,综合平台允许用户针对任何环境对设计进行调整。以下说明利用PLL中的累积电源抖动(在Vdd上步进10%)来抵抗电源电压变化的例子。

当加上这种步进时,理想参考时钟与输出时钟之间的瞬时相位误差将开始累积。经过一段时间之后,环路将作出反应,并开始将这些信号驱动回相位调整中。这项指标代表电压步进后的最差瞬时相位误差。为具有鲁棒性,假设电压步进的上升时间远小于参考周期。事实上,任何一种片上电压步进都很可能具有短得多的上升及下降时间,因此能提供远优于此项指标的性能。

其实设计可能对一种噪声比对另一种噪声更加脆弱。解决方案是,用户先对环境进行评估并确定出最大弱点,然后将约束设定为一个低值,再确定下一个最大弱点并将其设定到稍高一点的值。优化程序试图匹配所有约束条件,而将最重要约束设为最紧值且将最不重要约束设为宽松值,能使优化程序最大限度地满足设计要求

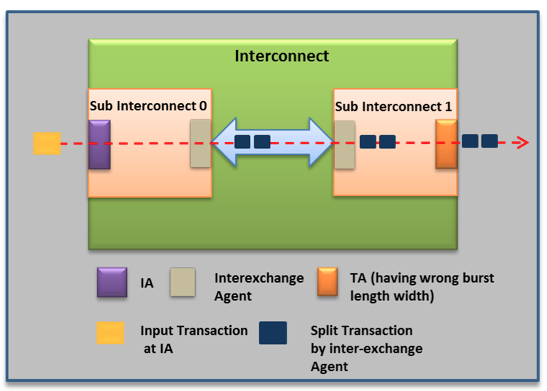

寄生

使用综合平台的设计者,通过将寄生效应构建到优化模型中,还能在开始优化时将所有寄生效应包括在内,并借此消除设计过程中的不确定因素。这些模型被构建成能处理与器件及其互连有关的不必要的电阻、电容及电感效应等信号完整性问题。设计者能对相邻连线间互耦这样的效应进行建模,如果这些因素影响到性能,则综合平台中的程序算法将把这些因素考虑到电路布局中。

布局布线

综合平台利用几何程序来控制电路布局,以达到系统性能目标。这些问题涉及到器件、模块、底层规划及布线等。为达到模拟及射频电路所需的性能指标,可考虑以下电路布局布线约束。

对称约束:一个部件可被约束成以水平或垂直轴线为中心;两个同样大小的部件可被约束成相对轴线为镜像。

镜像节点:可围绕轴线对节点进行镜像。

节点匹配:可将标记(布局扩展)增加到布线中,以使两个节点的水平及垂直金属长度整体上均衡。

对齐:两个元件可被约束成互相沿顶部、底部、左或右对齐。

电容约束:这能通过弯曲布线长度来限制布线与基底间的电容。

IR压降约束:布线器将对电源轨道尺寸进行规定,以将IR压降值限制在指定的数值上。

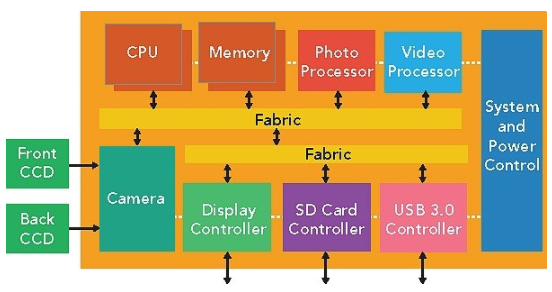

对器件生成器中的另一个重要考虑是中间数字化,这能减少器件电容,并确保有对称的电流方向、保护环(guard ring)及虚拟(dummy)结构等。图3显示了为模拟或射频设计所生成的器件例子。

如何验证模拟设计的鲁棒性

Barcelona公司可保证对每一优化实例的鲁棒性验证都能通过使用验证金字塔来完成,并已将它应用检验0.18及0.13毫米综合平台上。正如我前面所提到的,利用这种验证金字塔使我们既能避免设置及运行Monte Carlo模拟的艰辛,又能避免运行多种硅制造工艺的昂贵。

我们的验证金字塔分为4层。第1层:我们先基于试验及试探法设计来选择指标规格。设计规格空间由主要指标的无关联扫描来覆盖。在PLL的例子中,就是抖动、功率及静态相位误差。我们将试探性标准用于考虑了各指标相关性的栅格的定义。

我们进行一系列优化来使这一综合平台的功能合格。此过程包括将试验方案的数量从3个增加至49个。试验方案被定义成从1至7选择工艺阶段、将电源从其额定值上变化10%、将片上多晶硅电阻从其额定值上改变20%以及选择三种VCO频率等。

第2层:我们通过检查可从SPICE仿真上提取的参数与从综合平台上预计的参数之间的相关性来从第1级上检验优化设计的精度及功能是否合格。

我们特别强调对模拟电路模块进行SPICE仿真。例如,对于VCO,我们同时在低及高频上对以下内容进行仿真:功耗饱和余量、频率范围、kVCO增益、PSRR、(kVdd)。

第3层:我们期望能提供由综合平台预测的指标规格与在宏观层次上所提取仿真之间的相关性。

为保证指标能准备好用于制造,我们要求该综合平台能产生没有版图与原理图误差的GDSII数据。我们还要求不能违反任何半导体设计规则。

模拟设计中使性能下降或者甚至造成设计失败的一个主要问题是寄生效应。

第3层验证包括对自动GDSII版图的寄生预测。第2层指标选择是基于覆盖频率与低抖动范围、低功率PLL并针对相应的频率范围和覆盖以下应用的硅样片进行,这些应用包括:消费多媒体、无线及有线通信、微处理器及ASIC。

第4层:综合平台验证的最后一步是硅确认。这里的目标是通过硅中的三项合格性验证来确认第1层的严格及鲁棒性。选择第3层设计。表2及表3给出了在TSMC的 0.18 μm逻辑工艺上生产的两种PLL的关键参数。显示结果是针对最差情况下的工艺、电压及温度变化。大约在几小时内即可产生出GDSII版图,且无需任何改动即可直接提交给晶圆代工厂

电子发烧友App

电子发烧友App

评论