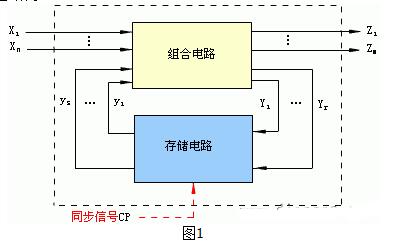

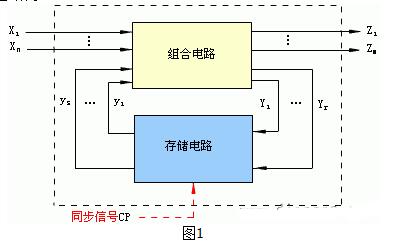

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 53525

53525

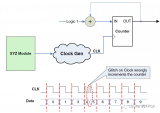

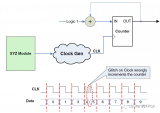

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2767

2767

描述 本设计咨询主要介绍一个错误的时钟偏移计算导致错误时序收敛的问题。 出现问题的情况: 这可能会影响使用生成时钟的设计,其具有以下特征: 使用 Vivado 2018.2.x 及更早版本。 用户

2020-12-24 11:16:24 5086

5086 了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 459

459 时序逻辑电路的精华——计数器

2022-12-29 09:23:56 1010

1010 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-01-13 13:57:47 1830

1830

数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

476 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。

2023-08-03 09:27:25 915

915

芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 809

809 组合逻辑产生的时钟可能有毛刺,会被错误地当成有效时钟边沿,在设计中会导致功能错误。因此,不要使用组合逻辑的输出作为时钟。

2024-01-22 09:30:50 168

168

时序逻辑电路的特点

2019-10-08 05:34:53

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

。同步的数字系统正是由许多的寄存器,以及寄存器中间的组合逻辑构成的(也包括寄存器间的直接连接)。显然,如果要数字系统正常工作,每个寄存器的建立时间和保持时间都必须得到满足。假设时钟信号ck到达所有寄存器

2020-08-16 07:25:02

进去, 1080p出来的时候,视频正常 播放出来。 可是当 1080p进, 4k出来的时候,视频图像上会有水波纹。当时就猜想是 FPGA 送给 下游器件SII9136的 时序不能满足。于是把输出的时钟

2016-11-15 18:15:03

,但问题是,最后数组63相乘这一步就是没有实现,我看网上说是时序逻辑会延后一个时钟周期导致最后一步没有加上,我试着将程序中timer==7‘d63改为timer==7‘d64,最后一个就加上了,但这样的话,新的问题又来了,我希望64个周期算完的,却要65个周期,这要什么方法解决这个问题?

2017-09-13 11:02:51

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

寄存器的代码编写。接下来我们要更进一步从深沉次来探讨基于寄存器的同步以及时钟的设计原则。(特权同学,版权所有)虽然在上一章已经对组合逻辑和时序逻辑的基本概念做过描述,但是这里还是要再额外唠叨几句组合逻辑

2015-06-29 09:31:03

基本时序路径本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 对于FPGA内部而言,通常有四大类的基本时序

2015-07-20 14:52:19

VGA驱动接口时序设计之3时钟约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 如图8.26所示

2015-07-30 22:07:42

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

的不同,我们可以从三方面来理解,分别是code(代码),电路图和波形图三方面。 从代码层面来看,时序逻辑即敏感列表里面带有时钟上升沿,如果是没有上升沿或者是带有“*”号的代码,为组合逻辑。电路层面,两种

2020-03-01 19:50:27

什么是时序逻辑?时序逻辑由哪几部分构成?

2021-09-17 07:43:37

时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表...

2021-11-11 06:13:35

本文来自芯社区,谢谢。1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统

2021-07-26 08:26:57

的延时。而在时序逻辑中,该实例除了组合逻辑满足条件外,只有在时钟信号clk的每个上升沿输出z2才会发生变化。这里有一个细节大家也需要注意,x和y的组合逻辑输出值在时钟上升沿到来的前后的某段时间内(即建立

2017-11-17 18:47:44

。组合逻辑设计代码: 对应的电路为: 时序逻辑对应代码为: 对应的电路为: 可以思考一下,这个两种设计方法都没有任何错误。那么在设计时应该用哪一种呢? 在设计时,有没有什么规定

2023-03-06 16:31:59

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

静态时序分析与逻辑设计

2017-12-08 14:49:57

1 进一步强化EDA仿真软件的使用;2 掌握利用MSI、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4&

2009-03-18 20:06:31 47

47 时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 基于PLD芯片的时序逻辑设计与实现:原理图输入设计直观、便捷、操作灵活;1-1、原理图设计方法简介QuartusII已包含了数字电路的基本逻辑元件库(各类逻辑门及触发器),宏

2009-10-29 22:03:10 0

0 摘要:通过实际例子,阐述了次态卡诺图在分析和设计时序逻辑电路中的使用方法。该方法的使用可以使时序逻辑电路的分析和设计得到一定的简化,过程中思路清晰,状态转换直

2010-04-28 10:03:10 21

21 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

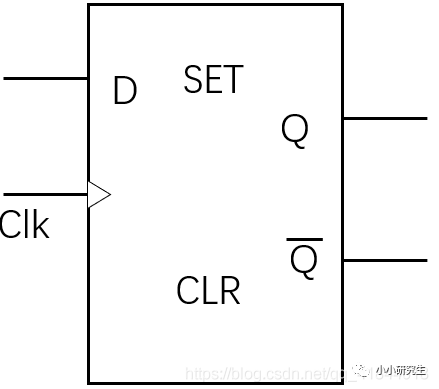

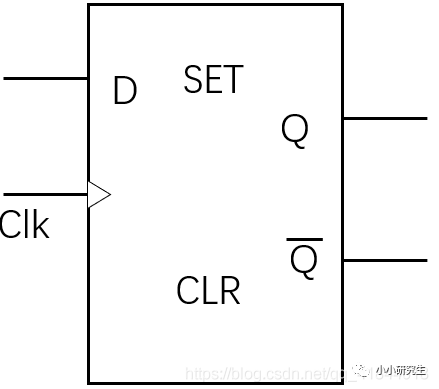

39 本章首先介绍能够存储1 位二值信号的基本单元电路锁存器和触发器。着重介绍各种锁存器和触发器的电路结构、工作原理、逻辑功能、特性及其描述方法。接着介绍时序逻辑电

2010-08-10 11:55:44 0

0 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

69 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

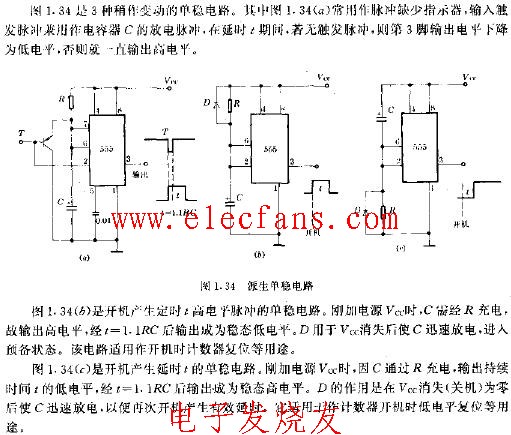

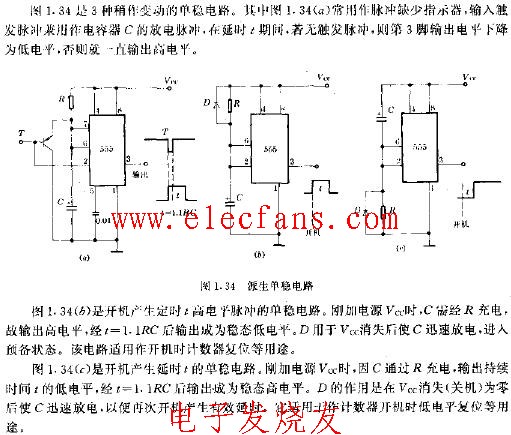

55 派生单稳电路

2008-05-19 23:06:06 775

775

实验十六 时序逻辑电路? 实验(1) 计数器?一、实验目的?⒈ 熟悉计数器的设计方法及工作原理。?⒉ 了解同步计数器与异步计数器的区别。?⒊ 应用

2008-09-24 22:17:08 3210

3210

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3438

3438

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 8146

8146

时序逻辑电路分析实例

例1 分析图所示电路的逻辑功能。设起始状态是

2009-04-07 23:20:25 4398

4398

使用逻辑分析仪调试时序问题

在今天的数字世界,嵌入式系统比以往任何时候都更为复杂。使用速度更快、功耗更低的设备和功能更强大的电路,

2009-08-26 12:09:14 1389

1389

时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 9900

9900

时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 5041

5041 定义了时钟单位阶跃信号C(n) 提出了一种利用带相对时钟坐标的逻辑方程表示逻辑信号的方法通过对所设计的DDR SDRAM控制器的读写时序的分析建立了控制器主要信号的时序表达式并利用

2011-09-26 15:34:12 39

39 c++面向对象课程实验指导书题目_继承与派生。

2016-01-14 16:25:42 0

0 主要讲了时序逻辑电路的相关知识,能够方便大家学习使用

2016-02-29 14:25:53 0

0 华为静态时序分析与逻辑设计,基础的资料,快来下载吧

2016-09-01 15:44:10 56

56 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 0

0 华为BTS逻辑分析时序,感兴趣的小伙伴们可以瞧一瞧。

2016-11-15 17:23:09 0

0 在传统设计中,所有计算机运算(算法逻辑和存储进程) 都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW) 的功耗,厂商间展开了残酷的竞争

2017-10-25 15:41:59 25

25 在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷的竞争

2017-11-15 15:40:13 12

12 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 8630

8630 时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 5673

5673

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 91327

91327

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 123040

123040

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 63961

63961

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 106879

106879

域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步策略来解决跨时钟域问题。

2018-09-01 08:29:21 5302

5302

时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

2018-11-24 11:17:51 3197

3197

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 30485

30485 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 49627

49627 将驱动方程代入相应触发器的特性方程中,便得到该触发器的次态方程。时序逻辑电路的状态方程由各触发器次态的逻辑表达式组成。

2019-02-28 14:06:14 23502

23502 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7636

7636

静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 掌握时序逻辑电路的设计方法及调试技巧,熟练掌握触发器的功能及应用,熟练掌握常用MSI时序逻辑芯片的功能及应用

2020-05-20 08:00:00 20

20 本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 组合逻辑生成的时钟,在FPGA设计中应该避免,尤其是该时钟扇出很大或者时钟频率较高,即便是该时钟通过BUFG进入全局时钟网络。

2020-10-10 10:28:32 3639

3639

本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 口静态时序工具可识别的时厅敌障数要比仿真多得多,包括:建立/保持和恢复移除检査(包括反向建立保持):最小和最大跳变:时钟脉泩宽度和时钟畸变;门级时钟的瞬旴脒沙检测;总线竞争与总线悬浮错误;不受

2021-01-14 16:04:03 9

9 文章目录高温下STM32采用内部晶振作为系统时钟的时钟源导致时序紊乱问题高温导致时钟紊乱问题引出时钟紊乱问题总结高温下STM32采用内部晶振作为系统时钟的时钟源导致时序紊乱问题单片机的时序问题在整个

2021-12-14 18:58:22 5

5 如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发,综合器推断时序逻辑。如前所述,所有阻塞赋值都在活动队列中进行计算和更新。读者请参阅之前分享的分层事件队列一文。

2022-09-06 09:44:02 3306

3306 时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导致时序问题。

2022-10-26 09:04:51 823

823 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-02-12 10:28:36 771

771 使用always_ff和在灵敏度列表中指定一个时钟边沿并不意味着过程中的所有逻辑都是时序逻辑。综合编译器将推断出每个被非阻塞赋值的变量的触发器。阻塞赋值也可能推断出触发器,这取决于赋值语句相对于程序中其他赋值和操作的顺序和上下文。

2023-02-20 10:38:06 442

442 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 4816

4816

1、时序错误的影响 一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是

2023-03-17 03:25:03 426

426 时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 400

400 组合逻辑最大的缺点就是会存在竞争冒险,使用时序逻辑就可以极大地避免这种问题,从而使系统更加稳定。

2023-05-22 15:30:24 791

791

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1882

1882

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 1983

1983

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 2539

2539

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312 时序逻辑电路 一 : 触发器 1:D 触发器 : 时序逻辑电路最小单元 。 (1):D 触发器工作原理 忽略清零端情况下 : 当使能条件 ( 往往为时钟的触发沿 : 上升沿 / 下降沿 ) 满足

2023-11-02 12:00:01 308

308

电子发烧友网站提供《完美时序-时钟产生和分发设计指南.pdf》资料免费下载

2023-11-18 10:27:02 0

0 电子发烧友网站提供《时序逻辑电路电子课件.ppt》资料免费下载

2023-11-21 14:43:40 0

0 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 499

499 成部分之一。 寄存器属于时序逻辑电路。时序逻辑电路是指其输出状态不仅依赖于当前的输入,还依赖于过去的输入和时钟信号的变化。在寄存器中,时钟信号用来控制数据的输入和输出,确保在时钟上升沿或下降沿时,数据能够稳定地从输入

2024-02-18 09:37:20 249

249 本文将介绍一个跨时钟错误的案例如图所示,phy_status作为一个多bit的phy_clk时钟域的信号,需要输入csr模块作为一个可读状态寄存器

2024-03-11 15:56:48 152

152

电子发烧友App

电子发烧友App

评论