电子发烧友网讯: 本文主要讲述了TAKUMI公司的图象IP核参考设计可用于S2C原型验证平台。S2C宣布,一家总部位于日本的高级图形知识产权(IP)供应商,TAKUMI 公司,已成功在S2C基于FPGA的快

2012-07-03 13:50:45 1548

1548 Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1403

1403 Cadence设计系统公司公布一个新版的尖端功能验证平台与方法学,拥有全套最新增强功能,与之前发布的版本相比,可将SoC验证效率提高一倍。 Incisive ®12.2提供了两倍性能,全新Incisive调试分析器产品,全新低功耗建模,以及当今复杂IP与SoC高效验证所需的数百种其他功能。

2013-01-27 10:44:38 1437

1437

OVM验证方法学的Cookbook大家喜欢看英文版?还是中文版?了解一下 大家都在看什么版本的?都是什么口味?{:soso_e120:}

2012-01-11 10:41:45

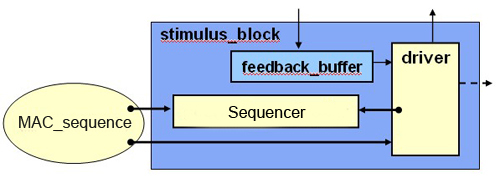

。 OVM 是一个开源 SystemVerilog 类库和方法,它定义了可重用验证 IP (VIP) 和测试的框架。它是 100% IEEE 1800SystemVerilog,并提供构建块(对象)和一组

2022-02-13 17:03:49

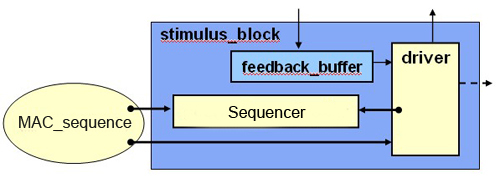

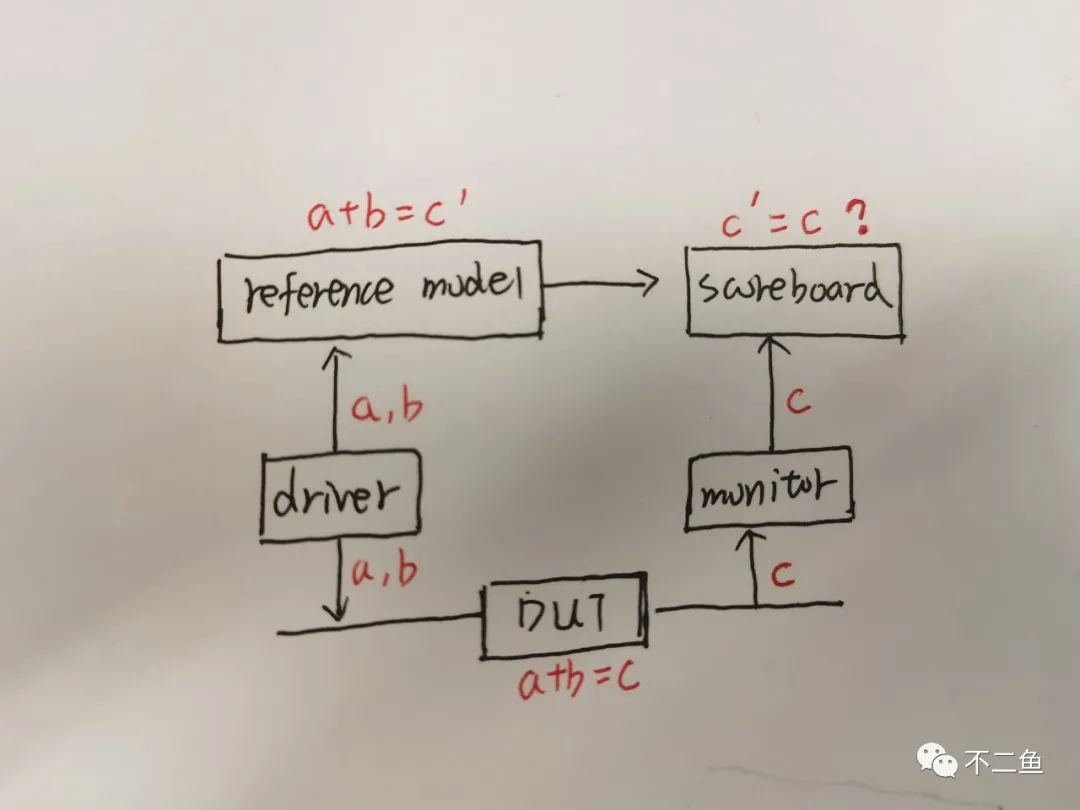

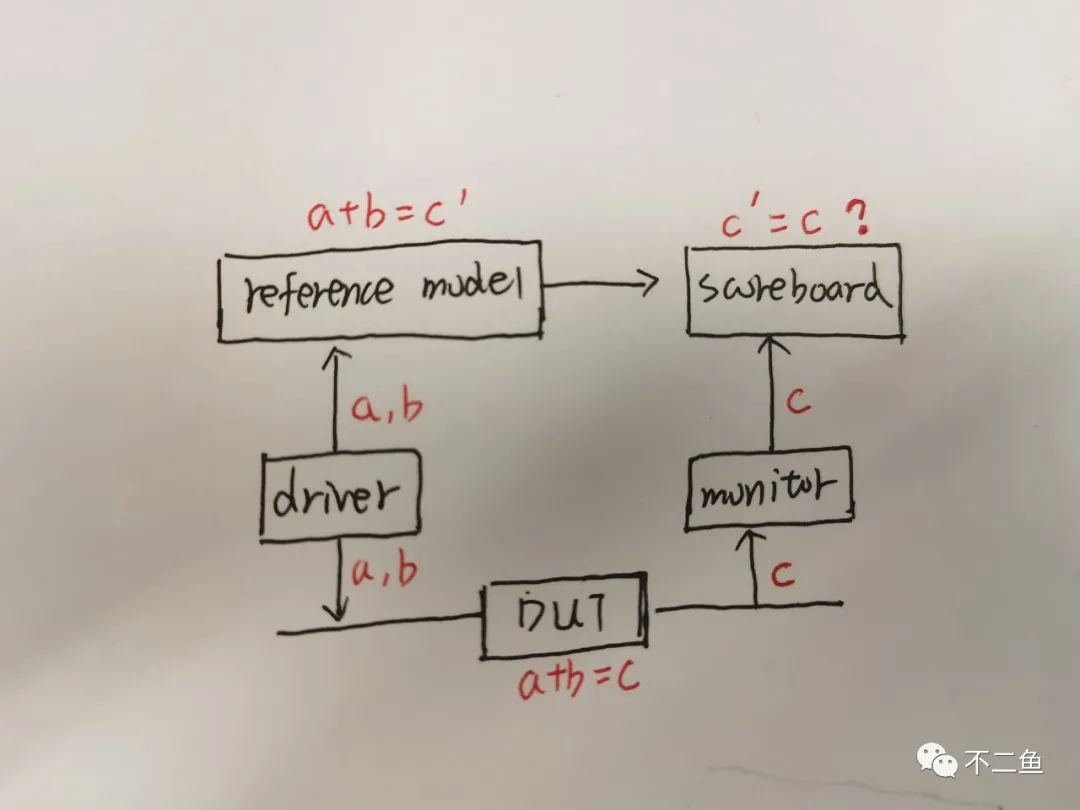

验证用于找出DUT中的bug,这个过程通常是把DUT放入一个验证平台中来实现的。一个验证平台要实现如下基本功能:验证平台要模拟DUT的各种真实使用情况,这意味着要给DUT施加各种激励,有正常的激励

2020-12-02 15:21:34

加入factory机制 上一节《IC验证"一个简单的UVM验证平台"是如何搭建的(五)》给出了一个只有driver、使用UVM搭建的验证平台。严格来说这根本就不算是UVM验证

2020-12-08 12:07:21

本帖最后由 IC那些事儿 于 2020-12-4 15:50 编辑

上次更新完《IC验证"UVM验证平台"组成》后本打算不再更新......但有人反映要继续更新...继续

2020-12-04 15:48:19

目前市面上基于SystemVerilog的验证主要有三种:VMM(Verification Methodology Manual),这是Synopsys在2006年推出的,在初期是闭源的。当OVM

2020-12-01 15:09:14

IC验证平台

2021-08-09 07:39:47

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

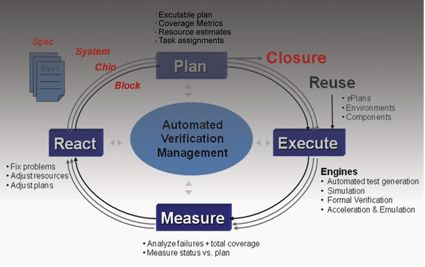

第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-11-01 06:28:47

Languages)”的一部分,又属于“半导体IP核-不仅仅是设计(SemiconductorIP Core – Not Just Design)”书系列的“验证用IP核和IP核验证(VerificationIP

2022-11-03 13:07:24

SoC芯片的规模一般远大于普通的ASIC,同时深亚微米工艺带来的设计困难等使得SoC设计的复杂度大大提高。仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80%,采用

2019-10-11 07:07:07

机的协商,保持接口参数同步;数据通道验证在该接口参数下的功能和性能,实现了接口的功能和性能验证的自动化,大大提高了测试效率,保证测试用例的覆盖率。该工具适用于多种平台下的UART和SPI接口验证。0

2019-06-21 05:00:09

随着现代集成电路技术的发展,尤其是IP的大量使用,芯片的规模越来越大,系统功能越来越复杂,普通的EDA和FPGA仿真在速度和性能上已经无法胜任芯片仿真验证的要求,功能验证已经成为大规模芯片设计的一个

2010-05-28 13:41:35

我用quartus II调用modelsim仿真fft ip核,仿真结束后我想验证下数据是否正确,结果是:我用matlab生成同样的整形数据,然后用modelsim仿出的结果txt文件与用

2012-09-20 12:48:37

,本科5年数字芯片验证工程师岗位要求:1、熟悉systemverilog 语言,熟练掌握UVM/VMM/OVM验证方法学,独立完成过中等规模以上模块的验证开发2、熟悉数字芯片验证流程,三年以上相关工作经验3、硕士3年,本科5年联系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

免费的 I3C 从属 IP 芯片是否经过验证?

2023-05-05 07:16:21

本文介绍一种通用的UART自动验证平台,可用于自动测试UART接口的所有方面。

2021-04-30 06:46:31

随着集成电路的规模和复杂度不断增大,验证的作用越来越重要。要在较短的时间内保证芯片最终能正常工作,需要将各种验证方法相结合,全面充分地验证整个系统。FF-DX是一款高性能定点DSP,为了在提升芯片

2011-12-07 17:40:14

、OVM等等,并对仿真方法有自己的深刻理解; 4.具有系统验证和调试经验,能够根据数据通信产品的特点确定仿真验证和仿真测试点; 5.具有3年以上仿真验证经验; 6.具有仿真平台(硬件平台和软件平台

2015-07-16 11:04:49

)。为此.我们利用VHDL设计一种嵌入式RISC8微处理器及应用芯片.设计后的IP核下载到FPGA(Field Programmable Gate Array.现场可编程门阵列)芯片上做验证,并在

2021-09-01 19:32:45

的软件模拟器作为验证的第一站。Mentor Graphics验证IP(VIP)是一个可复用组件库,无缝集成到使用UVM、OVM、Verilog、VHDL和SystemC构建的测试平台,也可与第三方软件

2017-04-05 14:17:46

寻找一个现成的PMSM控制算法验证平台,帮我做控制算法的验证实验。拜谢各位前辈了!我的情况说明:我目前已经在simulink中搭建好控制算法,并且仿真出来了,但没有验证的平台。因为时间比较急,我希望

2019-12-23 16:25:38

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

SoC系统验证平台总体框架是怎样的?SoC系统验证平台如何去构建?

2021-04-28 07:13:41

验证码与打码平台的对抗讲起。何为打码平台?打码平台的基本原理是利用人工智能技术实现对验证码设计原理的突破。其工作流程如下图所示:以前黑灰产要想获取数据,首先会向自己想要获取的数据页面发送请求,若该数据页面

2022-11-01 15:21:22

SoC与IP有什么关系?如何去验证IP?

2021-04-28 06:02:37

讲述两个内容,芯片验证以及验证计划。首先来看看芯片验证在芯片设计当中的地位。芯片验证是在一个芯片设计的过程当中,验证各个转化阶段是否正确的执行的过程,一个芯片的设计涉及到多个阶段的转化。首先,分析市场需求

2021-01-21 15:59:03

请教一下基于FPGA的通信系统基带验证平台该怎样去设计?

2021-04-28 06:59:45

硬件验证方法简明介绍本书“硬件验证方法简明介绍”是“半导体 IP 核——不仅仅是设计”系列丛书中“验证 IP 和 IP 核验证”的一部分。本书调查、处理和介绍了 IC 验证中涉及的一些关键方法、工具

2022-11-26 20:43:20

芯片的验证平台,用的主要技术 手段是SC/SV+OVM.平心而论,本人决非所谓高手、牛人。所谓的高手是什么,举个例子,IC行业用TCL语言的人不少,这个语言的发明人觉得研究中用C不爽,干脆自己写一个

2012-01-11 10:51:00

该IP核验证平台采用ALTERA Cyclone系列FPGA,型号为EP1C12Q240C8,提供超过30万门系统资源和240k bit的内部高速FIFO, 以及内部两个高速PLL,可以合成

2019-06-20 05:00:02

PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。 S1500硬件验证板照片以下为IP核验证平台提供

2019-06-12 05:00:07

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

探讨了IP 核的验证与测试的方法及其和VHDL 语言在IC 设计中的应用,并给出了其在RISC8 框架CPU 核中的下载实例。关键词:IP 核;片上系统;验证

2009-06-15 10:59:14 32

32 研究40Gb/s 交换IP 软核的验证和测试方法。通过建立SDH 芯片验证平台和SDH 芯片测试平台, 实现IP 软核的功能仿真、时序仿真和芯片性能测试。使得IP 软核质量优良、性能稳定, 适应性

2009-11-27 14:30:16 6

6 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43:22 7

7 无线温度验证系统 温度压力一体 温度验证仪分有线系统与无线系统。有线的温度验证系统精度低,价格相对于无线产品的价格要低廉的多,无线验证系统操作方便,节省时间,而有线布线特别麻烦。所以在某些全封闭

2023-12-20 10:10:23

提出了基于事务断言验证技术,用属性说明语言(Property Specification Language,PSL)描述系统的属性,用事务进行系统的验证,通过编程语言接口机理和工具控制语言来控制验证中PSL断

2010-08-02 17:26:35 0

0 IP验证增量仿真技术的运用

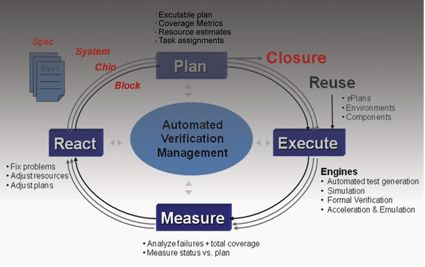

验证涉及每个阶段的迭代循环:仿真、检查结果,改变激励或设计或调试设置,重新仿真并不断重复。在系统调

2009-01-27 17:58:24 834

834 随着深亚微米工艺技术日益成熟,基于IP复用的IC设计方法广泛采用,集成电路芯片的规模越来越大,这对集成电路验证技术和方法学提出了很大的挑战。就如芯片

2009-04-04 10:58:40 1360

1360

Cadence为PCI Express 3.0推出首款验证解决方案

Cadence设计系统公司宣布其已经开发了基于开放验证方法学(OVM)的验证IP(VIP)帮助开发者应用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 针对数字信号处理器的不同仿真和验证要求,提出了一种可测性软硬件协同仿真和验证平台的设计. 采用可配置IP 模块和总线结构,实现了硬件平台可配置性和可重用性;采用在线仿真模块

2011-06-09 17:54:21 39

39 IP核验证平台采用6层板PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。

2012-01-17 14:02:19 1501

1501

本文利用Altera公司的FPGA开发工具对皋于国产龙芯I号处理器IP核的SoC芯片进行ASIC流片前的系统验证,全实时方式运行协同设计所产生的硬件代码和软件代码,构建一个可独立运行、可现场

2012-04-21 15:22:01 3161

3161

电子设计创新企业Cadence设计系统公司,今天宣布使用ARM AMBA协议类型的Cadence验证IP(VIP)实现多个成功验证项目,这是业界最广泛使用的AMBA协议系列验证解决方案之一。顶尖客户,包括

2012-11-07 08:21:52 997

997 无MCU的USB2.0设备控制器IP设计与验证

2013-09-23 17:18:17 40

40 Mentor Graphics 公司(纳斯达克代码:MENT)今日宣布推出面向 ARM AMBA 5 AHB 片上互连规范的验证 IP (VIP)。该新 VIP 在 Mentor® 企业验证平台

2015-11-12 11:28:11 1132

1132 SoC基于IP设计的特点使验证项目中多语言VIP(Verification IP)协同验证的需求不断增加,给验证工作带来了很大的挑战。为了解决多语言VIP在SoC验证环境灵活重用的问题。提出了一种

2015-12-31 09:25:13 12

12 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 基于IEEE1500标准的IP核测试壳的设计与验证_冯燕

2017-01-07 19:00:39 23

23 北京亚科鸿禹电子有限公司在北京发布一款针对2K/4K超高清视频验证的原型验证开发平台-VeriTiger-M2000T。此平台作为亚科鸿禹”All-In-One”家族的最新成员,主要为广大的视音频SOC/IP的硬件/软件验证客户提供完整的解决方案。

2017-02-11 16:49:11 1406

1406 基于OVM的32位微处理器验证_吴勇昊

2017-03-17 08:00:00 3

3 参数化的IP是可配置的,这意味着在不同的SOC中IP设计可以有不同的设计参数,设计参数可以对应到协议、端口号、端口名称、以及内部逻辑。大量的IP设计参数非常影响验证环境的构建,比如testbench

2017-09-15 14:37:34 6

6 功能验证正成为IP 验证的瓶颈,并影响到整个设计团队。设计工程师想方设法提高验证效率,以实现整个芯片设计的最佳利益。在这里,我们提供10 个简单技巧,显著提升您的IP 验证效率。 1.参与验证计划

2017-10-19 09:17:23 8

8 技术方法,验证了SoC系统、DSP指令、硬件IP等。实验证明,此FPGA验证平台能够验证SoC设计,提高了设计效率。

2017-11-17 03:06:01 13138

13138

随着集成电路设计技术的发展和芯片集成度的提高,验证已经成为芯片设计流程中的主要瓶颈。本文设计了一个基于FPGA的智能卡验证平台,并对验证方法做了详细阐述。本文对于双界面智能卡芯片验证的成功实践

2017-11-17 16:25:01 1037

1037 利用Xilinx的FPGA设计了一个FPGA原型验证平台,用于无源高频电子标签芯片的功能验证。主要描述了验证平台的硬件设计,解决了由分立元件实现模拟射频前端电路时存在的问题,提出了FPGA器件选型

2017-11-18 08:42:22 1938

1938

,并应用到包交换芯片的仿真验证中。仿真结果显示,新设计的验证平台能通过修改随机信号约束条件和产生随机信号的权重值,使芯片的功能覆盖率达到100%。

2018-01-12 11:28:24 2379

2379

复旦大学微电子学院某国家重点实验室内部教学视频:基于ZYNQ FPGA与PC的IP设计与验证方案。

关键词:IP设计,IP验证,AXI总线协议,ARM,UDP传输,PYTHON

2019-08-06 06:16:00 1968

1968

验证 SmartMesh IP 对于工业物联网应用的数据可靠性

2021-03-20 11:16:15 8

8 第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-10-25 12:36:01 22

22 基于高通方案,罗德与施瓦茨使用R&S CMX500 5G无线综测仪平台验证了10 Gbps端到端(E2E) IP数据性能。

2021-10-27 16:28:21 1755

1755

历时4月,可支持18亿门SoC全芯片验证的英诺达硬件验证云平台成都中心一期成功实现满载运行,圆满达成云平台一期运营所有目标!英诺达的云平台,不同于传统的IDC机房,机器要求高、运营复杂、专业要求极高

2021-12-17 13:54:49 1771

1771 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 种新的验证 IP(VIP)解决方案,助力工程师迅速有效地验证设计,以满足最新标准协议的要求。

2022-06-06 11:18:21 2665

2665 芯片验证就是采用相应的验证语言,验证工具,验证方法,在芯片生产之前验证芯片设计是否符合芯片定义的需求规格,是否已经完全释放了风险,发现并更正了所有的缺陷,站在全流程的角度,它是一种防范于未然的措施。

2022-07-25 11:48:49 5263

5263 ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)今日发布FPGA-Go-ASIC验证平台。

2022-07-29 10:08:16 784

784 近期疫情严重,身为社畜的我只能在家中继续钻研技术了。之前写过一篇关于搭建FIFO验证平台的博文,利用SV的OOP特性对FIFO进行初步验证,但有很多不足之处,比如结构不够规范、验证组件类不独立于DUT等问题。此次尝试验证更复杂的IP,并利用SV的更多高级特性来搭建层次化验证平台。

2022-08-10 11:14:49 2229

2229 半导体各领域的发展难度与日俱增,验证可能是整个发展过程中最具挑战性的阶段。多年来,研究显示在验证上投入的时间和资源所占的百分比会随着新时代芯片的出现而增加。因此整体上,验证的快速成长超过芯片开发

2022-11-18 10:40:07 673

673 百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 1060

1060 原文标题:从IP级到多芯片系统,这个验证解决方案“一锅端”了 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-03-17 03:35:03 304

304

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-03-28 09:33:16 854

854 在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-05-30 15:04:06 905

905

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程。 首先对 测试平台集成者(testbench integrator) 和 测试编写者(test

2023-06-13 09:14:23 326

326

验证平台顾名思义就是为了验证而存在的。普通意义上来说,如果是IP验证,当验证人员拿到设计的某模块的RTL代码(DUT,Design Under Test),设计文档之后,就会根据文档,基于自己的理解去着手写验证计划,提取功能点

2023-06-15 18:12:04 745

745

IP核的开发过程中,面临着许多关键技术,比如IP核的规格定义、基于接口的设计、IP核测试存取结构标准、IP核的验证与打包等。对于IP核的验证,主要是建立参照模型和测试平台,然后进行回归测试和形式验证

2022-06-10 11:50:16 373

373

IP核的开发过程中,面临着许多关键技术,比如IP核的规格定义、基于接口的设计、IP核测试存取结构标准、IP核的验证与打包等。对于IP核的验证,主要是建立参照模型和测试平台,然后进行回归测试和形式验证

2022-06-13 11:47:03 317

317

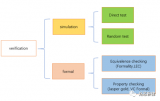

相信很多人已经接触过验证。如我以前有篇文章所写验证分为IP验证,FPGA验证,SOC验证和CPU验证,这其中大部分是采用动态仿真(dynamic simulation)实现,即通过给定设计(design)端口测试激励,结合时间消耗判断设计的输出结果是否符合预期。

2023-07-21 09:53:24 4285

4285

国芯科技(688262)。sh) 8月2日的投资者在互动平台(interface),公司目前正在与合作伙伴一起流片验证相关chiplet芯片高性能互联IP技术,和上下游合作厂家积极开展包括HBM技术在内的芯片的设计与封装技术的研究正在积极进行。”

2023-08-02 12:01:33 643

643 基于XCVU440-FLGA2892的多核处理器多输入芯片验证板卡为实现网络交换芯片的验证,包括四个FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片验证任务,多任务功能验证。

2023-08-24 10:58:23 476

476

ic验证是封装与测试么? IC验证是现代电子制造过程中非常重要的环节之一,它主要涉及到芯片产品的验证、测试、批量生产以及质量保证等方面。 IC验证包含两个重要的环节,即芯片设计验证和芯片生产验证

2023-08-24 10:42:13 464

464 随着半导体技术的快速发展,集成电路芯片的复杂度日益增加,芯片设计中的验证工作变得越来越重要。验证的目的是确保芯片在各种工况下的功能正确性和性能稳定性。在这个过程中,testcase(测试用例)扮演着关键角色。本文将简要介绍 testcase 的基本概念、设计方法和在芯片验证中的作用。

2023-09-09 09:32:31 547

547 在芯片设计流程中,验证环节是至关重要的一环。它直接关系到芯片的性能、可靠性和成本。

2023-09-11 09:58:49 1192

1192 任何芯片都需要把芯片划分成更便于管理的小模块/特性进行验证。

2023-10-07 14:41:31 322

322 当设计的规模动辄几十亿门,系统验证时间不断的增加,硬件验证系统几乎是验证工程师不可或缺的利器,因此对高性能硬件验证系统提出了更多的需求。

2024-01-05 10:06:47 254

254 FPGA验证和UVM验证在芯片设计和验证过程中都扮演着重要的角色,但它们之间存在明显的区别。

2024-03-15 15:00:41 94

94 FPGA原型验证平台与硬件仿真器在芯片设计和验证过程中各自发挥着独特的作用,它们之间存在明显的区别。

2024-03-15 15:07:03 131

131

电子发烧友App

电子发烧友App

评论