16日,三星电子宣布在基于EUV的高级节点方面取得了重大进展,包括7nm批量生产和6nm客户流片,以及成功完成5nm FinFET工艺的开发。 三星电子宣布其5纳米(nm)FinFET工艺技术的开发

2019-04-18 15:48:47 6010

6010 全球电子设计创新企业Cadence设计系统公司日前宣布其与TSMC在3D IC设计基础架构开发方面的合作。

2012-06-11 09:47:43 1071

1071 新思科技公司(Synopsys)在过去五年多与行业领导者合作共同开发了对FinFET技术的支持,通过提供经生产验证的设计工具与IP来推进对FinFET技术的采用。

2013-02-19 10:42:54 823

823 ARM (LSE:ARM; Nasdaq: ARMH) 和Cadence (NASDAQ: CDNS) 今天宣布合作细节,揭示其共同开发首款基于台积电16纳米FinFET制程的ARM®Cortex™-A57处理器,实现对16纳米性能和功耗缩小的承诺。

2013-04-07 13:46:44 1509

1509 Altera公司与台积公司今日共同宣布在55纳米嵌入式闪存 (EmbFlash) 工艺技术上展开合作,Altera公司将采用台积公司的55纳米前沿嵌入式闪存工艺技术生产可程序器件,广泛支持汽车及工业等各类市场的多种低功耗、大批量应用。

2013-04-16 09:05:09 925

925 Cadence系统芯片开发工具已经通过台积电(TSMC) 16纳米 FinFET制程的设计参考手册第0.1版与 SPICE 模型工具认证,客户现在可以享用Cadence益华电脑流程为先进制程所提供的速度、功耗与面积优势。

2013-06-06 09:26:45 1236

1236 昨日台积电官方宣布,16nm FinFET Plus(简称16FF+)工艺已经开始风险性试产。16FF+是标准的16nm FinFET的增强版本,同样有立体晶体管技术在内,号称可比20nm SoC平面工艺性能提升最多40%,或者同频功耗降低最多50%。

2014-11-14 09:31:58 2127

2127 在国际电子电路研讨会大会(ISSCC)上,三星展示了采用10纳米FinFET工艺技术制造的300mm晶圆,这表明三星10纳米FinFET工艺技术最终基本定型。

2015-05-28 10:25:27 1715

1715 12纳米领先性能(12LP)的FinFET半导体制造工艺。该技术预计将提高当前代14纳米 FinFET产品的密度和性能,同时满足从人工智能、虚拟现实到高端智能手机、网络基础设施等最具计算密集型处理需求的应用。 这项全新的12LP技术与当前市场上的16 /14纳米 FinFET解决方案相比,电路密度提高

2017-09-25 16:12:36 8666

8666 据台湾经济日报最新消息,联电(2303)与下一代ST-MRAM(自旋转移力矩磁阻RAM)领导者美商Avalanche共同宣布,合作技术开发MRAM及相关28纳米产品;联电即日起透过授权,提供客户具有成本效益的28纳米嵌入式非挥发性MRAM技术。

2018-08-09 10:38:12 3129

3129 8月30日,中芯国际发布2018年中期业绩,收入同比增长11.5%至17.22亿美元;毛利同比增长5.6%至4.38亿美元。中芯国际在14纳米FinFET技术开发上获得重大进展。中芯国际的第一代FinFET技术研发已进入客户导入阶段。

2018-08-31 14:44:33 5140

5140 晶体管制造工艺在近年来发展得不是非常顺利,行业巨头英特尔的主流产品长期停滞在14nm上,10nm工艺性能也迟迟得不到改善。台积电、三星等巨头虽然在积极推进7nm乃至5nm工艺,但是其频率和性能

2020-07-07 11:38:14

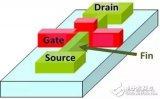

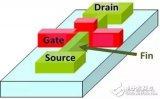

增强;同时也极大地减少了漏电流的产生,这样就可以和以前一样继续进一步减小Gate宽度。目前三星和台积电在其14/16nm这一代工艺都开始采用FinFET技术。图6:Intel(左:22nm)和Samsung(右:14nm)Fin鳍型结构注:图3、图6的图片来于网络。

2017-01-06 14:46:20

台积电0.18工艺电源电压分别是多少?是1.8v跟3.3v吗?

2021-06-25 06:32:37

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

有机会“独吞”A7代工订单。 台积电作为全球规模最大的专业集成电路制造公司,其技术优势的领先,在业界可谓屈指可数。台积电积极开发20纳米制程,花旗环球证券指出,在技术领先MAX3232EUE+T优势下,未来1

2012-09-27 16:48:11

台积电正在大量生产用于苹果iPhone8手机的10nm A11处理器。消息称,苹果可能在下个月初正式发布iPhone 8,但是具体发货日期仍然不确定。 据悉,台积电已经采用10nm FinFET

2017-08-17 11:05:18

EMC设计、工艺技术基本要点和问题处理流程推荐给大家参考。。

2015-08-25 12:05:04

技术开发成功,同时透露会朝第二代的 FinFET 技术开发。若***一举朝 7 纳米前进,将会成为全球第四家 7 纳米技术供应商,与英特尔、台积电、三星分庭抗礼。同时,华为海思的麒麟980也抢先发布,首款

2018-09-05 14:38:53

Sic mesfet工艺技术研究与器件研究针对SiC 衬底缺陷密度相对较高的问题,研究了消除或减弱其影响的工艺技术并进行了器件研制。通过优化刻蚀条件获得了粗糙度为2?07 nm的刻蚀表面;牺牲氧化

2009-10-06 09:48:48

苹果晶圆代工龙头台积电16纳米鳍式场效晶体管升级版(FinFET Plus)将在明年1月全产能量产,搭配整合型扇出晶圆尺寸封装(InFO WLP)的系统级封装(SiP)技术,在x86及ARM架构64位

2014-05-07 15:30:16

:为把openEuler 打造成全球顶尖的技术软件,我们不仅仅要和国内的开发者社区和基金会合作,还要和国际上先进的开发者社区和基金会合作,让他们愿意参与进来,共创 openEuler 社区。我愿意

2022-07-29 10:11:11

,未来就要看竞争对手的制程技术能否赶得上脚步。 近期高通与台积电持续紧密合作,业界传出在最先进的7纳米制程技术上,台积电因为技术开发领先三星电子(Samsung Electronics),可望拿回高通7

2017-09-22 11:11:12

了高通的订单。之后,中芯国际凭借极具竞争力的价格从Globalfoundries手中夺走了订单,成为高通电源管理芯片的主要合作伙伴。我们知道,在高通的帮助下,中芯国际实现了28nm工艺量产,而且还加快14nm硅片的量产。由于产能、价格及新芯片技术的原因,此次高通将电源管理芯片交给了台积电生产。

2017-09-27 09:13:24

。这场战役两家大厂互有消长,首先是三星的14nm较台积电的16nm抢先半年投入量产,因两家大厂的鳍式晶体管(FinFET)设计也确有雷同之处,后续又衍生了竞业禁止官司诉讼等故事,无论如何,最终台积电还是

2018-06-14 14:25:19

Nano-Proprietary旗下的Applied Nanotech公司与Funai Electric先进应用技术研究所日前宣布,双方将针对一个研究项目进行合作,共同开发基于酶涂层碳纳米

2018-11-19 15:20:44

CPLD技术在PCI总线开关中的应用使用CPLD技术开发PCI板卡有什么优点

2021-04-08 06:47:28

PCB部件使用PI膜作为柔性芯板,并覆盖聚酰亚胺或丙烯酸膜。粘合剂使用低流动性预浸料,最后将这些基材层压在一起以制成刚挠性PCB。刚柔性PCB制造工艺技术的发展趋势:未来,刚柔结合PCB将朝着超薄,高密度

2019-08-20 16:25:23

业界对哪种半导体工艺最适合某一给定应用存在着广泛的争论。虽然某种特殊工艺技术能更好地服务一些应用,但其它工艺技术也有很大的应用空间。像CMOS、BiCMOS、砷化镓(GaAs)、磷化铟(InP

2019-07-05 08:13:58

业界对哪种半导体工艺最适合某一给定应用存在着广泛的争论。虽然某种特殊工艺技术能更好地服务一些应用,但其它工艺技术也有很大的应用空间。像CMOS、BiCMOS、砷化镓(GaAs)、磷化铟(InP

2019-08-20 08:01:20

交给代工厂来开发和交付。台积电是这一阶段的关键先驱。

半导体的第四个时代——开放式创新平台

仔细观察,我们即将回到原点。随着半导体行业的不断成熟,工艺复杂性和设计复杂性开始呈爆炸式增长。工艺技术

2024-03-13 16:52:37

各类常用工艺库台积电,中芯国际,华润上华

2015-12-17 19:52:34

工艺技术的演进遵循摩尔定律,这是这些产品得以上市的主要促成因素。对整个行业来说,从基于大体积平面晶体管向FinFET三维晶体管的过渡是一个重要里程碑。这一过渡促使工艺技术经过了几代的持续演进,并且减小

2019-07-17 06:21:02

如何利用TI DLP Pico 技术开发头戴式显示应用?为什么要选择DLP Pico技术开发HMD应用?

2021-06-01 06:52:55

一半,而性能提高两倍。通过选择一个高性能低功耗的工艺技术,一个覆盖所有产品系列的、统一的、可扩展的架构,以及创新的工具,赛灵思将最大限度地发挥 28 纳米技术的价值, 为客户提供具备 ASIC 级功能

2019-08-09 07:27:00

如何通过软件无线电的架构加速无线技术的开发与测试?如何应对无线标准和技术的快速更新?

2021-05-07 07:05:26

如何提高多层板层压品质在工艺技术

2021-04-25 09:08:11

本帖最后由 华强芯城 于 2023-3-17 09:16 编辑

晶圆代工巨头——台积电近日传出涨价20%的消息,业内轰动。这是台积电继2020年底上涨超10%之后,一年之内,又一次的大幅上涨

2021-09-02 09:44:44

的工艺技术可用于晶圆凸起,每种技术有各自的优缺点。其中金线柱焊接凸点和电解或化学镀金焊接凸点主要用于引脚数较少的封装应用领域包括玻璃覆晶封装、软膜覆晶封装和RF模块。由于这类技术材料成本高、工序

2011-12-01 14:33:02

的小珠子,使其最后形成一个10X5比例的长方形。从这个实验不难看出,要达成这个目标非常不容易,由此可以了解到,各大厂面临的困境有多么艰难。三星和台积电都在完成14 纳米、16 纳米 FinFET 的量产

2016-06-29 14:49:15

的长方形。从这个实验不难看出,要达成这个目标非常不容易,由此可以了解到,各大厂面临的困境有多么艰难。三星和台积电都在完成14 纳米、16 纳米 FinFET 的量产,并以此为资本争夺下一代iPhone

2016-12-16 18:20:11

穿戴电子开发项目,可技术合作共同开发!各位网友大家好,明年是穿戴式电子元年,google glass 年底上市注定会刮起一阵电子穿戴风,穿戴电子市场有很大的发展空间,必定会为合作伙伴带来机会,我们

2013-06-29 17:35:47

,所以只能以旧工艺(16nm制程)制造A10处理器。除此之外,台积电还将独家代工重大变化的2017年版iPhone采用的A11处理器。据称A11芯片将采用10纳米FinFET工艺,最早有望于明年二季度

2016-07-21 17:07:54

生产。如果台积电真的能够完全按照这一时间展开工作的话,那么就将使该公司彻底走在了芯片制造领域的最前端。 目前,业内设备制造厂商大多刚刚开始拥抱14纳米芯片工艺,苹果最新的iPhone 6s系列就是

2016-01-25 09:38:11

请详细叙述腐蚀工艺工段的工艺流程以及整个前道的工艺技术

2011-04-13 18:34:13

中芯国际将45纳米工艺技术延伸至40纳米以及55纳米

上海2009年10月14日电 -- 中芯国际集成电路制造有限公司(“中芯国际”,纽约

2009-10-15 08:22:44 793

793 中芯国际(SMIC)和Cadence 共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

完全集成的能效型流程令快速、轻松地设计低功耗尖端器件成为可能

2009-10-31 07:48:01 1228

1228 中芯国际(SMIC)和Cadence共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

全球电子设计创新领先企业Cadence设计系统公司今天宣布推出一款全面的低功耗设计流程,面向

2009-11-04 17:05:17 589

589 高通携手TSMC,继续28纳米工艺上合作

高通公司(Qualcomm Incorporated)与其专业集成电路制造服务伙伴-TSMC前不久日共同宣布,双方正在28纳米工艺技术进行密切合作。此

2010-01-13 08:59:23 910

910 新思科技与中芯国际合作推出用于中芯65纳米低漏电工艺技术的、获得USB标志认证的DesignWareUSB 2.0 nanoPHY

通过芯片验证的DesignWare PHY IP

2010-05-20 17:39:09 588

588 据外国媒体报道,IBM和ARM计划加强移动电子市场合作的同时,还会共同合作提高14纳米半导体技术。

2011-01-19 08:09:55 330

330 中国顶尖IC设计公司已经采用了28纳米尖端技术开发芯片,而9.2% 本地无晶圆厂半导体公司亦采用先进的45纳米或以下的工艺技术进行设计及大规模量产。

2011-09-07 11:23:50 1556

1556 中国顶尖设计公司已经采用28纳米尖端技术开发芯片,而本地9.2%无晶圆厂半导体公司亦采用先进的45纳米或以下的工艺技术进行设计及大规模量产

2011-09-13 09:00:40 3212

3212 Crocus科技和中芯国际正式签署合作技术开发和晶圆制造协议。共同研发高温MLU的应用技术。

2011-12-09 19:04:21 637

637 Cadence与三星的合作为移动消费电子产品带来了新的工艺进展,使得20纳米及未来工艺节点设计成为可能。

2012-06-10 10:43:54 984

984 随着芯片微缩,开发先进工艺技术的成本也越来越高。TSMC对外发言人孙又文表示,台积电会继续先进工艺技术节点的投入和开发,今年年底台积电将推出20nm工艺

2012-08-30 14:34:30 1782

1782 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909 该14纳米产品体系与芯片是ARM、Cadence与IBM之间在14纳米及以上高级工艺节点上开发系统级芯片(SoC)多年努力的重要里程碑。使用FinFET技术以14纳米标准设计的SoC能够大幅降低功耗。 这

2012-11-16 14:35:55 1270

1270 新思科技公司日前宣布:该公司与三星在FinFET技术上的多年合作已经实现了一个关键性的里程碑,即采用三星的14LPE工艺成功实现了首款测试芯片的流片

2013-01-09 12:11:31 1062

1062 ,采用台积公司先进的16纳米FinFET (16FinFET)工艺打造拥有最快上市、最高性能优势的FPGA器件。

2013-05-29 18:21:14 869

869 日前,联华电子与SuVolta公司宣布联合开发28纳米工艺技术,该工艺将SuVolta的SuVolta的Deeply Depleted Channel晶体管技术集成到联华电子的28纳米High-K/Metal Gate高效能移动工艺。

2013-07-25 10:10:52 1049

1049 全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字技术交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence ® Encounter® 数字技术交付出55纳米平台的参考设计流程。

2013-08-16 12:02:40 1445

1445 益华电脑宣布,晶圆代工业者GLOBALFOUNDRIES已经认证Cadence实体验证系统适用于65nm至14nm FinFET制程技术的客制/类比、数位与混合讯号设计实体signoff。同时

2014-03-25 09:33:50 862

862 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,立即推出基于台积电16纳米FinFET制程的DDR4 PHY IP(知识产权)。

2014-05-21 09:44:54 1769

1769 全球知名电子设计创新领先公司Cadence设计系统公司 (NASDAQ: CDNS),今日宣布台积电采用了Cadence®16纳米FinFET单元库特性分析解决方案。

2014-10-08 19:03:22 1594

1594 设计参考手册(Design Rule Manual,DRM) 与SPICE认证,相比于原16纳米FinFET制程,可以使系统和芯片公司通过此新工艺在同等功耗下获得15%的速度提升、或者在同等速度下省电30%。

2014-10-08 19:10:45 663

663 美国加州圣何塞(2014年9月26日)-全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。

2014-10-08 19:19:22 919

919 三星于2015年第一季度发布了半导体芯片行业首款采用14nmLPE (Low-Power Early) 工艺量产的Exynos 7 Octa处理器,成为FinFET逻辑制程上的行业引领者。

2016-01-15 17:12:47 927

927 2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1026

1026 2016年5月19日,北京讯——ARM今日发布了首款采用台积电公司(TSMC)10纳米FinFET工艺技术的多核 64位 ARM®v8-A 处理器测试芯片。仿真基准检验结果显示,相较于目前常用于多款顶尖智能手机计算芯片的16纳米FinFET+工艺技术,此测试芯片展现更佳运算能力与功耗表现。

2016-05-19 16:41:50 662

662 确保连续四代全可编程技术及多节点扩展的领先优势四代先进工艺技术和3D IC以及第四代FinFET技术合作 2015年5月28日, 中国北京 - All Programmable 技术和器件的全球领先

2017-02-09 03:48:04 198

198 2017年4月18日,中国上海 – 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日正式发布针对7nm工艺的全新Virtuoso® 先进工艺节点平台。通过与采用7nm FinFET

2017-04-18 11:09:49 1165

1165 三星10纳米工艺技术公告:全球领先的三星电子先进的半导体元器件技术正式宣布,其第二代10纳米(nm)FinFET工艺技术,10LPP(Low Power Plus)已经合格并准备就绪用于批量生产。

2017-05-03 01:00:11 580

580 2017年6月2日,上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS) 今日宣布其数字、签核与定制/模拟工具成功在三星电子公司7LPP和8LPP工艺技术上实现。较前代高阶工艺

2017-06-02 16:04:34 1237

1237 赛灵思、Arm、Cadence和台积公司今日宣布一项合作,将共同构建首款基于台积7纳米FinFET工艺的支持芯片间缓存一致性(CCIX)的加速器测试芯片,并计划在2018年交付

2017-09-23 10:32:12 4003

4003 Technology (12FFC) 和最新版本 7nm FinFET Plus 工艺的认证。Nitro-SoCTM 布局和布线系统也通过了认证,可以支持 TSMC 的 12FFC 工艺技术。

2017-10-11 11:13:42 2372

2372 在2011年初,英特尔公司推出了商业化的FinFET,使用在其22纳米节点的工艺上[3]。从IntelCorei7-3770之后的22纳米的处理器均使用了FinFET技术。由于FinFET具有

2018-07-18 13:49:00 119524

119524

楷登电子(美国 Cadence 公司)今日正式公布其与台湾积体电路制造股份有限公司(TSMC)全新12nm FinFET紧凑型(12FFC)工艺技术开发的合作内容。凭借Cadence 数字

2018-05-08 11:07:00 1422

1422 Synopsys设计平台用于高性能、高密度芯片设计 重点: Synopsys设计平台获得TSMC工艺认证,支持高性能7-nm FinFET Plus工艺技术,已成功用于客户的多个设计项目。 针对

2018-05-17 06:59:00 4461

4461 中芯国际14纳米FinFET技术获得重大进展 8月9日,中芯国际公布了在14纳米FinFET技术开发上获得的重大进展。第一代FinFET技术研发已进入客户导入阶段。除了28纳米PolySiON和HKC,28纳米HKC+技术开发也已完成。28纳米HKC持续上量,良率达到业界水平。

2018-08-18 10:31:00 3773

3773 外,在技术研发方面,中芯国际表示,第一代 FinFET 14 纳米技术进入客户验证阶段,产品可靠度与良率已进一步提升。同时,12 纳米的技术开发也开始有所突破。

2019-02-18 17:03:10 3076

3076

4月16日,三星官网发布新闻稿,宣布已经完成5纳米FinFET工艺技术开发,现已准备好向客户提供样品。

2019-04-16 17:27:23 3008

3008 UltraScale+ 器件系列以低功耗半导体工艺(TSMC 16 纳米FinFET+)为基础,与 7 系列 FPGA 及 SoC 相比,能将整体器件级电源节省达 60%。架构改进。

2019-08-01 15:46:33 1252

1252 目前从全球范围来说,也就只有台积电和三星这两家能做到5纳米工艺以下了。6月29日晚间,据外媒报道,三星宣布其基于栅极环绕型 (Gate-all-around,GAA) 晶体管架构的3nm工艺技术已经

2021-07-02 11:21:54 2254

2254 Cadence 和 TSMC 联手进行 N3 和 N4 工艺技术合作, 加速赋能移动、人工智能和超大规模计算创新 双方共同客户现可广泛使用已经认证的 N3 和 N4 流程 PDK 进行设计 完整

2021-10-26 15:10:58 1928

1928 工艺技术的FINFLEX架构认证 此外,该认证也可扩展到台积电N4工艺技术 Ansys宣布Ansys电源完整性解决方案荣获台积电FINFLEX创新架构以及N4工艺技术认证,持续深化与台积电的长期技术合作

2022-11-17 15:31:57 696

696 来源:Cadence楷登 2023年4月26日,楷登电子近日宣布基于台积电 3nm(N3E)工艺技术的 Cadence® 16G UCIe™ 2.5D 先进封装 IP 成功流片。该 IP 采用

2023-04-27 16:35:40 453

453

,包括最新的 N3E 和 N2 工艺技术。这一新的生成式设计迁移流程由 Cadence 和台积电共同开发,旨在实现定制和模拟 IC 设计在台积电工艺技术之间的自动迁移。与人工迁移相比,已使用该流程的客户成功地将迁移时间缩短了 2.5 倍。

2023-05-06 15:02:15 801

801 恩智浦和台积电联合开发采用台积电16纳米FinFET技术的嵌入式MRAM IP 借助MRAM,汽车厂商可以更高效地推出新功能,加速OTA升级,消除量产瓶颈 恩智浦计划于2025年初推出采用该技术

2023-05-26 20:15:02 396

396 流程现已通过 Intel 16 FinFET 工艺技术认证,其 Design IP 现可支持 Intel Foundry Services(IFS)的此工艺节点。 与此同时,Cadence 和 Intel 共同发布

2023-07-14 12:50:02 381

381

Cadence近日宣布,其数字和定制/模拟流程在Intel的18A工艺技术上成功通过认证。这一里程碑式的成就意味着Cadence的设计IP将全面支持Intel的代工厂在这一关键节点上的工作,并提

2024-02-27 14:02:18 160

160

正在加载...

电子发烧友App

电子发烧友App

评论