Cadence设计系统公司公布一个新版的尖端功能验证平台与方法学,拥有全套最新增强功能,与之前发布的版本相比,可将SoC验证效率提高一倍。 Incisive ®12.2提供了两倍性能,全新Incisive调试分析器产品,全新低功耗建模,以及当今复杂IP与SoC高效验证所需的数百种其他功能。

2013-01-27 10:44:38 1437

1437

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,该版本将复杂SoC的低功耗验证效率提高了30

2013-05-14 10:31:40 1832

1832 Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

解决方案的基础,通过集成的散热、功率消耗和静态时序分析功能,为客户提供系统驱动的功率、性能和面积 (PPA),用于单个小芯片。 Cadence® Integrity™ 3D-IC 平台是业界首个综合性

2021-10-14 11:19:57

%, 使用户得以更快、更有预见性地创建产品。同时,新型信号集成流引入了更高层次的自动化水平,使得快速设计所需要的预布线拓扑、约束开发和发展的性能导向数字电路模拟具有了更好的可用性和生产率。在新版本的发布会

2012-12-18 10:18:07

及属性提供了位置。 提升的生产率和仿真精确性 新发布的Allegro平台在Allegro PCB SI 及PCB PI中提供了新的功能,可缩短互连设计时间并提升产品性能和可靠性。这些性能包括了串行

2018-08-28 15:28:45

和解决这些不断增加的复杂度难题的流程和方法学,从而树立了全新PCB设计典范。 “新的Allegro平台版本引入了很多新的生产率特性,将为象我一样的设计师带来优势,”加拿大Kaleidescape高级

2008-06-19 09:36:24

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如

2019-10-11 07:07:07

SoC验证超越了常规逻辑仿真,但用于加速SoC验证的广泛应用的三种备选方法不但面临可靠性问题,而且难以进行权衡。而且,最重要的问题还在于硬件加速访问权限、时机及其稳定性。

2019-11-11 06:37:11

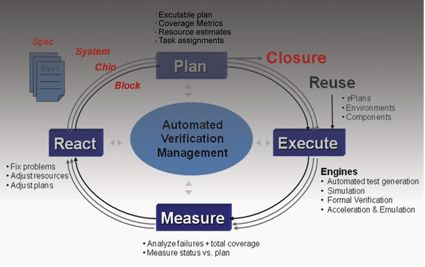

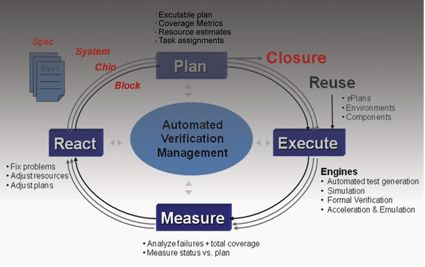

由于片上系统(SoC)设计变得越来越复杂,验证面临着巨大的挑战。大型团队不断利用更多资源来寻求最高效的方法,从而将新的方法学与验证整合在一起,并最终将设计与验证整合在一起。虽然我们知道实现验证计划

2019-07-11 07:35:58

由于skill 语言提供编程接口甚至与<br/>C 语言的接口所以可以以Cadence 为平台进行扩展用户还可以开发自己的<br/>

2008-07-12 23:11:21

联合开发,以促进真正的 SystemVerilog 与标准库和经过验证的方法的互操作性。它完全开放,结合了 Cadence® Incisive® Plan-to-Closure Universal

2022-02-13 17:03:49

EMC新标准,EN12895-2013新

2015-11-30 13:26:39

未来的FPGA,将会采用创新的迭堆式封装(SIP),即在一个封装里放多个裸片的技术,到那时,FPGA将成为一个标准的、虚拟的SoC平台来应用。” 半导体行业最让人称道的是,能把沙子做成比金子还要贵

2019-07-17 07:08:07

(scoreboard,也被称为 checker,本书统一以scoreboard来称呼)。既然是判断,那么牵扯到两个方面:一是判断什么,需要把什么拿来判断,这里很明显 是DUT的输出;二是判断的标准是什么。验证平台要收集

2020-12-02 15:21:34

DN206-LTC1702 / LTC1703开关稳压器控制器为瞬态响应设定了新标准

2019-07-15 08:15:22

平台下注册。所有先前颁发的能效证书/标签的型号将在第SASO 2927号标准实施之日到期(2020年8月31日)。因此,所有申请人的平台上升级的道路照明产品为标准号SASO 2927,以完成要求

2021-04-30 14:12:45

全速ASIC/ASSP验证平台的核心。 HAPS-51系统采用模块化的可延伸架构,提供了专为满足SoC设计人员和软件开发人员需求而设计的多种有效功能与特性。与所有HAPS系统一样,HAPS-51也采用

2018-11-20 15:49:49

机的协商,保持接口参数同步;数据通道验证在该接口参数下的功能和性能,实现了接口的功能和性能验证的自动化,大大提高了测试效率,保证测试用例的覆盖率。该工具适用于多种平台下的UART和SPI接口验证。0

2019-06-21 05:00:09

USB PD 的最新标准是2.0还是3.0? 具体标准是什么?据说苹果笔记本不接受9V和12V的输入,这是什么原因呢?它的充电器是PD2.0的吗如果一个电源适配器和移动电源只支持5V/1A

2016-05-30 18:20:33

USB Type-C™、USB PD 和 USB 3.1 第 2 代:速度和功率的新标准

2021-01-21 06:01:47

随着现代集成电路技术的发展,尤其是IP的大量使用,芯片的规模越来越大,系统功能越来越复杂,普通的EDA和FPGA仿真在速度和性能上已经无法胜任芯片仿真验证的要求,功能验证已经成为大规模芯片设计的一个

2010-05-28 13:41:35

表面不受雨水、咸水、油或冰的影响。 营销总监Ian Cro***y评论:“Zytronic已为触控性能设定了新标准,使传感器能够在工业环境(先前不能运行的工业环境)下可靠地运行。尽管在强电磁干扰

2018-09-25 11:20:50

小编前段时间帮客户找到一些人解决了SOC验证环境的问题。在招人的时候我们和不少人进行了沟通交流,从中发现SOC验证环境一千家公司有一千家公司的做法。那么一个优秀的SOC验证环境应该具备哪些功能呢

2022-05-31 11:39:18

随着系统芯片(SoC)设计的体积与复杂度持续升高,验证作业变成了瓶颈:占了整个SoC研发过程中70%的时间。因此,任何能够降低验证成本并能更早实现验证sign-off的方法都是众人的注目焦点。

2019-08-26 07:06:04

制化FPGA原型板验证效率的创新方法,自动化现有的电路仿真(in-circuit emulation)侦错功能,并提供更高的FPGA能见度。这个以FPGA为基础的SoC验证平台对工研院而言是前景看好

2011-07-24 09:47:50

专家您好! 想请教一下ADPD105 / 108在生产验证阶段,要如何验证芯片有无问题?像是G-sensor都会订有容许的误差标准(例如:+/- 0.1G)之类的~~ ADPD105 / 108有这

2018-07-31 08:45:30

验证,通常我们在设计的时候,会将厂家要求的标准提高一些来做。后端设计:可以理解为将电路从器件符号形式转为几何图形形式,以指导掩膜版的设计。然后,我把设计流程里各个环节能用且好用的软件列一下(可以看到

2020-06-14 08:01:07

SoC原型的Handel-C描述及其实现流程是怎样的?利用RC1000和SoC设计展示评估平台RC200搭建一个原型验证系统的样机?

2021-05-28 06:15:18

SoC设计的特点软硬件协同设计流程基于标准单元的SoC芯片设计流程

2021-01-26 06:45:40

导航系统SoC芯片设计的要求有什么?如何构建基于LEON开源软核的SoC平台?

2021-05-27 06:18:16

的,因为一旦你做到,就可以金石为开。”事实上,设计和验证SoC并非易事。一个原因源于选择和灵活性,凡事有利必有弊,组装芯片也如此。例如,就ARM而言,企业既可购买由英国公司设计的现成处理器,也可自己构建运行

2017-04-05 14:17:46

2018年4月,IEC TC61公布新标准IEC60335-2-114使用碱性或其他非酸性点解质电池的自平衡个人运输装置的安全要求。该标准的颁布使得在市场销售已久的自平衡车有了完整的电气安全检测依据

2018-10-17 15:23:29

怎样去修改RK3288平台HDMI默认的显示分辨率呢?如何去实现呢?

2022-03-03 08:37:52

SoC系统验证平台总体框架是怎样的?SoC系统验证平台如何去构建?

2021-04-28 07:13:41

焊台温度设定的基本原则: 在不影响焊接质量及焊接速度的前提下,焊接设定温度越低越好。 主要考虑因素: 焊料的熔点 PCB板时间曲线图 元器件耐热温度时间曲线图 生产效率 焊盘与PCB连接的粘胶耐热

2010-08-26 19:41:17

小得多,因此大多数工程师对这些测试台感到满意。 几年过去了,设计变得更大更复杂,使用主要用于设计的 HDL 编写测试平台将无助于验证具有更高门密度的电路,EDA 行业意识到旧的定向测试方法无法扩展

2022-02-16 13:36:53

讲述背提包和旅行箱及其配件的新标准 新的《背提包》标准是对QB/T1333-96《背提包》的修订。新标准主要对原版本做了以下修订:对织物面料背提包数量增加的市场需求,增加织物面料背提包要求。技术要求

2013-04-12 16:48:14

请问D1平台tina的kernel和标准的5.4kernel有哪些区别?改动大吗?

2021-12-28 07:12:23

。这是双方工程团队为进一步提升良率、增强可靠性并缩短生产周期而努力合作的成果。Virtex-6系列通过生产验证,意味着联华电【关键词】:生产验证,高性能,电子,可靠性,生产周期,系列,制造工艺,生产

2010-04-24 09:06:05

常年使用一种 EDA 工具显然可以提高效率,同时也会让您习惯于自己所用的 PCB 设计工具,接受该工具的所有优缺点。不过,随着当今技术的快速发展,我们需要考虑做出改变,继而引入最新的技术方法。本文经 PCB 设计杂志授权翻印,其中讨论了阻碍 PCB 设计流程的生产率问题。

2019-10-14 06:27:31

高空作业属于特种行业,安全性尤为重要,一般国内优质的高空作业平台都会通过欧盟CE认证,如果是载人从三米的高度降落跌落危险的话,这个高空平台也是危险机械,如果载物就是普通机械,会根据不同的标准进行CE

2015-09-10 10:57:31

近几年来,SoC 技术已经得到了迅速的发展,随之而来的是 SoC 设计的验证也变得更加复杂,花费的时间和人力成倍增加。一个SoC 芯片的验证可能会用到多种验证技术,常用的 SoC 的

2009-08-31 10:33:25 24

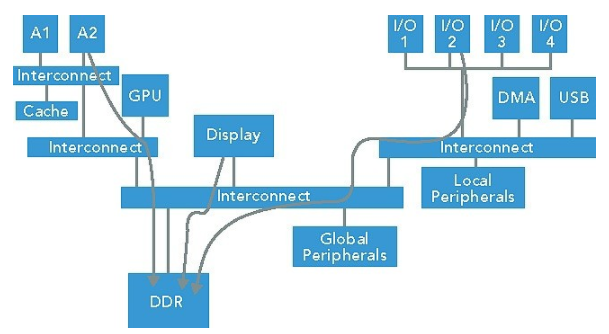

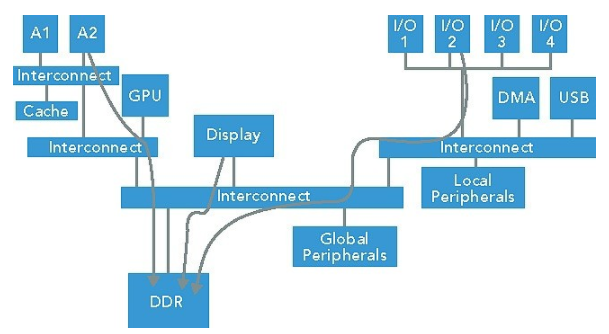

24 本文描述了SOC平台体系结构之低功耗高性能的数字信号处理的应用。这个平台是基于AMBA SOC总线协议,它结合了新颖的互连规范,为了能让高性能的DSP IP核集成到SOC平台中,这个规范

2010-02-01 13:58:40 14

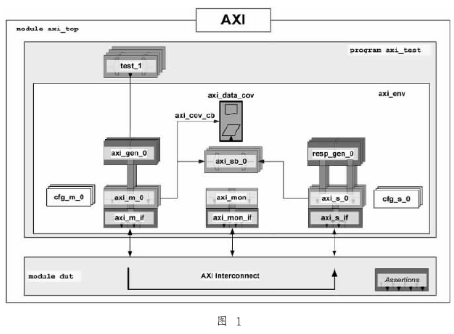

14 本文介绍了基于事务的SoC验证方法,详细说明了事务、事务处理器的概念和事务级验证平台的功能结构。Synopsys公司的RVM验证方法学是当前比较流行的基于事务的SoC验证方法,文中详细

2010-02-24 11:44:04 8

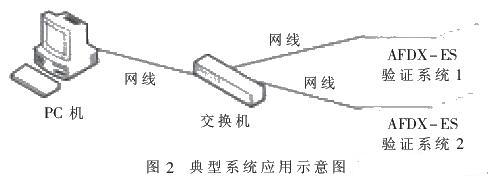

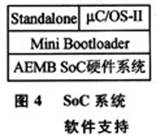

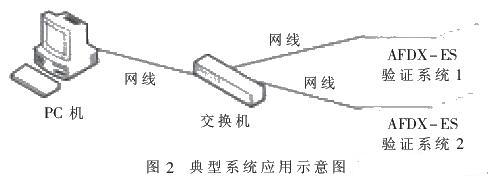

8 以SoC软硬件协同设计方法学及验证方法学为指导,系统介绍了以ARM9为核心的AFDX-ES SoC设计过程中,软硬件协同设计和验证平台的构建过程及具体实施。应用实践表明该平台具有良

2010-11-22 15:18:52 56

56 Cadence推出首个TLM驱动式设计与验证解决方案

Cadence设计系统公司今天推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽享事务级建模(TLM)的好处。

2009-08-07 07:32:00 674

674 Cadence推出首个TLM驱动式设计与验证解决方案提升基于RTL流程的开发效率

Cadence设计系统公司推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽

2009-08-11 09:12:18 499

499

电池国家最新标准发布公告

2009-11-02 15:55:24 870

870 Cadence为PCI Express 3.0推出首款验证解决方案

Cadence设计系统公司宣布其已经开发了基于开放验证方法学(OVM)的验证IP(VIP)帮助开发者应用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 设计与验证复杂SoC中可综合的模拟及射频模型

设计用于SoC集成的复杂模拟及射频模块是一项艰巨任务。本文介绍的采用基于性能指标规格来优化设计(如PLL或ADC等)的方

2009-12-26 14:38:13 557

557

GF、ARM共同定义行动技术平台新标准

GLOBALFOUNDRIES与ARM日前于2010 MWC中,公布针对新一代无线产品及应用开发的尖端系统单芯片(SoC)平台全新细节资料。全新的芯片生产制

2010-02-26 08:55:44 575

575 GF、ARM共同定义行动技术平台新标准

GLOBALFOUNDRIES与ARM日前于2010 MWC中,公布针对新一代无线产品及应用开发的尖端系统单芯片(SoC)平台全新细节资料。全新的芯片生产制

2010-02-26 08:59:40 472

472 芯邦采用Cadence Incisive Xtreme III系统提升SoC验证实效

全球电子设计创新领先企业Cadence设计系统公司今天宣布,位于中国深圳的、无晶圆厂集成电路设计领先企业芯邦科

2010-03-02 10:32:47 573

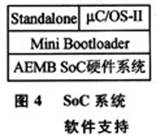

573 AEMB软核处理器设计的SoC系统验证平台

本文采用OpenCores组织所发布的32位微处理器AEMB作为SoC系统的控制中心,通过Wishbone总线互联规范将OpenCores组织

2010-05-24 11:02:58 802

802

电池辅助无源RFID平台新标准

Intelleflex是功能增强型RFID( Extened Capability RFID) 平台的领军企业,近期宣布推出新一代、标准化电池辅助无源XC3技术平台

2010-05-24 11:22:40 529

529 全球电子设计创新领先企业Cadence设计系统公司,今天宣布了业界最全面的用于系统级芯片(SoC)验证的通用验证方法学(UVM)开源参考流程。为了配合Cadence EDA360中SoC实现能力的策略,

2010-06-28 08:29:14 2240

2240 摘 要: 以SoC软硬件协同设计方法学及验证方法学为指导,系统介绍了以ARM9为核心的AFDX-ES SoC设计过程中,软硬件协同设计和验证平台的构建过程及具体实施。应用实践表明该

2010-12-08 10:44:41 1027

1027

Cadence设计系统公司600多种新功能扩展了指标驱动型验证(MDV)的范围,帮助工程师实现更快、更全面的验证闭合与硅实现。

2011-01-13 11:26:17 768

768 Cadence Incisive Conformal ASIC是Incisive验证平台等效检查解决方案的一部分,设计者无需测试向量就能验证和调试数百万门的设计。它组合了业界最优的等效检查工具和扩展功能检查,数据路

2011-04-13 23:40:45 17

17 电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,中国科学院计算技术研究所(简称计算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系统,来加速其下一代6400万门以上龙芯3号高级多

2011-05-27 10:49:34 646

646 芯片验证的工作量约占整个芯片研发的70%,已然成为缩短芯片上市时间的瓶颈。应用OVM方法学搭建SoC设计中的DMA IP验证平台,可有效提高验证效率。

2012-06-20 09:03:29 2627

2627 随着芯片设计技术的快速发展,基于SoC的开发平台已成为IC设计业界的热点,对SoC应用设计平台需求越来越多,同时对其性能要求也越来越高。因此本文提出了一种基于LEON3的精简的,灵

2013-03-13 16:29:19 54

54 光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

2013-07-09 15:53:24 769

769 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 842

842 彻底地验证其片上系统(SoC)是否符合HDMI 2.0规范,从而加速批量生产的准备时间。这款用于HDMI 2.0的Cadence VIP支持各种主流逻辑模拟器、验证语言及包括UVM(Universal Verification Methodology)在内的方法学。

2013-09-27 16:19:08 857

857 Workbench搭配Cadence Interconnect Validator,组成了一套完整的功能验证与性能检验解决方案。

2013-11-07 09:34:14 1130

1130 ) 通过采用Cadence®完整的工具流程,已成功完成该公司最大型的SoC (系统单芯片) 项目开发,该项目是用于4G基站的3亿门芯片设计。通过在其分层式 (hierarchical) 设计流程中部

2013-11-19 10:30:13 886

886 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,海思半导体(HiSilicon Semi)进一步扩大采用Cadence® Palladium® XP 验证运算平台作为其仿真方案,运用于移动和数字媒体System-on-Chip (SoC) 与 ASIC开发。

2014-05-13 16:19:03 2137

2137 SoC基于IP设计的特点使验证项目中多语言VIP(Verification IP)协同验证的需求不断增加,给验证工作带来了很大的挑战。为了解决多语言VIP在SoC验证环境灵活重用的问题。提出了一种

2015-12-31 09:25:13 12

12 ™ 可以显著缩短片上系统(SoC)面市时间。较Cadence上一代仿真平台,Xcelium™ 单核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。

2017-03-01 15:57:05 3341

3341 2017年3月2日,上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日发布全新基于FPGA的Protium™ S1原型验证平台。借由创新的实现算法,平台可显著提高工程生产

2017-03-02 11:13:11 2744

2744 设计了一种基于FPGA的验证平台及有效的SoC验证方法,介绍了此FPGA验证软硬件平台及软硬件协同验证架构,讨论和分析了利用FPGA软硬件协同系统验证SoC系统的过程和方法。利用此软硬件协同验证

2017-11-17 03:06:01 13138

13138

为了充分利用系统级芯片(SoC)设计带来的优点,业界需要一种可以扩展的验证解决方案,解决设计周期中各个阶段的问题,缩短验证鸿沟。本文将探讨可扩展验证解决方案为何能够以及如何解决SoC设计目前面临的功能方面的严峻挑战,以达到提高设计生产力、保证设计质量、缩短产品上市时间以及提高投资回报率的目的。

2018-06-04 03:13:00 743

743

参加本研讨会可了解 PADS VX 版如何提高全流程的设计生产率。

2019-05-20 06:10:00 1964

1964

增强功能为成像和计算机视觉基准设定了新标准,与Tensilica Vision P5 DSP相比,性能提高了4倍。

2019-08-07 11:05:27 5902

5902 SAN JOSE - Cadence Design Systems Inc.今天宣布推出基于块的设计(BBD)和基于平台的设计(PBD) )方法和工具流向苏格兰的阿尔巴中心。 BBD和PBD是用于片上系统(SoC)开发的一套完全编码和验证的设计方法。

2019-08-13 09:03:45 1273

1273 在上周发布iOS 13.2.2正式版之后,苹果今日停止了对iOS 13.2的验证,这意味着用户无法再降级到iOS 13.2。

2019-11-15 15:46:07 2438

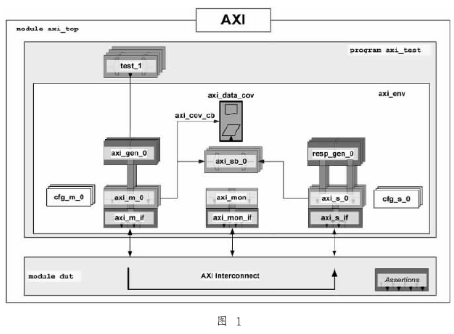

2438 本文以软件工程的视角切入,分析中科院计算所某片上系统(SoC)项目的验证平台,同时也介绍当前较为流行的验证方法,即以专门的验汪语言结合商用的验证模型,快速建立测试平台(test-bench)并在今后的项目中重用(reuse)之。

2020-04-10 09:23:23 1151

1151

传感器应用来自传感器专家Micro-Epsilon的optoNCDT 1220、1320和1420激光三角测量传感器为位移和距离测量设定了新标准。这些小巧、智能、精确的传感器具有微型光斑尺寸,可以

2020-09-22 15:29:32 2533

2533 Cadence Palladium Z1 企业级仿真平台和 Cadence Protium X1 企业级原型验证平台来实现硬件仿真和原型验证。

2021-03-19 09:37:06 2003

2003 ,已成为验证进程管理的棘手问题。本文主要跟小伙伴们聊一聊智能跟踪SoC验证进度的方法。 EDA工具两大巨头Synopsys和Cadence都有自己的验证计划工具,分别是Synopsys公司

2021-03-28 10:52:02 3292

3292

SoC设计中的验证技术有哪些。

2021-03-29 10:37:30 12

12 Cadence拥有最完整的IP与SoC验证、硬件与软件回归测试及早期软件开发的全系列解决方案。

2021-04-06 13:48:53 2431

2431 历时4月,可支持18亿门SoC全芯片验证的英诺达硬件验证云平台成都中心一期成功实现满载运行,圆满达成云平台一期运营所有目标!英诺达的云平台,不同于传统的IDC机房,机器要求高、运营复杂、专业要求极高

2021-12-17 13:54:49 1771

1771 中国上海,2022年4月21日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence® Fidelity™ CFD 软件平台,为多物理场仿真的性能和准确度开创新时代。

2022-04-21 11:36:50 1955

1955 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 种新的验证 IP(VIP)解决方案,助力工程师迅速有效地验证设计,以满足最新标准协议的要求。

2022-06-06 11:18:21 2665

2665 面对持续不断的上市时间压力和日益复杂的 SoC 设计,很难找到不想从设计周期中缩短时间的工程师。特别是在高级节点,验证 SoC 互连已成为一个耗时的步骤。但是,工具现在可以高效且有效地执行周期精确的性能分析和互连验证。

2022-06-14 10:12:17 1692

1692

的验证 IP(VIP)和系统级 VIP(系统 VIP),以加速新技术的采用。Cadence CXL 3.0 VIP与 Cadence PCI Express(PCIe)6.0 VIP 集成,提供了从 IP 到系统级芯片(SoC)的完整解决方案,助力用户成功设计高性能数据中心应用。

2022-08-10 10:14:50 1781

1781 设定新标准:高清音频正在改变着我们的收听方式

2022-11-03 08:04:38 0

0 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞萨电子(Renesas Electronics)已采用全新的人工智能(AI)驱动的 Cadence Verisium 验证

2023-03-15 09:07:00 539

539 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩大与台积电和微软的合作,致力于加快千兆级规模数字设计的物理验证。通过此次最新合作,客户可以在带有 Cadence

2023-04-26 18:05:45 710

710 了 Cadence 在面对 SoC 设计验证挑战下的应对之法。 随着 SoC 设计的发展,如何在有限的时间内尽可能发现更多的 bug 和实现更多的溯源分析,让项目各方面的投资都做到物尽其用,这是验证工作所面临

2023-06-07 00:20:03 466

466

内容提要 ● Cadence Integrity 3D-IC 平台现已全面支持最新版 3Dblox 2.0 标准,涵盖 TSMC 的 3DFabric 产品 ● Integrity 3D-IC

2023-10-08 15:55:01 249

249 双方的共同客户可获取 Cadence 的全流程系统级设计验证和实现解决方案以及接口 IP,依托 Neoverse CSS 加速开发基于 Arm 的定制 SoC 中国上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

电子发烧友App

电子发烧友App

评论