2022年4月20日,中国苏州讯 —— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。 华邦的 1.35V DDR3 产品在 x8

2022-04-20 16:04:03 2554

2554

时钟接口有两个时钟给DDR3控制器,一个时钟是DDR3控制器的工作时钟,一个是给DDR3的I/O接口。DDR3控制器的时钟不可超过DSP的1/2,I/O接口的时钟是DDR3的内存时钟。2.2. 信号

2018-01-18 22:04:33

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

在调试335x的DDR3时,用的是CCS,非操作系统调试。

按TI给的AM335x——StarterKit.gel,这个文件导入到CCS,debug的时候,DDR3可以驱动,读写正常。按

2018-06-21 10:59:20

附件为DDR3走线主要的规则介绍,有兴趣的朋友可以下载看看,老手就不用了~

2019-03-08 20:37:44

DDR3不是GDDR3 细说GDDR3显存认识误区 最近看到很多关于显卡显存规格的文章.很多的文章和说明都将显卡的显存GDDR3与DDR3规格认为是一种显存规格,而且很多人的理解是GDDR3就是

2011-02-23 15:27:51

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:53:43

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-03-12 16:05:56

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条,笔记本

2009-08-17 22:58:49

概述: JS-9300A内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测

2009-03-13 15:46:57

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:50:27

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:55:45

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条,笔记本

2009-08-17 23:00:19

对电路设计的优化包括降低信号反射、过冲,确定匹配电阻的大小、走线阻抗等,通过对无源器件的各种配置分析选取出最适合的参数配置。 图1时钟线的拓扑结构(点击查看大图) (1)DDR3总线的差分时钟分析

2014-12-15 14:17:46

通过DDR3内存名MT41J128M16-16Meg*16*8Banks通过命名怎样算出内存的大小?

2017-06-15 21:19:11

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16组成。 DDR3数据速率为1600Mbps,因此我必须在HP BANK中使用VRN

2020-07-21 14:47:06

各位朋友有没有遇到过DDR3 Vref 信号上100nF滤波电容失效的情况?我们板子用到了2颗DDR3芯片,VREFCA和VREFDQ管脚各自通过两个10K电阻分压得到0.76V。主芯片上还有一个MEM_VREF管脚也是通过两个1K电阻分压得到0.76V。

2019-02-19 10:41:35

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

共享交流一下,DDR3布线技巧

2016-01-08 08:17:53

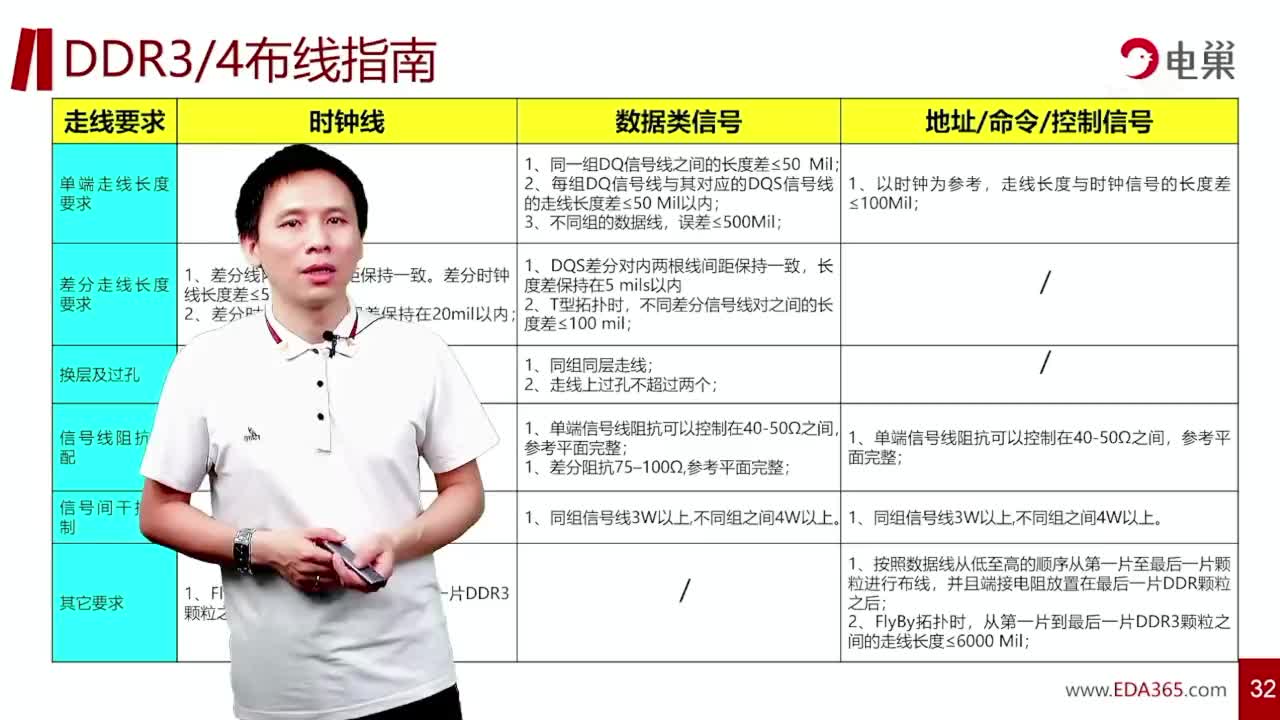

这篇帖子跟大家一起来讨论下DDR3布线的那些事:DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间

2016-10-28 10:25:21

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

)GROUP F 中 CLK、CLKn 差分对的线长误差控制在 5mil 以内;CLK/CLKn 不能短于任意一组 DATA/DM/DQS。3.走线规则1)DDR3 的信号走线必须有完整参考面,以保证

2019-09-20 09:05:04

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 编辑

各位好!关于DDR3,之前有小结过如果进行DDR3的SW leveling和进行EMIF4寄存器的配置。但是调试时,如果进行DDR3的问题定位,现小结一下,附上相关文档。如有相关问题,可在楼下跟帖讨论。谢谢!

2018-06-21 04:01:01

DDR 走线,可以借鉴!

2020-09-15 19:03:17

有些方案的DDR布线要求是不要走蛇形线,请问下这是为什么要这样要求? 走蛇形线有什么影响吗? 谢谢!

2022-11-29 11:52:06

[size=14.3999996185303px]我有个ARM的板子,DDR2和NAND的数据线是复用的,这样PCB走线的时候,除了原来DDR2高速信号走线阻抗和等长以外,还需要特别注意什么吗。NAND的线长是不是不算入DDR2总的线长中。

2016-10-10 17:09:28

1/ DDR2/ DDR3。DDR4预计在2015年将成为消费类电子的主要设计,随着DDR信号速率的不断提高,在DDR4设计中特别是DQ和DQS之间传输时延对设计者提出更高的挑战。在PCB设计的时候为了时序

2014-10-21 09:54:56

多大?6:如果空间不足的情况下,地址跟地址的间距最小可以做多少,数据与数据间距可以做多少?地址可以跟数据走同一层吗?7:以上的等长情况在频率,控制芯片,ddr颗粒不同的情况下,同样适用吗?8:关于ddr3

2015-01-06 15:34:50

大家好,我刚刚接触AM3359,板子在DDR3的调试中,遇到了一个问题,希望得到大家的帮助。

DDR3的参数设置中,有两个参数很是奇怪,一个是EMIF_SDCFG,这个参数有没有办法在不使用CCS

2018-05-15 05:49:26

我是一名labview FPGA程序员,使用的是NI 7975 fpga模块,它具有kintex 7 fpga。该模块具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga资源。数据应该从芯片到芯片之间会有多少延迟?这是DDR3 DRAM双端口(同时读写操作可能??)???

2020-05-20 14:42:11

大家好!

我刚刚买了TMDSEVM6678L开发套件,这款套件应该有512MB的DDR3 SDRAM,从图上看,有5块芯片组成这512MB的DDR3,但是我的板子上DDR3部分只有4块芯片,请教一下各位是我的板子少了一块芯片还是这4块芯片容量比5块的要大,所以总量还是512MB呢?

谢谢!

2018-06-24 05:29:03

自己画的6657的板,发现DDR3初始化有问题,初始化参数是按照芯片手册来设置的,写数据进去会出错。初步怀疑是DDR3布线问题,请问TI的大神们,6657对DDR3的布线有什么具体的要求吗?或者是

2018-06-21 05:42:03

两旁大容量DDR3,是否有建议参考的型号?

开发板的DDR3是菊花链拓扑布线吧,能否用2片DDR3,走类似AM3517这样的 T形拓扑?

一般来说 DDR3多片,走T行的话, 800MHz以上会有问题。 而菊花链更好。

2018-06-21 11:19:34

等长解析(1/2/4片)5、DDR、DDR2、DDR3、DDR4区别与联系6、你问我答10个关于DDR设计问题现场答疑`

2018-10-10 11:49:20

我想请教个关于DSP6446的问题:DSP6446的哪个寄存器的设置需要根据DDR2的走线参数来确定呢?

2013-09-06 09:26:11

(flight-time skew)来降低共同切换噪声(SSN)。走线摆率可以达到0.8tCK,这个宽度导致无法确定在哪两个时钟周期获取数据,因此,JEDEC为DDR3定义了校准功能,它可以使控制器

2019-04-22 07:00:08

各位大虾,我想设计一个检测FPGA的外挂DDR3硬件是否有问题的程序。目前先做初级阶段工作,主要实现以下几点:1、检测DDR3数据线DQ是否有错连和漏连(虚焊)的情况,如有找到对应的错误处;2

2013-04-12 13:00:45

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

管理员,发一份关于K2 ddr3 initialization文档吧····我只找到了关于k1的

2018-06-21 17:16:04

大家好,请问:在PADS 2007中,已经对DDR3的数据线,地址线,及控制线做了分组设置, 现在要走线了,发现好难控制啊,应该如何走线啊?谢谢!

2013-07-03 09:19:02

我做硬件设计时,参照官方下载的原理图evm816x_Schematics_RevD,我发现DDR0的接线方式如下数据线DDR0_D5连接的是DDR3的MEM00_D5,DDR0_D0连接

2020-04-16 08:38:17

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

`各位大侠好,小弟最近在走一个DDR3的布线,数据线等长做到了+/-5mil,可地址线和控制线由于空间不够,只能做到+/-200mil,这样布线有问题吗?设计的板子是4层板,中间两层是电源

2015-06-22 20:59:24

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

看完保证你会做DDR3的仿真

2015-09-18 14:33:11

是信号完整性方面的配置,主要是一些信号线的阻抗设置,这个要咨询硬件工程师,这里我们直接使用NXP的默认设置即可。 关于DDR3的配置我们就讲解到这里,如果是EMMC核心板(DDR3型号为

2019-12-28 16:00:43

SDRAM 相连的是BANK35 的 IO,DDR3 的硬件设计需要严格考虑信号完整性,我们在电路设计和 PCB设计的时候已经充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,保证DDR3 高速

2021-07-30 11:23:45

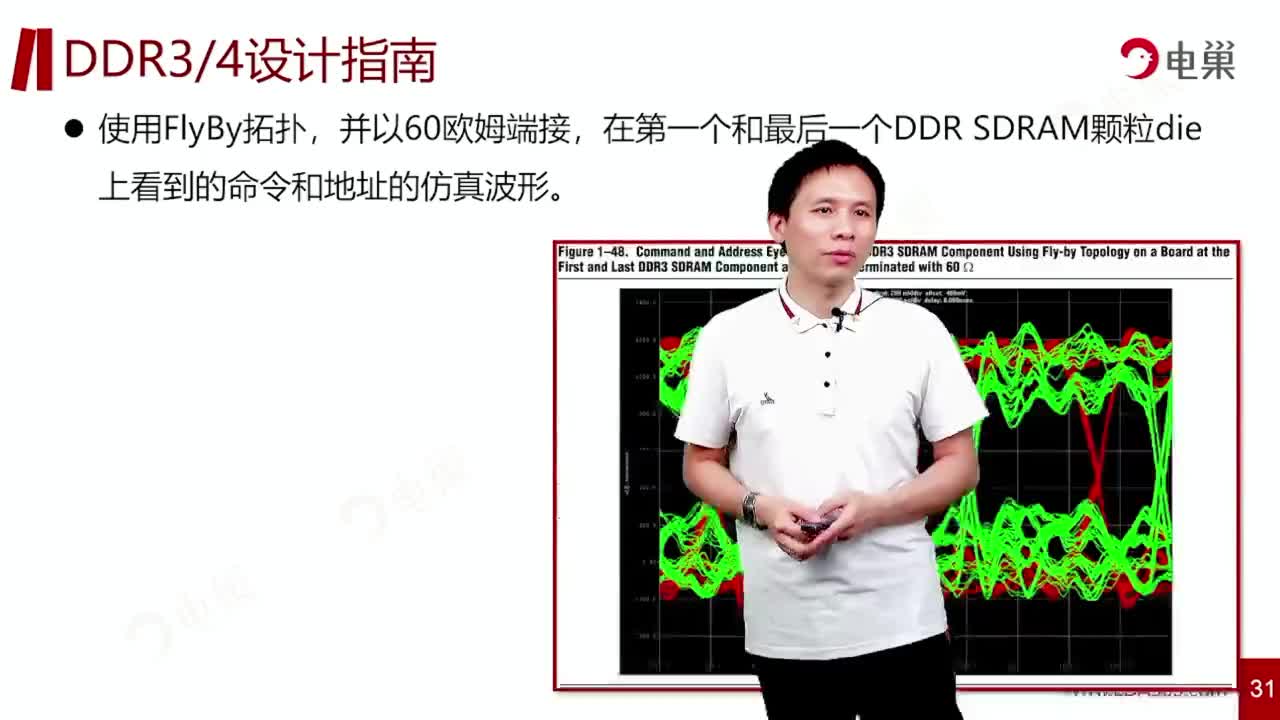

匹配电阻根据SI仿真的结果的走线阻抗,电阻值可能需要做出不同的选择,通常其电阻值在30-70 Ohms之间。而差分信号的阻抗匹配电阻始终在100 Ohms。3. 互联通路拓扑对于DDR2和DDR3,其中信号

2019-07-30 07:00:00

嗨,我正在设计一个定制FPGA板&我将使用带有Kintex(XC7K160T-2FFG676C)FPGA的DDR3 RAM。我阅读了xilinx& amp; amp; amp

2020-04-17 07:54:29

(CPU或FPGA)不停的发送不同时延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器。控制器端反复的调整DQS-DQS#的延时

2022-12-16 17:01:46

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配技术对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM

2018-08-02 09:34:58

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

本手册以 DDR3 器件为例讲解硬件设计方法,包括 FPGA I/O 分配、原理图设计、电源网络设计、PCB 走线、参考平面设计、仿真等,旨在协助用户快速完成信号完整性好、低功耗、低噪声的高速存储

2022-09-29 06:15:25

基于Xilinx MIS IP的DDR3读写User Interface解析特权同学,版权所有,转载请注明出处参考文档:ug586_7Series_MIS.pdf1. Command时序首先,关于

2016-10-13 15:18:27

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

大家好,我在DDR3规格中发现JEDEC79-3E定义VOH(DC)是DC输出高测量级别(用于IV曲线线性)。但是没有关于如何测量高输出直流输出的指南,特别是当信号在高电压时有环时,请参见附图。谁能

2019-04-17 13:59:13

一张表总结常规DDR3的走线设计

2021-03-03 08:00:13

模拟DDR3的地址信号与时钟信号

2021-03-02 08:12:10

各位大神好,小弟在设计的FPGA模块中需要加入一个DDR3作为缓存,但是不是特别了解DDR3的输入输出信号(包括信号类型、位宽以及功能),哪位大神对这个比较了解,最好能分享下相关资料,谢谢了,急用!!!!!!

2014-10-21 17:46:09

FPGA出来的信号到DDR3有800M的速度,对信号的相位偏移要求很高。请问在做Layout设计时,有没有固定的模式(设计方法、参数)可以保证DDR3信号的相位偏移在时间t内。比如要求走线平行,宽度

2016-06-14 12:31:37

DDR3的数据线等长是怎么设置长度的

2019-07-17 04:47:35

两片DDR3走fly by拓扑是否一定要8层板?最近要画一个FPGA带DDR3的,800Mhz,想了解一下

2019-03-01 07:35:22

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 编辑

各位专家好!刚刚学习DSP,还没有入门。实验室购买了TMS320C6678开发板。请问:1、为什么DSP需要外接DDR3?2

2018-06-20 00:40:57

针对DDR2-800和DDR3的PCB信号完整性设计

2012-12-29 19:12:39

设计为较高的阻抗,经过负载电容的平均后,负载部分的走线才会和主线段阻抗保持一致,从而达到阻抗连续,降低反射的效果。 在实际中的一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗

2015-11-16 16:04:19

Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4257

4257

本文章主要涉及到对 DDR2 和DDR3 在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB 层数,特别是4 层板

2011-07-12 17:31:10 0

0 针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 30895

30895 针对采用DDR3接口来设计的新一代闪存固态盘(SSD)需要完成与内存控制器进行通信与交互的特点,提出了基于现场可编程门阵列( FPGA)的DDR3协议解析逻辑方案。首先,介绍了DDR3内存工作原理

2017-12-05 09:34:44 10

10 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2021-05-02 09:05:00 2979

2979

《信号与系统 第3版》习题解析

2022-03-21 15:06:19 0

0 一、DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据

2022-12-21 18:30:05 1915

1915 DDR3的速度较高,如果控制芯片封装较大,则不同pin脚对应的时延差异较大,必须进行pin delay时序补偿。

2023-07-04 09:25:38 313

313

DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3905

3905

正在加载...

电子发烧友App

电子发烧友App

评论