Synopsys公司做功耗分析使用到的工具是:黄金时间的PX***PTPX铁可以在逻辑综合之后就进行功耗预估的PrimeTime 轨道进行分析,所以,我们只要用到的PrimeTime PX来做功耗分析就够了。

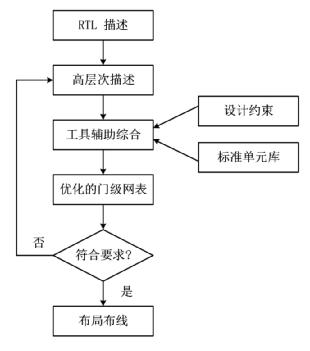

上图是布局布线后和逻辑综合后进行功耗分析的流程。

一。逻辑综合后的功耗分析

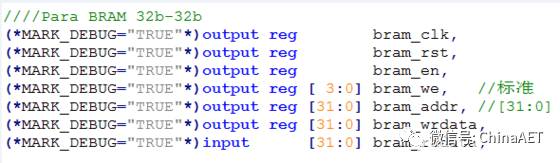

所用到的文件有:1。逻辑综合后的Verilog的文件

2。静态时序分析时用到的约束文件

3。RTL的仿真文件,我用的是VCD,毕竟标准各个仿真器都支持〜

4。有功耗信息的库文件。分贝,这个库文件可以报告一个库里的细胞,看是否有。

有了这些文件之后,就可以做功耗分析了,下面说一下功耗分析的流程:

1。允许功耗分析功能集power_enable_analysis

2。设置分析模式 设置 的因素。

3。读入设计和库文件

4。指定工作条件

5。时序分析 update_timing

6。获取活动数据

如果是RTL级别的网表文件,要用RTL来告诉PT之前指定的VCD文件是布局布线之前的。如果VCD是zero_delay的仿真,也就是说是纯纯的功能模拟的话,应该家用zero_delay选项如果都为指定,PT默认是门级。

7。设置功耗分析选项set_power_analysis_options:

-static_leakage_only选项set_power_analysis_options命令只支持 平均功率分析模式。

-waveform_interval-cycle_accurate_cycle_count,-cycle_accurate_clock,-waveform_format, - waveform_output,包括-include_groups选项 只支持基于时间的 功率分析模式。

8。功耗分析 update_power

9。生成功耗分析报告report_power

要说明的是,PTPX是primetime的一个增强功能,只用一个PT脚本就可以了,我把自己的pt脚本拿出来分享一下:

文件:pt.tcl

###########################################

# 设置功率分析模式

###########################################

设置真正power_enable_analysis;

集平均power_analysis_mode;

###########################################

# 读取和门级网表链接

###########################################

设置SEARCH_PATH“。。/源DB / /结果”

设置link_library“typical.db”

设置target_library“typical.db”

read_verilog jnd_90s.v

设置top_name JND

current_design JND

链接

###########################################

# 阅读SDC和过渡时间或注释寄生

###########################################

read_sdc pt_con.tcl

###########################################

# 检查,更新或报告时序

###########################################

check_timing

update_timing

report_timing

###########################################

# 读取开关活动文件

###########################################

read_vcd-RTL测试平台jnd_all.vcd strip_path

report_switching_activity list_not_annotated

###########################################

# 检查或更新或报告电源

###########################################

check_power

update_power

report_power层次

二。布局布线后的功耗分析

功率格式。这里不介绍。

#读库,设计,使电源分析

#和链路设计

设为power_enable_analysis真

设置link_library slow_pgpin.db

read_verilog power_pins.v

链接

#创建后备电源网

create_power_net_info vdd_backup功率

create_power_net_info vss_backup-GND

#创建域电力网

create_power_net_info t_vdd功率切换

-nominal_voltages {1.2} voltage_ranges {1.1 1.3}

create_power_net_info a_vdd功率

create_power_net_info b_vdd功率

#创建域地面网

create_power_net_info t_vss-GND

create_power_net_info a_vss-GND

create_power_net_info b_vss-GND

#创建内部电源网

create_power_net_info int_vdd_1功率

-nominal_voltages {1.2} voltage_ranges [1.1 1.3}

可切换的

create_power_net_info int_vdd_2功率

-nominal_voltages {1.25} voltage_ranges {1.1 1.3}

create_power_net_info int_vdd_3功率

-nominal_voltages {1.2} voltage_ranges {1.1 1.3}

create_power_net_info int_vdd_4功率

#创建电源域

一个create_power_domain吨

一个create_power_domain一个对object_list [get_cells PD0_inst]

POWER_DOWN power_down_ctrl [A] get_nets

power_down_ctrl_sense 0

一个create_power_domain B-object_list里get_cells PD1_inst]

POWER_DOWN

#连接到电源域的轨

connect_power_domain T-primary_power_net t_vdd

primary_ground_net t_vss

connect_power_domain一个primary_power_net的a_vdd

-primary_ground_net a_vss

-backup_power_net vdd_backup

backup_ground_net vss_backup

connect_power_domain B-primary_power_net b_vdd

primary_ground_net b_vss

#设置电压的电力网

set_voltage 1.15 object_list里{t_vdd a_vdd b_vdd}

#读取SDC和其他时间或电源断言

set_input_transition 0.0395 [all_inputs]

1.0 set_load [所有输出]

#执行。时序分析

update_timing

#读取开关活动

set_switching_activity 。。.

set_switching_activity 。。.

。。.

report_power

三。关于报告

一个标准的报告:

电力集团电源电源电源电源(%)ATTRS

-------------------------------------------------- -------------

io_pad 0.0000 0.0000 0.0000 0.0000(0.00%)

内存0.0000 0.0000 0.0000 0.0000(0.00%)

black_box 0.0000 0.0000 0.0000 0.0000(0.00%)

clock_network 0.0000 0.0000 0.0000 0.0000(0.00%)

注册8.442e-05 1.114e-05 9.208e-09 9.557e-05(29.97%),我

组合0.0000 0.0000 0.0000 0.0000(0.00%)

顺序0.0000 0.0000 0.0000 0.0000(0.00%)

属性

----------

- 包括驱动寄存器功率

内部开关漏电总时钟

电源电源电源电源(%)ATTRS

-------------------------------------------------- -------------

CLK 1.813e-04 4.199e-05 4.129e-10 2.233e-04

-------------------------------------------------- -------------

预计Clock1.813e 04 4.199e 054.129e 102.233e-04(70.03%)

开关电源净额= 5.313e-05(16.66%)

细胞内部功率= 2.657e-04(83.33%)

电池泄漏功率= 9.627e-09(0.00%)

---------

总功率= 3.188e-04(100.00%)

关于门控时钟的报告:

report_clock_gate_savings

****************************************

报告:时钟门储蓄

power_mode:平均值

设计:mydesign

版本:D-2009.12

日期:2010年10月29 12:08:20 2009

****************************************

-------------------------------------------------- ----------------

时钟:CLK

+时钟切换率:0.392157

+寄存器数:19262

+的时钟门数:12

+平均时钟切换率在寄存器:0.305872

+平均切换储蓄的寄存器:22.0%

-------------------------------------------------- ----------------

切换储蓄数目%

分布寄存器寄存器

-------------------------------------------------- ----------------

100%0 0.0%

80% - 100%76 0.4%

60% - 80%5660 29.4%

40% - 60%0 0.0%

20% - 40%8 0.0%

0% - 20%0 0.0%

0%13518 70.2%

----------------------

电子发烧友App

电子发烧友App

评论