为简化和加速复杂IC的开发,Cadence 设计系统公司 (NASDAQ:CDNS) 今天推出Tempus™ 时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

2013-05-21 15:37:37 3256

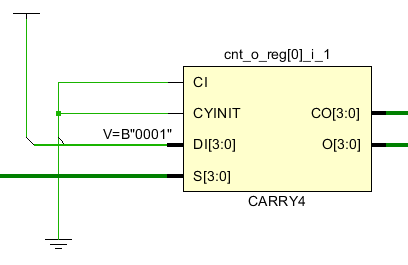

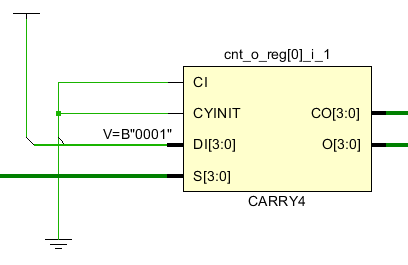

3256 更快,而一个坏的代码风格则给后续时序收敛造成很大负担。你可能要花费很长时间去优化时序,保证时序收敛。拆解你的代码,添加寄存器,修改走线,最后让你原来的代码遍体鳞伤。这一篇基于赛灵思的器件来介绍一下如何在开始码代码的时候就考虑时序收敛的问题,写出

2020-11-20 15:51:41 4814

4814

描述 本设计咨询主要介绍一个错误的时钟偏移计算导致错误时序收敛的问题。 出现问题的情况: 这可能会影响使用生成时钟的设计,其具有以下特征: 使用 Vivado 2018.2.x 及更早版本。 用户

2020-12-24 11:16:24 7462

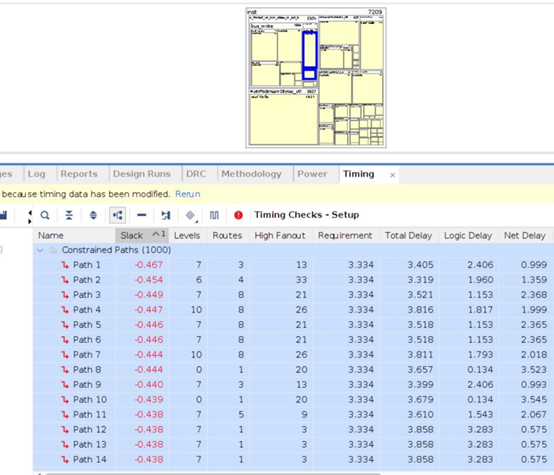

7462 资源利用率、逻辑层次和时序约束。 2时序基线设定:在每个实现步骤后检查并解决时序违例,从而帮助布线后收敛时序。 3时序违例解决:识别建立时间违例或保持时间违例的根源,并解决时序违例。 01 初始设计检查详细介绍 在赛灵思器件上实现设计,是一个自动化程度相当

2021-11-05 15:10:26 5892

5892

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2395

2395 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。

2023-08-03 09:27:25 2201

2201

在之前的文章里面介绍了Canny算法的原理和基于Python的参考模型,之后呢在FPGA上完成了Canny算法的实现,可是遇到了时序不收敛的问题,记录一下。

2023-11-18 16:38:28 1787

1787

、Vivado基本操作流程2、时序基本概念3、时序基本约束和流程4、Baselining时序约束5、CDC时序约束6、I/O时序7、例外时序约束8、时序收敛优化技术

2018-08-01 16:45:40

莱尔德科技公司推出散热型电路板屏蔽产品T-BLS系列,该产品结合电磁干扰防护和热管理技术,符合RoHS要求,用于需要对电路板进行屏蔽的电子设备。这个合二为一的产品降低了元件和零件的数量,节省

2018-08-31 11:53:58

跪求指点,据芯片手册里介绍,Burnout Current是用来检测前端传感器失效的,但是现在设计RTD检测模块时,不配置Burnout Current检测精度很高,但是一旦配置Burnout Current,检测到的值精度降低了很多(采样值偏大)。是不是配置有问题,这块配置有没有注意的地方,谢谢

2025-01-10 13:52:55

使用Kintex-7(xc7k325tffg900-2)进行编译。这一次,我得到了时间关闭。任何人都知道Artix-7和Kintex-7之间有什么不同,它对我的时序收敛有如此大的影响?

2020-08-17 08:40:58

请问能提供C6678上电芯片时序控制,以及配置端口电平和时序的Verilog代码吗?

2018-06-21 04:32:03

活动详情随着逻辑设计的规模,复杂度的提高,以及新器件的不断出现,逻辑工程师面临时序收敛困难,项目周期缩短,器件功能复杂等诸多挑战。规范开发流程,引入业界新技术、丰富工程师经验等,都是确保问题得以有效

2015-03-11 16:13:48

服务。 我们的服务将为 IC 芯片设计工程师、IC 制造工程师、材料研发工程师缩短研发时间,降低研发制造成本,增加产品成品率。 公司目前在北京、上海、深圳分别设有实验室,可为全国客户提供快速、便捷的技术

2013-12-18 14:37:38

今天给大侠带来FPGA 高级设计:时序分析和收敛,话不多说,上货。

这里超链接一篇之前的STA的文章,仅供各位大侠参考。

FPGA STA(静态时序分析)

什么是静态时序分析?静态时序分析就是

2024-06-17 17:07:28

时间,降低了制造成本。直观的逻辑合成环境包括先进的优化技术、屡获殊荣的时序分析和先进的推论技术,适用于与供应商无关的设计中,可加快产品上市时间、消除设计缺陷以及提供极佳的结果质量 (QoR)。 FPGA

2018-09-20 11:11:16

的物理管脚输出,同时还需保持设计的电气完整性。FPGA 复杂度增加也需要高级合成技术,如此才能更快达到时序收敛,最大程度地减少设计变更的影响以及解决特定应用要求。

2019-10-09 07:15:30

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可

2016-06-02 15:54:04

同步复位,可以降低资源的使用和功耗,有助于时序收敛。由于FPGA的初始状态是确定的(可以在定义说明中指定),为了更快地时序收敛,官方文档认为,能不用复位是最好的,尤其数据路径和移位寄存器的设计中。不过

2020-12-23 17:42:10

功耗作为芯片设计的关键参数,贯穿整个IC芯片设计处理过程,甚至会影响时序与芯片的运行。我们IC芯片设计师整理了一套有效的方法来处理功耗问题。【解密专家+V信:icpojie】 减少功耗的方法

2017-06-29 16:46:52

有没有哪位大神对ISE的时序约束比较熟悉,尤其是多周期约束这一块。在Quartus中使用比较简单,而且相关资料也比较多,但是ISE中的资料好像不是那么多,而且也没有针对具体例子进行分析。官网上给出

2015-04-30 09:52:05

《FPGA设计时序收敛》,很好的PPT!推荐给大家[hide][/hide]

2011-07-26 11:24:49

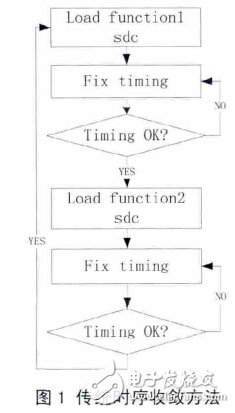

时序约束无法满足要求,则需要重新查看代码设计,往复的进行前阶段流程,直到时序约束满足要求。在项目系统时钟较高,时序要求严格的情况下,该过程消耗大量的项目开发周期,降低该阶段周期可有效提高开发效率。评估

2017-07-05 11:00:48

的设计计划,例如完整的和精确的时序约束和时钟规范节约时间的设计技术,例如为更好的性能结果,整合设计的各个部分而编写严谨的RTL代码,提出最高性能挑战,当你之后调整设计时减少迭代运行时间综合和摆放以及路由时序

2019-08-11 08:30:00

减压器降低了电压,增强了电流,是通过什么原理来实现的?给个原理图好吗,小弟研究一下谢谢了

2019-06-17 04:36:10

功能完整,使用方便外,它的设计性能也非常好,拿ISE 9.x来说,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟布局、更好的封装和时序收敛映射,从而

2009-11-23 16:13:52

性能的同时,缩短设计周期,降低开发成本,采用了半定制/全定制混合设计的方法,对RTL级代码进行优化改进,对处理器内核的执行单元采用全定制设计实现。混合设计的复杂性,给验证工作带来了巨大的挑战。本文针对

2011-12-07 17:40:14

降低犯错的几率。 其实时序问题是最让人琢磨不透,甚至有时候很难想象出现的现象本身居然和时序有关。今天的这个例子确有几分怪异,可以说出现了好几种比较反常的现象,甚至难以解释到只有怀疑是时序问题。其实

2014-12-26 16:36:46

和P&R之后的时序结果,具体是在时序关键路径上给定起点和终点的边界。我们指出的方法会早早地截取时钟和约束设置问题,同时也提供多种技术来调整和关联你设计的时序以及拥有快速时序收敛的RTL

2021-05-18 15:55:00

原边反馈AC/DC控制技术是近10年发展起来的新型AC/DC控制技术,与传统的副边反馈的光耦加431的结构相比,最大的优势在于省去了这两个芯片以及与之配合工作的一组元器件,这样就节省了系统板上

2012-11-21 10:59:07

量。通过采用基于40nm的半导体最新制造工艺以及创新方法来优化这些复杂的器件,设计人员能够在单芯片中集成更多的功能。这不但降低了总功耗,而且还可以降低后续工艺节点每一相应功能的功耗。TPACK便是能够

2019-07-31 07:13:26

求助高手,怎样在labview中获取周期波形中的一个周期的数据,方便后面的计算,我初步想法是利用matlab和labview结合使用,利用matlab的图像处理技术不知是否可行

2013-07-14 14:37:30

如何使用基于图形的物理综合加快FPGA设计时序收敛?

2021-05-06 09:19:08

CCD驱动电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完成驱动时序电路的实现

2019-10-21 06:05:17

ser-des核心工作在2.5 GHz。我使用了一个简单的包装器,它有clock,reset,tx& amp; rx串行信号用于环回,Tx并行数据输入和Rx并行数据输出。我该如何设置约束?请建议如何进行时序收敛,即如何确保生成的内核工作在2.5GHz。问候CJ

2020-06-03 11:24:21

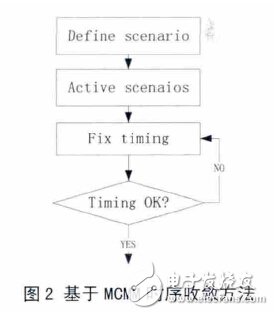

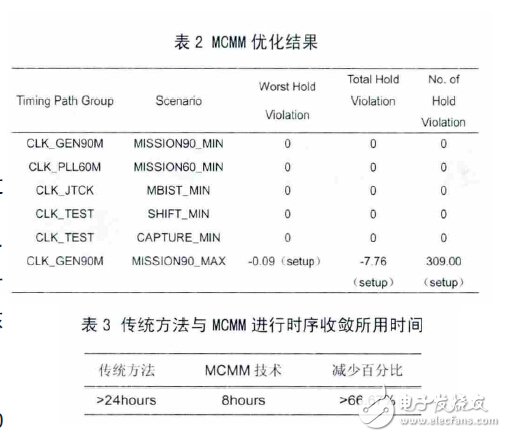

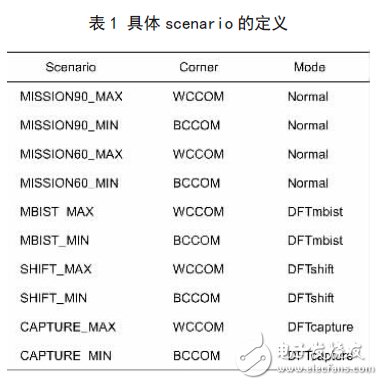

:JCDI.0.2010-04-005【正文快照】:1引言90/65nm下芯片的后端设计变得更加复杂,随着模式(mode)和角落(corner)的增多,如何快速取得各种情况下的时序收敛成为设计的重要

2010-05-28 13:41:58

您好,如果我想为我的设计获得最佳时序收敛,我应该使用什么实施策略?例如,如果我想改善设置和保持的松弛度,我应该选择哪种最佳策略?以上来自于谷歌翻译以下为原文Hello,If i want

2018-11-05 11:40:14

控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

2016-06-29 11:28:15

动态重构其逻辑功能等特点。利用CPLD芯片和数字控制技术设计的时序电路,可将时序控制的精度提高到纳秒级,并且工作稳定,不受温度的影响,有利于系统定位精度的提高。

2021-05-06 09:44:24

什么是时序收敛?如何去解决物理设计中时序收敛的问题?

2021-04-26 06:38:50

IC尺寸微缩仍面临挑战。为了使芯片微缩,总是利用光刻技术来推动。然而近期Sematech在一次演讲中列举了可维持摩尔定律的其他一些技术。1. 零低k界面:在目前Intel的45nm设计中,采用硅衬底

2014-01-04 09:52:44

FPGA外部的芯片,可能是FPGA内部的硬核。对于FPGA design来说,必须要关注在指定要求下,它能否正常工作。这个正常工作包括同步时序电路的工作频率,以及输入输出设备的时序要求。在FPGA

2019-07-09 09:14:48

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

如何收敛高速ADC时序?有哪种办法可以最大化ADC的建立和保持时间?

2021-04-14 06:06:09

如何在开始码代码的时候就考虑时序收敛的问题?

2021-06-18 06:29:47

下面我们来找这些参数,将上篇文章中的数据添加约束之后,执行一次全编译,当然这个时候肯定是时序不收敛,不过没关系,时序收不收敛跟我们的PFGA建立保持时间以及数据输出时间是没什么关系的。我们先来看建立保持

2015-03-31 10:35:18

时延以及数据包丢失是导致网络控制系统性能降低的重要原因。利用既是时钟驱动又是事件驱动的传感器,可以使时延与采样周期具有相同的长度,这样降低了建模随机时延的

2009-08-31 11:25:47 5

5 Ethernet-over-SONET/SDH映射器,降低了新型以太网服务传输的总成本

DS33M30/DS33M31/DS33M33是以太

2009-03-31 10:57:35 2544

2544 更高速的 ADC 在转换器输出和接收机输入之间有严格的时序要求;知道如何利用产品说明书数字来保证无错误数字传输。

最近几年,高速、高精度的模数转换器 (ADC)

2010-07-13 09:59:10 969

969 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 Cadence公司宣布Renesas微系统有限公司已采用Cadence Encounter RTL Compiler用于综合实现。其优势在于将复杂ASIC设计的芯片利用率提高了15%,面积减少了8.4%,加速了实现周期并降低了成本。

2012-12-14 10:59:15 1336

1336 时序约束可以使得布线的成功率的提高,减少ISE布局布线时间。这时候用到的全局约束就有周期约束和偏移约束。周期约束就是根据时钟频率的不同划分为不同的时钟域,添加各自周期约束。对于模块的输入输出端口添加

2017-02-09 02:56:06 918

918 fpga时序收敛

2017-03-01 13:13:34 23

23 这是特权同学的关于fpga时序分析方面的极好资料

2017-08-28 11:19:14 20

20 介绍了一种在多工艺角多工作模式下快速实现时序收敛的技术MCMM(Multicorner-Multimode)技术,该技术将工艺角和模式进行组合,对时序同时进行分析和优化,到达快速实现时序收敛的目的。该

2017-10-20 15:21:11 3

3 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

CCD驱动 电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完成驱动时序电路的实现

2017-11-24 18:55:51 2079

2079

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 5956

5956

目前,花费在时序收敛与签收(Timing closure and signoff)上的时间接近整个设计实现流程时间的40%,复杂设计对实现时序收敛提出了更高的要求。但在Cadence公司芯片实现之

2017-12-04 10:30:45 0

0 FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA内部的硬核。

2018-07-11 09:37:00 10018

10018

介绍了实现网络快速收敛的相关协议以及引起收敛的原因,IXIA正在申请专利的集成在IxNetwork产品中TrueView网络收敛时间测试技术和传统技术的差异。 1 引言 收敛(Convergence

2018-02-14 09:24:00 7820

7820

FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 19

19 当然,层次化设计也有许多不可避免的缺陷,最突出就是来源于时序预估时产生的误差。这种误差往往使得做划分的物理实现时,时序难以收敛。或者尽管划分满足时序收敛条件,在全芯片合并后,会发现一些时序路径又会变得极差无比。

2018-06-04 17:14:28 7697

7697

标准块写操作图17显示的是一个标准的块写周期时序图。块写周期可以在每一个时钟周期完成一次数据传输。

2018-07-19 15:36:31 4417

4417

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 7944

7944

随着架构师开始利用 AI 提高性能和降低功耗,并为未来芯片的开发、制造和更新奠定基础,人工智能也开始影响半导体设计。技术增加了芯片粒度,但随着架构需要处理更大数据量,设计起点也变了。

2018-11-16 16:46:53 5438

5438 万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。

2019-07-26 15:56:23 4237

4237

为提高带宽,很多类型的 Memory 都采用了 Double Data Rate(DDR)interface,它对在内存控制器(memory controller)设计过程中的时序收敛和后仿真提出了挑战。

2019-08-03 10:36:40 4430

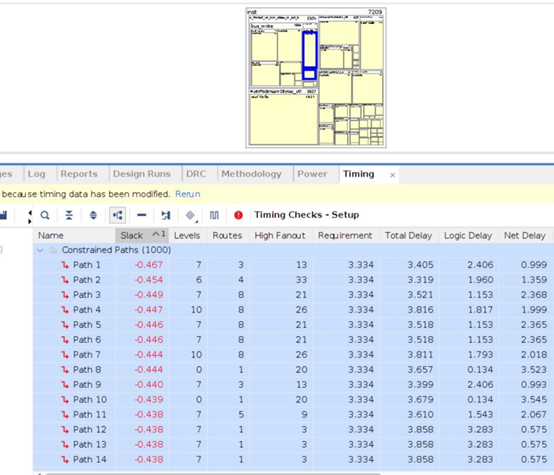

4430 生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Setup、Hold和Pulse Width的总体信息,但凡WNS、WHS或WPWS有一个小于0,就说明时序未收敛。

2020-08-31 13:49:10 7100

7100

本文是一篇详细介绍ISSCC2020会议上一篇有关亚稳态解决方案的文章,该技术也使得FPGA在较高频率下的时序收敛成为了可能。亚稳态问题是芯片设计和FPGA设计中常见的问题,随着FPGA的发展,时序

2020-10-22 18:00:22 5277

5277

高效的以太网供电解决方案降低了总体成本

2021-03-20 19:50:43 6

6 在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种

2021-05-19 11:25:47 3923

3923

1、如何降低功耗?

(1) 优化方向:

组合逻辑+时序逻辑+存储

(2) 组合逻辑:

(a)通过算法优化的方式减少门电路

(b)模块复用、资源共享

(3) 时序逻辑:

(a)尽量减少无用

2022-02-11 15:30:36 2

2 本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整

2022-08-02 11:37:35 989

989

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25:06 1049

1049

随着物联网、机器人、无人机、可穿戴/植入设备等低功耗便携式设备越来越普及,超低功耗SoC芯片技术也面临着越来越大的挑战。为了降低这些SoC芯片的功耗,人们提出了如上图所示的各种技术。

2022-12-21 09:51:22 1414

1414 对于发送时钟和接收时钟是同一时钟的单周期路径,时钟抖动对建立时间有负面影响,但对保持时间没有影响。

2023-06-12 09:15:48 1129

1129

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41:31 3800

3800

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角分析模式。这是在先进工艺下必须要使用的一种时序分析模式。

2023-07-04 15:40:13 4000

4000

本文聊聊“RQS_CLOCK-12”时钟设置建议以及它如何帮助达成时序收敛

2023-07-12 15:44:19 1195

1195

电子发烧友网站提供《UltraFast设计方法时序收敛快捷参考指南(UG1292).pdf》资料免费下载

2023-09-15 10:38:51 0

0 设计周期延长,且达不到性能目标。所以采用正确的方法,可使您减少迭代次数,提高可预测性,并更快地实现时序收敛。

2025-06-04 11:40:33 676

676

电子发烧友App

电子发烧友App

评论