需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图示)。

2022-10-14 09:27:03 5312

5312 本内容讲解了计算高频设计时计算特性阻抗等参数的软件。因为GPS接收机设计时,天线信号线的特性阻抗要求在50欧姆,以实现与天线的阻抗匹配,若人工去计算,计算较繁琐,较容易出

2011-12-14 17:57:48 8249

8249

与计算方法根据信号传输线的不同位置可以形成各种各样的结构及其计算方法(参见《现代印制电路基础》一书第十四章)。2.3特性阻抗值Z0的一般设计规则 ⑴选用合适的基板(CCL)材料和PCB结构,确定信号

2018-02-08 08:29:08

嗨,我不知道是Simulink问题还是包括Micro.Blockset的模型……当我用相同的Matlab版本在不同的平台上打开模型时,一些信号线变得与其目的地不相连。

2020-04-20 10:23:14

在信号线中使用共模扼流圈的目的是什么?共模扼流圈的等价电路图中记载的黑点是什么意思?信号线用共模扼流圈的使用方法

2021-04-09 06:57:11

再做调整。

4、阻抗计算列表操作

1) 在华秋DFM软件中输入阻抗控制 要求值 ,再选择 阻抗层 ,找到阻抗对应的模板,再输入原始 线宽线距 ,如参考层特别比如隔层参考,需要手动选择参考层。

2

2023-09-13 11:03:22

中单个信号线的阻抗。在单端传输中,信号通过单个信号线进行传输。

03 问:什么是差分阻抗?答:差分信号线结构用于控制阻抗,驱动端输入极性相反的两个信号波形,由两根差分线传送,接收端减法处理,这种

2024-01-05 10:52:33

原理图编辑器的增强功能包括信号线束的概念。信号线束可以对包括总线和导线在内的不同信号线进行逻辑分组,以满足设计灵活性和合理化的需要。导线用于表示各点之间的电气连接,而总线则用于表示一组相关的信号线

2019-06-28 06:00:00

法则就能做到尽量做到吧时钟信号:以地平面为参考,给整个时钟回路的走线提供一个完整的地平面,给回路电流提供一个低阻抗的路径。由于是差分时钟信号,在走线前应预先设计好线宽线距,计算好差分阻抗,再按照这种

2015-01-15 10:39:37

直径应该小于21.39598588mil,取个常用的参考值过孔用钻孔10mil,焊盘20mil就很合理。该处为了能让大家更明白计算关系,列图标进行说明。(11)按照计算的线宽、线距、设置约束规则。新建

2020-07-06 15:58:12

无法避免线宽的变化,应该尽量减少中间不一致部分的有效长度。

倒角规则

在PCB布线时,走线拐弯的拐角应避免设计成锐角和直角形式,以免产生不必要的辐射;要求所有线与线的夹角应大于等于135°在走线确实需要

2023-11-14 16:06:37

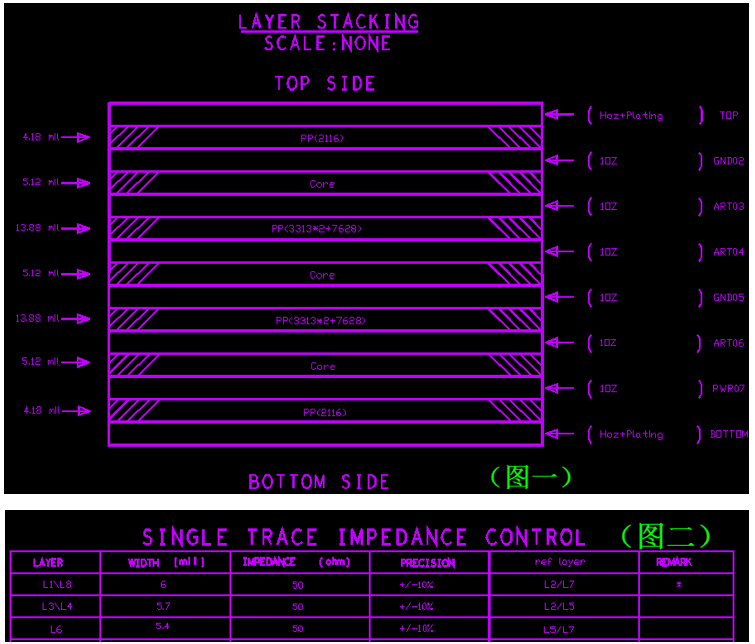

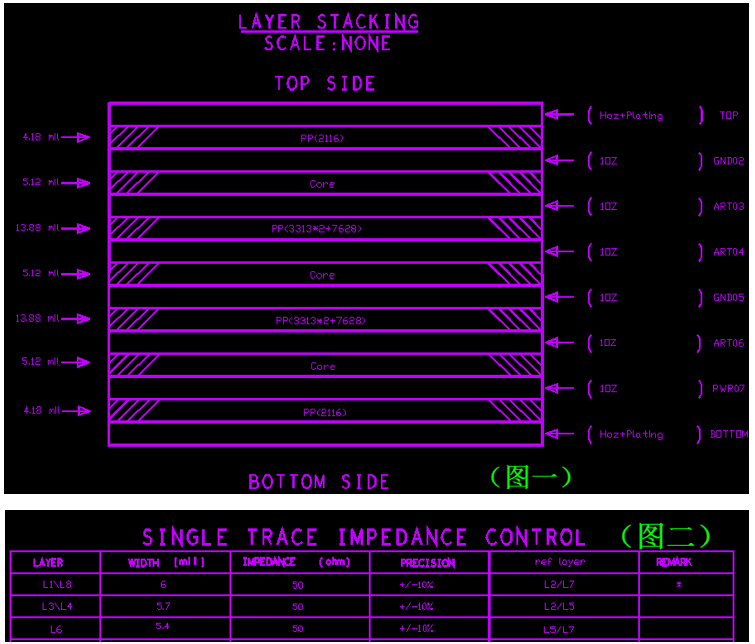

;工厂使用的阻抗计算工是Polar Si9000,参数如下:H1:介质厚度(阻抗线到参考层之间的厚度)Er1:板材的介电常数 4.2-4.6(PP以4.2计算,Coer以4.5计算)W1:设计线宽W2

2020-07-01 15:54:09

请教:1. PCB板上 RS485 的 A B线 在 走线时 需要注意哪些 问题 ?2.PCB板上 RS485 的 A B线 需要做阻抗匹配吗 ?谢谢!

2016-10-25 14:29:05

的问题不一定能做到设置的线宽和间距,而且线宽和间距越小,成本越高。2、线距3W规则所有设计在时钟走线、差分线、视频、音频、复位线以及其他系统关键线路等。多个高速信号线长距离走线时,为了减少线与线之间

2022-12-15 16:28:19

的波阻抗),在PCB中是否还有能让地线加宽的地方。 · 对于关健的信号线是否采取了最佳措施,如长度最短,加保护线,输入线及输出线被明显地分开。 · 模拟电路和数字电路部分是否有各自独立的地线

2018-09-03 11:06:43

在布局时遇到个问题希望各位大神帮忙解答一下: 要求差分阻抗为100R,通过polor计算出a.走线宽度5mil,线距5mil,包地5mi和b.走线宽度7mil,线距6mil,包地距离6mill都可达到要求(阻抗值也差不多),那么对于a.和b我应该如何选择呢?

2013-07-29 09:28:10

`PCB设计线宽、线距规则设置多大比较好? 中国IC**1、需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R

2019-02-19 13:36:26

控)。

线距规则设计之前须考虑设计的铜厚要求,1OZ尽量保持4mil以上距离,2OZ尽量保持6mil以上距离。

关于差分信号对内的距离设计,应该按照阻抗的要求,合理设置其相应的距离。

布线应远离板框位置

2023-09-01 10:51:14

。这就要求在进行高速PCB布线时,必须要遵守以下布线规则: (1)LVDS布线规则。要求LVDS信号差分走线,线宽7mil,线距6mil,目的是控制HDMI的差分信号对阻抗为100+-15%欧姆

2018-09-17 17:36:05

请问各路大侠,蛇形走线有什么作用?为什么要蛇形走线?哪些类信号线需要蛇形走线,如果要进行蛇形布线,需要满足什么规则和注意什么问题?烦劳大侠们指点一下. 电感作用 视情况而定,比如PCI板上的蛇行线

2014-11-19 11:54:01

应该按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图所示)。

2019-07-19 08:23:41

大安全间距等方法。保证信号质量。

d) 有阻抗控制要求的网络应布置在阻抗控制层上,须避免其信号跨分割。

2布线窜扰控制

a) 3W原则释义

线与线之间的距离保持3倍线宽。是为了减少线间串扰,应保证线间距足够大,如果线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰,称为3W规则。

2023-12-12 09:23:35

蛇形线时不能太密集,应为4W,等长尽量在焊盘附近解决,以倒角形式来走线,不能随意改变线宽和线距; 对称性:MIPI线始终保持等长和等距。对称是为了保证走线阻抗一致,减少反射。对称性不好会使信号失真

2023-04-12 15:08:27

的差分阻抗就需要这些.PCB布局时,这些焊盘需要保留在需要的时候。 D+、D- 的线宽跟线距为9mil ,这两个信号线旁不可以铺铜,应该将地裸空。如下图: 一些较差的USB走线 一些很普通的较差

2023-04-13 16:09:54

来说,没有按照正确的方法评估走线线宽,可能导致电流过大,烧毁板子走线;对于高速信号来说,没有合适的计算线宽,可能导致阻抗失配,引起信号完整性问题。 2.PCB走线跟哪些因素有关 PCB的走线主要跟

2023-04-12 16:02:23

这样的一个射频参考电路。要求特性阻抗是50欧,RF信号线的线宽应该是多少呢?{:4_106:}

2014-07-15 10:36:26

STM32的SPI通信线传输需要做好阻抗匹配吗

2023-10-10 06:35:12

Lay板时的线宽线距,是怎么确定最小值的

2017-12-09 11:07:50

pcb内电层设计的规则中plane下面的三个规则应该怎么设计?如图所示?都选择默认?还是说根据自己设计规则里面电源线的宽度来设计?内电层不走信号线

2017-07-24 09:12:34

。 LVDS布线规则。要求LVDS信号差分走线,线宽7mil,线距6mil,目的是控制HDMI的差分信号对阻抗为100+-15%欧姆 DDR布线规则。DDR1走线要求信号尽量不走过孔,信号线等宽,线与线

2019-04-19 15:36:28

及成品板厚的总厚度。

4、线宽线距计算阻抗值

选择阻抗层,找到阻抗对应的模板,再输入原始线宽线距,如参考层特别,如隔层参考,需要手动选择参考层,参数输入完毕后,点击全部计算,计算结果为绿色则计算正确,为

2023-05-04 16:43:04

中输入阻抗控制 要求值 ,再选择 阻抗层 ,找到阻抗对应的模板,再输入原始 线宽线距 ,如参考层特别比如隔层参考,需要手动选择参考层。

2、参数输入完毕后点击全部计算,计算结果为绿色则计算正确,若为

2023-09-15 14:11:33

各段之间也将会出现反射。这就要求在进行高速PCB布线时,必须要遵守以下布线规则:USB布线规则。要求USB信号差分走线,线宽10mil,线距6mil,地线和信号线距6mil。HDMI布线规则。要求

2017-10-23 14:29:36

在走线的时候 突然遇到区域规则 线距变了 调整后一推线 他有变了怎么解决呀

2019-08-07 05:20:28

提问: 1)我想问下为啥一般模拟信号不用考虑阻抗设计?如果考虑是多少为佳? 2)为啥模拟信号线走线越粗越好吗?其中有什么道理吗?是抗干扰的能力强吗?

2018-12-25 09:25:13

回板内正常制作出生产所需的工具菲林。

匹配叠层结构

1、按照客户要求的叠层厚度及所用的物料参数制作叠层图,计算阻抗线时,华秋DFM自动读取叠层图里面的参数,使用叠层图里面的介质厚度,计算线宽线距所需要

2023-04-28 11:01:02

板的生产变得越来越重要。另外,其它的方法,如余线(stub)长度最短化、末端去除和整线使用,也用来保持信号传递中瞬时阻抗的稳定。四. 传输线阻抗的计算设计一个预定的特性阻抗,需要不断调整线宽、介质厚度

2015-01-23 11:56:02

。。。

那到底要怎么样算嘛!高速先生为此还真的专门做了一块测试板出来,就是按照上面类似的线宽来做的。

那到底信号线A的阻抗是多少呢?信号线B到底在它旁边起到一个怎么样的影响呢?我们想象一下在具体工作的时候

2023-11-02 14:00:35

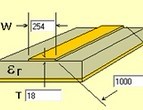

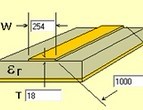

的。以下以共面波导为例说明一下如何计算特性阻抗:a)输入参数图中的各输入参数意义如下:L:线长H:板厚,即信号所在层与临近地层之间的介质厚度W:线宽G:线与其它铜波的间距T:铜皮厚度b)选择介质点击左下

2019-05-31 06:54:07

线宽,地线>电源线>信号线,但是哪些是电源线哪些是信号线,我不是很懂,麻烦大家浪费几分钟说下输入端线宽加大,SW OUT都是大电流输出 线宽加大,那1>1,2,3,4这些也要加宽吧?2>A,B,C,D连到地这些也要加宽吗?先谢谢

2017-08-28 20:46:04

控)。

线距规则设计之前须考虑设计的铜厚要求,1OZ尽量保持4mil以上距离,2OZ尽量保持6mil以上距离。

关于差分信号对内的距离设计,应该按照阻抗的要求,合理设置其相应的距离。

布线应远离板框位置

2023-09-01 10:48:01

制作出生产所需的工具菲林。

匹配叠层结构

1、按照客户要求的叠层厚度及所用的物料参数制作叠层图,计算阻抗线时,华秋DFM自动读取叠层图里面的参数,使用叠层图里面的介质厚度,计算线宽线距所需要的介质

2023-04-28 11:12:07

有的板子在同一层 但是走线和焊盘颜色分信号线和电源线是怎么设置的

2019-11-26 21:30:08

的信号线之间,以及其他干扰信号之间保持足够的距离。一般情况下,该距离至少为信号线宽度的40 倍。 无论如何,低电平信号线的对地电容应该很高,以便减小耦合电压。这就是说,低电平信号导线应当靠近地线。如果

2018-09-14 16:38:43

同一条信号线从顶层经过孔到底层,假如该信号线顶层和顶层是垂直的(垂直点就是过孔点),那这算不算是90°走线,是不是需要避免这种直接垂直的情况?还是应该先放置过孔,过孔走一段距离后再45°折角比较好?最佳的处理走线方式是怎样的?

2019-05-28 05:35:10

接口差分信号线设计USB2.0协议定义由两根差分信号线(D 、D-)传输高速数字信号,最高的传输速率为480 Mbps。差分信号线上的差分电压为400 mV,差分阻抗(Zdiff)为90(1±O.1

2015-02-11 14:44:36

在PCB中为什么地线会比电源线和信号线宽起什么作用?还有就是为什么有的时候会在GND上挖一段缺口?

2023-04-10 16:18:53

问:在布多层板时,我们都知道应该把重要的信号线尽量布在信号层,把干扰降低到最小!但是有些疑问,就是重要的信号线怎么区分出来?为了降低干扰,哪些信号线选择包地?(容易干扰信号线)心有困惑,请有学之士,不吝赐

2016-10-13 10:29:28

在高速PCB板上,给高速信号线进行屏蔽时采取什么样的措施比较好?我是给它进行网络包地,这个网络包络的线性要改成GND的电气属性么?线宽和间距有特殊要求没有?如何操作这一规则?

2023-04-07 17:11:10

藕合。为了减小藕合,建议在高阻抗的信号线之间,以及其他干扰信号之间保持足够的距离。一般情况下,该距离至少为信号线宽度的40 倍。 无论如何,低电平信号线的对地电容应该很高,以便减小耦合电压。这就是说

2013-09-13 10:26:12

图中的信号迹线横截面通常为梯形,而宽度 W 是指最接近上表面的迹线宽度,W1 是指最接近下表面的迹线宽度。表面微波传输带最简单的配置表面(或曝置)微波传输带如下图所示。其中包括一条信号线,顶部和侧边都

2009-09-28 16:16:56

,必须需要拐角时应进行直角补偿,见附图1;9、射频信号线上尽量不要出现分叉或者之脚,都会对射频阻抗产生影响;10、不要在射频传输线上平行布置任何线路,这样的线路会增加线与线之间的耦合;11、不要在射频传输线上设置测试点;

2021-04-20 20:25:28

[单片机IO变成输入可以检测状态] (看图中的框4)MC/A0/A1单向信号线, MD双向信号线低速PCB 300KHZ有于项目特殊性 上述4根线单根需要2.5米长并放在工厂里面.这个信号线容易***扰吗, 如果容易干扰怎么解决比较好。干扰会不会对IO口有损害需要考虑防静电问题吗. 加TVS等?

2023-03-08 17:12:00

高频差分信号线:做FPC板,在产品上有两条等长信号线,怎么测试两条信号线直接的高频阻抗?有什么仪器可以测试吗,TDR仪器测试头太大了有没有仪器可以测试,网分?

2020-05-11 10:26:53

1 单端信号线就是用一根线进行传输,并以地作为电压参考点。也就是说,单端信号就是传输电平信号线与地平面电平的电压差。所以信号从A点传递到B点,必须保证这两点之间的地平面电势保持一致。否则就会造成信号

2019-05-22 07:42:12

50ohm,这样可以与一般测试设备端口阻抗(如矢量网络分析仪和频谱仪等)相匹配,借助微带线阻抗计算公式,模型结构参数设置如下:信号线和地平面材料设为铜,电导率σ=5.8*107S/m,信号线宽w

2019-07-03 07:18:29

可能带来不可预知的结果。 3、走线长度控制规则 即短线规则,在设计时应该尽量让布线长度尽量短,以减少由于走线过长带来的干扰问题,特别是一些重要信号线,如时钟线,务必将其振荡器放在离器件很近的地方

2023-04-18 15:04:04

8-20us雷击测试,信号接口 差模2KA,共模3KA,走线线宽、线距、铜厚、过孔该如何选择? 电源接口 差模5KA,共模5KA,走线线宽、线距、铜厚、过孔该如何选择? PCB布线有其他哪些方面需要注意的?

2017-09-05 17:08:36

以上为8层板顶层部分元器件排列框图,第2层左半部分为模拟地,右半部分为数字地,第3层、第6层为信号层,请问第三层的模拟地下,能否通过数字信号线路,如果不能通过,在第6层走数字信号线,该数字信号线应该距离旁边的模拟地通孔多远,数字信号频率分别为5M、0.5M,

2018-08-15 06:58:10

是否可以把电源平面上面的信号线使用微带线模型计算特性阻抗?电源和地平面之间的信号是否可以使用带状线模型计算?

2009-09-06 08:39:46

脉冲信号的带宽100m,干扰的频谱应该更好,然后找出它,通过设计RC的滤波进行信号线滤波,c一般要到pf。这样是否合理?我看一些资料介绍用磁珠滤波,这样总感觉不可控,100m下的阻抗应该需要比较小才不会损失信号本身能量,还有的方法是采用共模电感,这样不会损失差模信号,也就是信号线。请大神们分析?

2023-11-20 06:30:02

规则一:高速信号走线屏蔽规则 在高速的设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。 图1

2018-09-20 10:38:01

,在PCB设计过程中,应该遵循高频电路设计的基本原则。这就要求首先要注意电源的质量与分配,其次要注意信号线的分布和地线的布线。 1.电源质量与分配 在设计PCB板时,给各个单元电路提供高质量的电源

2018-09-05 16:38:26

脉冲信号的带宽100m,干扰的频谱应该更好,然后找出它,通过设计RC的滤波进行信号线滤波,c一般要到pf。这样是否合理?我看一些资料介绍用磁珠滤波,这样总感觉不可控,100m下的阻抗应该需要比较小才不会损失信号本身能量,还有的方法是采用共模电感,这样不会损失差模信号,也就是信号线。请大神们分析?

2019-02-15 13:40:12

如何确定线宽线距?还有过孔的大小

2019-03-11 06:52:03

AD中 Outline Selected Objects(描画选择对象的外形)命令时可否设置描画线的线宽和描画线与被描线的线距。

2019-09-11 05:36:52

各位大侠 ,请教一个问题:1.pcb布线时,信号线,地线,电源线按照什么顺序布线?a.是先走信号线,再走电源线,最后走底线,在铺地?这样走的话,感觉电源线比较乱。b. 还是,先走一对平行的电源线

2019-07-28 23:20:27

什么样的信号线需要50欧姆阻抗,90欧姆阻抗,100欧姆阻抗,什么信号是单端的??什么样的信号是共面的???什么信号需要包地处理的???

2019-03-19 00:32:53

比如电源走线线宽要加粗(例如20~30mil,第一优先),信号线一般宽度(例如10mli),但有些IC引脚很细,例如8mil左右。这如果选择8mil线宽走线会警报提示不符合10mil宽度,想问下这个怎么设置?

2019-04-12 04:58:24

请问一下 高速信号线为什么要阻抗匹配啊 2.5G一般做多大阻抗匹配为好呢

2019-07-10 22:19:05

中输入阻抗控制 要求值 ,再选择 阻抗层 ,找到阻抗对应的模板,再输入原始 线宽线距 ,如参考层特别比如隔层参考,需要手动选择参考层。

2、参数输入完毕后点击全部计算,计算结果为绿色则计算正确,若为

2023-09-15 14:12:46

高速信号线中才考虑使用这样的电阻。在低频情况下,一般是直接连接。 这个电阻有两个作用,第一是阻抗匹配。因为信号源的阻抗很低,跟信号线之间阻抗不匹配(关于阻抗匹配,请看详述),串上一个电阻后,可

2015-01-21 14:53:07

一个稳定的电流,从电池吸收恒定的电流,传输线就等同于一个电阻,并且阻值恒定。我们称之为传输线的浪涌阻抗。同样,当信号沿传输线向前传播时,每传播一定的距离,信号会不断地探查信号线的电环境,并且试图确定

2019-06-14 13:24:02

在画高频PCB,信号线粗还是细好?线宽大概多少?小弟新手,希望能顺带讲讲为什么。先谢谢劳烦大家了!

2015-08-21 01:38:00

各段之间也将会出现反射。这就要求在进行高速PCB布线时,必须要遵守以下布线规则:USB布线规则。要求USB信号差分走线,线宽10mil,线距6mil,地线和信号线距6mil。HDMI布线规则。要求

2019-07-28 09:00:18

。 LVDS布线规则。要求LVDS信号差分走线,线宽7mil,线距6mil,目的是控制HDMI的差分信号对阻抗为100+-15%欧姆 DDR布线规则。DDR1走线要求信号尽量不走过孔,信号线等宽,线

2017-10-20 14:29:17

一丶 需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图

2020-10-06 20:54:00 14131

14131

阻抗控制计算:以 E03为例,E03 USB2.0 D+ , D- 要求有90欧姆的阻抗匹配,依照此要求,计算出这两条差分信号线在走线时的线宽和线间距。

2023-01-11 16:45:38 1

1

电子发烧友App

电子发烧友App

评论