滤波电容:用在电源整流电路中,用来滤除交流成分,使输出的直流更平滑。去耦电容:用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。旁路电容:用在有电阻连接时,接在电阻两端使交流信号顺利

2019-08-26 09:41:50

PCB PDN design guidelines (PCB电源完整性设计指导) ------PCB平面图指南一、 不带电源平面1.为每个有源设备至少提供一个“本地”去耦电容器,并为板上分布的每个

2021-12-28 06:07:45

类型的频率响应很重要。随便选用电容,会让设计低阻抗 PDS 系统的努力付之东流。如何设计出合格的 PDS要设计出合格的 PDS,需要使用各种电容(见图 1)。PCB 上使用的典型电容值只能将直流或

2020-11-18 09:18:02

类型的频率响应很重要。随便选用电容,会让设计低阻抗 PDS 系统的努力付之东流。如何设计出合格的 PDS要设计出合格的 PDS,需要使用各种电容(见图 1)。PCB上使用的典型电容值只能将直流或接近

2022-05-07 11:30:38

是否通过走线或通过一对过孔将去耦电容连接到IC电源引脚的问题。我们看到通孔技术是优越的,因为它降低了电感,当我们试图确保去耦电容在50-100] Vias和Planes在本文中,我们将探讨与通孔

2018-07-27 11:59:50

对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量

2018-09-18 15:56:26

个很全方面讲解的。下面这些内容是我转载的一片关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。 老师 问:为什么去耦电容就近摆放呢?学生 答:因为它有有效半径哦,放的远了失效

2018-08-28 14:41:28

的相关文章。下面这篇文章是我转载于博士的一片关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。 老师 问: 为什么去耦电容就近摆放呢?学生 答: 因为它有有效半径哦,放的远了

2018-09-12 10:46:08

个很全方面讲解的。下面这些内容是我转载的一篇关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。 老师问: 为什么去耦电容就近摆放呢? 学生答: 因为它有有效半径哦,放的远了

2018-09-17 17:40:22

PCB抗干扰设计,电源线、地线、去耦电容如何配置?

2021-03-17 07:04:11

什么是PCB中的板级去耦呢?如何设计板级去耦。

2021-01-22 06:28:39

个高频去耦电容。每个电解电容边上都要加一个小的高频旁路电容。 (2) 用大容量的钽电容或聚酯电容而不用电解电容作电路板上的充放电储能电容。使用管状电容时,外壳要接地 (3) 对进入印制板的信号要加滤波

2017-03-16 09:46:27

。二、降低冲击电流影响的措施:(1)降低供电电源内阻和供电线阻抗(2)匹配去耦电容三、何为去耦电容在 ic(或电路)电源线端和地线端加接的电容称为去耦电容。四、去耦电容如何取值去耦电容取值一般为

2011-02-24 14:30:32

?正题:在设计电子线路时,比较多考虑的是产品的实际性能,而不会太多考虑产品的电磁兼容特性和电磁骚扰的抑制及电磁抗干扰特性,在实际PCB设计中可采用以下电路措施: (1)为每个集成电路设一个高频去耦电容

2016-12-13 17:10:29

以下电路措施:(1)为每个集成电路设一个高频去耦电容。每个电解电容边上都要加一个小的高频旁路电容。(2) 用大容量的钽电容或聚酯电容而不用电解电容作电路板上的充放电储能电容。使用管状电容时,外壳要接地

2016-12-07 17:04:14

。 (21) 弱信号电路,低频电路周围不要形成电流环路。 (22) 信号都不要形成环路,如不可避免,让环路区尽量小。 (23) 每个集成电路一个去耦电容。每个电解电容边上都要加一个小的高频旁路

2018-09-18 15:40:54

1.PCB设计之电容的结构和特性给导体加电位,导体就带上电荷。但对于相同的电位,导体容纳电荷的数量却因它本身结构的不同而不同。导体能够容纳电荷的能力称为PCB设计之电容。 通常,某导体容纳的电荷Q

2019-08-13 10:49:30

。对于小电容,因去耦半径很小,应尽可能的靠近需要去耦的芯片,这正是大多数资料上都会反复强调的,小电容要尽可能近的靠近芯片放置。 PCB布局时去耦电容摆放技巧与安装 尖峰电流的抑制方法 1、在电路板

2023-04-11 16:26:00

振或钟振)要尽量靠近用到该时钟的器件;⑥. 在每个集成电路的电源输入脚和地之间,需加一个去耦电容(一般采用高频性能好的独石电容);电路板空间较密时,也可在几个集成电路周围加一个钽电容。⑦. 继电器线圈

2014-09-23 09:32:40

尽量短,去耦电容引脚尽量短。 (18) 关键的线要尽量粗,并在两边加上保护地。高速线要短要直。 (19) 对噪声敏感的线不要与大电流,高速开关线平行。 (20) 石英晶体下面以及对噪声敏感的器件

2018-11-28 17:05:55

,去耦电容引脚尽量短。 (18) 关键的线要尽量粗,并在两边加上保护地。高速线要短要直。 (19) 对噪声敏感的线不要与大电流,高速开关线平行。 (20) 石英晶体下面以及对噪声敏感的器件下面不要

2018-12-21 09:29:36

经常听说pcb设计要加泪滴,至今任然不知道什么是泪滴,它长啥样啊,有没有图示?要怎样加呢?

2015-07-22 19:36:35

` 本帖最后由 eehome 于 2013-1-5 10:08 编辑

去耦电容和旁路电容的区别`

2012-08-14 11:49:42

信号完整性之去耦电容与旁路电容

2019-11-19 14:52:05

去耦电容分为哪几种?如何去放置去耦电容呢?在设计中如何防止上电及正常工作时出现总线冲突呢?

2021-11-03 07:17:04

一些。每10片左右集成电路要加一片充放电电容,或1个蓄能电容,可选10μF左右。最好不用电解电容,电解电容是两层薄膜卷起来的,这种卷起来的结构在高频时表现为电感。要使用钽电容或聚碳酸酯电容。去耦电容的选用

2012-03-08 23:42:09

去耦电容和旁路电容的区别详解

2017-01-19 09:06:12

电子线路中的同一个电容,有时候会称它去耦电容,有时候又会称它为旁路电容。 电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,但是,当我们从不同的角度去看时,它所起的作用是不同的,所以才有

2021-05-25 06:14:19

去耦电容在PCB板设计中的应用在板设计中应充分考虑电磁兼容方面的问题,合理地使用去耦电容在PCB板防止电磁干扰中具有重要作用, 本文就去耦电容的容量及其具体应用作了较为全面、详细的叙述,同时还介绍了增强去耦电容效果的一些实用方法。[hide][/hide]

2009-12-09 14:08:29

去耦电容的有效使用方法之一是用多个(而非1个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

2019-08-02 06:56:29

去耦和旁路概述:旁路:空载时为了得到想要的输出信号而加的电容。去耦:带载时为了不让负载对前级信号产生影响而加的电容。 耦合的产生:电路中总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路

2015-08-26 21:56:00

何为去耦技术?正确去耦有何必要性?去耦电容有哪些类型?不良去耦技术对性能的影响是什么

2021-03-11 08:14:14

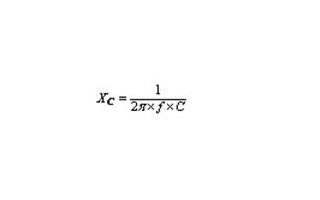

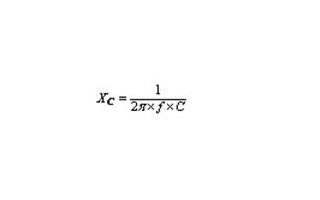

1.电源附近去耦电容的选择很多IC管脚的VCC会增加一个0.1uf的去耦电容,因为电容的滤波曲线在谷底最低的位置滤波效果最好。当IC内部的逻辑门频率是是10MHz-50MHz的时候,0.1uf电容

2021-12-31 07:29:16

的分立电容去耦。在达到200~300 MHz以上频率的电流工作状态后,0.1μF与0.01μF并联的去耦电容由于感性太强,转换速度缓慢,不能提供满足需要的充电电流。 在PCB上放置元件时,必须提供

2018-11-27 15:19:23

请问去耦电容的选择按照这个图上的规则来选对吗

2018-11-19 11:21:51

一个原型设计电路板省去了比较麻烦的去耦电容器;但获得的任何结果都无法与预期结果相匹配。最后,添加一个去耦电容器,问题解决了。什么我们需要使用去耦电容器?它的作用到底是什么?

2021-04-02 07:46:38

解释对应的分别是低频和高频两种情况,但本质上都是希望减小PDN上的电压突变,这就是去耦。2.为什么要有那么多的去耦电容而不是选择一个等效的大电容?这个问题也是要分情况,对于低频来说,很多个小的去耦电容

2019-05-07 06:22:23

去耦旁路电路,不同规格的电容在PCB布局时该怎么摆

2021-03-17 07:33:04

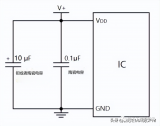

我们都知道小电容滤高频,大电容滤低频,为了更好的滤波效果,一般输入电源或者输出电源都是采用一个大容值电容加一个小容值电容进行滤波,比如1uF+0.1uF; 我们先来了解一下去耦和旁路的区别

2021-01-11 16:31:51

电容在高速 PCB 设计中起着重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,电容通 常分为滤波电容、去耦电容、储能电容等。 1 电源输出电容,滤波电容 我们通常把电源模块

2023-04-20 10:32:14

对于已经知道了电容的具体特性和适用范围,以及去耦原理,那么就知道了去耦的具体方法了吗?不是的,下面我们将讲解一下,具体安装到电路板上之后的去耦原理以及具体如何防止电容的准则!

2021-03-04 08:11:41

4片,每一片各10个管脚,四片共40个电源管脚,单片如图 Demo给出的去耦电容一共十几个,貌似容值还有规律0.1u 0.1p 1p的各四组等 去耦电容如图 我的第一个问题是去耦电容 为什么要这么选择

2016-12-13 09:34:14

扰的影响可降至最低。例如,如果走线宽度为5密耳,则两条并行走线之间的最小距离应为10密耳或更大。随着新材料和新的元器件不断出现,PCB设计人员还必须继续应对电磁兼容性和干扰问题。

技巧4:去耦电容

去

2023-12-19 09:53:34

`各位大神,请问FPGA去耦电容如何布局、布线?1.根据文档,一般去耦电容的数量都少于电源引脚,那么去耦电容要放到哪些管脚旁边呢?2.以下三种方案哪种好?2.1电容放在PCB top层FPGA外围

2017-08-22 14:57:10

想为cyclone V 系列的5CEFA7F27这款FPGA设计去耦电容电路,但是不知道该如何下手。参考了altera公司的一块开发板,给出的FPGA的去耦电容电路如下所示,但是感觉这个去耦电容电路

2016-07-09 10:11:21

亲爱的先生/女士,我们在我们的调制解调器板上使用两个xc7k160t-1ffgi,基于我们使用xpe进行功率估算的逻辑利用率。根据UG483(PCB设计指南)遵循每个组的去耦电容器数量)。第17页表

2020-08-17 10:48:12

一、名词定义:旁路(bypass)电容: pass是通过的意思,bypass指从靠近的地方,从旁边通过。大路不走走小路,主路不走走辅路。所以, 旁路电容可以理解成把信号高频成分旁路掉的电容。去耦

2022-11-04 22:29:20

专业allegro pcb设计,10 看工作经验,要的加Q279312621

2017-09-19 17:05:43

系统需要用到大量的理论知识以及与之相对应的实际应用,这篇文档将会用到许多重要的概念。感谢原作者和中文对照作者们。目录:•PCBS 101•优秀的高速PCB设计练习–电源/地系统的效率–正确使用去耦电容

2017-07-26 17:37:44

PCB设计

VDD_CPU_BIG0/1

01

如下图(上)所示的滤波电容,原理图上靠近RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容,务必放在对应的电源管脚背面,电容GND PAD尽量

2023-08-10 16:37:25

,如不可避免,让环路区尽量小。(23) 每个集成电路一个去耦电容。每个电解电容边上都要加一个小的高频旁路电容。(24) 用大容量的钽电容或聚酷电容而不用电解电容作电路充放电储能电容。使用管状电容时,外壳要接地。

2018-03-10 21:32:11

。 (21) 弱信号电路,低频电路周围不要形成电流环路。 (22) 信号都不要形成环路,如不可避免,让环路区尽量小。 (23) 每个集成电路一个去耦电容。每个电解电容边上都要加一个小的高频旁路电容

2019-02-01 22:35:31

除了电阻之外,在我们的设计中,用的最多的器件便是电容。不要轻视这些小小的电容,他们的作用非常大,如果在电路中用的地方不好,会非常影响电路的功能。 在PCB设计过程中电源的管脚为什么要加许多电容?

2019-08-26 11:28:36

什么是PCB中的板级去耦呢?如何设计板级去耦?

2021-01-25 06:33:18

SOIC 的去耦局部的高频滤波器可以优化小小效果,去耦电容 可以减小回路电感经验法则–Via resistance ≈ 1mΩ, Via inductance ≈ 1nHLQFP/LFCSP 去耦

2020-10-13 09:04:13

我在百度百科看到这样一句话:为了防止多级子系统间电源的相互串扰,一般在每级子系统的电源输入端加0.1u的电容来去耦;我就想起我的一个问题,我这几天做了一个功放,前级用LM324放大,后级用

2013-05-09 19:41:13

`关于去耦电容旁路电容的总结`

2012-08-20 14:01:15

一般去耦电容的容量选取原则是什么?

2021-06-08 06:38:27

怎么分清滤波电容、去耦电容、旁路电容?其实并不难~

2021-01-22 07:53:58

用于电容传感器接口的模拟前端元件有哪些?基于PCB设计的电容传感器

2021-04-22 06:48:21

通用电容传感器模拟前端测量方法用于电容传感器接口的模拟前端元件基于PCB设计的电容传感器

2021-04-09 06:17:02

Walt Kester在上篇文章中,我们介绍了去耦的基础知识及其在实现集成电路(IC)期望性能方面的重要性。在本篇文章中,我们将详细探讨用于去耦的基本电路元件——电容。实际电容及其寄生效应图1所示为

2018-10-19 10:58:00

,也就是说,对于10MHz以下的噪声有较好的去耦效果,对40MHz以上的噪声几乎不起作用。1μF、10μF的电容,并行共振频率在2MHz以上,去除高频噪声的效果要好一些。每10片左右集成电路要加一片充放电电容

2018-12-07 09:39:59

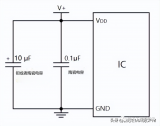

集成电路的电源,地之间都要加一个去耦电容。去耦电容有两个作用:一方面是本集成电路的蓄能电容,提供和吸收该集成电路开门关门瞬间的充放电能;另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容为0.1uf

2013-03-08 16:33:18

一、电源滤波技术:常用的滤波措施有:去耦电容、电感、磁珠等。常用的滤波场景有:电源滤波、接口滤波等。在进行PCB设计时,滤波器件的摆放位置相当关键,对于电容类去耦的滤波原则是靠近滤波区域位置放置最佳

2021-11-11 08:03:08

在ug373“Virtex-6 FPGA PCB设计指南”v1.3中,不需要用于Vccaux和Vcco的去耦电容(表2-1至2-2),而在我读过的早期版本中,数字并非都是零(我不记得确切的数字)。这些0与ug373以及ML605原理图中的以下描述相矛盾。对此有什么正确的答案?

2020-06-08 11:03:50

电源去耦电容为何要接近IC电源引脚?是什么原因呢?

2023-04-21 17:36:30

电源端为什么要加那么多去耦电容,而不是用一个等效的大电容代替!如输入为5V的电源,并联10个0.1u的电容后接地。为什么不是直接接一个1u的电容而是接10个0.1u电容。论容值 1u=0.1u*10 。求解!!

2023-03-28 16:12:56

找到一个很全方面讲解的。下面这些内容是我转载的一篇关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。 老师问: 为什么去耦电容就近摆放呢? 学生答: 因为它有有效半径哦,放

2019-09-06 18:13:24

和供电线阻抗 (2)匹配去耦电容 三、何为去耦电容 在IC(或电路)电源线端和地线端加接的电容称为去耦电容。 四、去耦电容如何取值 去耦电容取值一般为0.01~0.1uf,频率越高,去耦电容值越小

2017-05-04 10:48:07

在设计的时候 是不是板子上加的去耦电容越多越好?我看原理图工程师有的地方加很多

2019-05-08 04:15:39

本资料包括在高速PCB设计中电源/地的设置要求,正确使用去耦电容的方法,分析了电阻,电容在高速设计中的特性;混合信号布线中的接地方式,电源的滤波及去耦方式;小信号布线走线损耗和预防PCB温度问题。

2019-03-25 15:51:27

电容在高速PCB设计中的应用:探讨高速PCB设计电容的应用。电容是电路板上不可缺少的一个部分,并且起到了至关重要的作用,探讨他具备至关重要的价值。您在设计中是否有这样

2009-08-16 13:11:56 0

0 高速PCB设计电容的应用,很有参考意义

2016-12-16 22:07:10 0

0 高速PCB设计电容的应用

2017-01-28 21:32:49 0

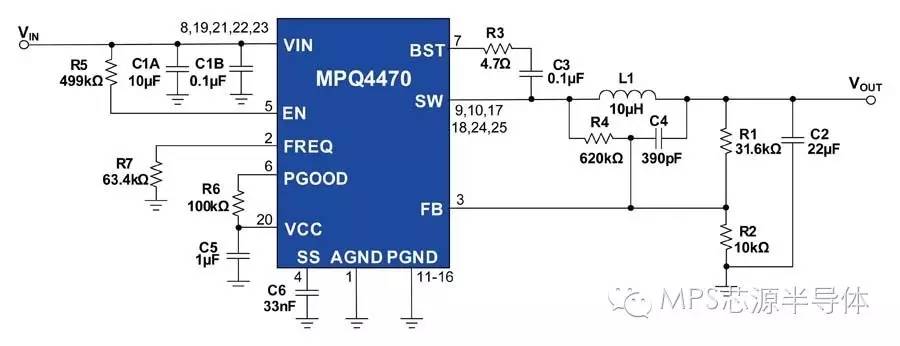

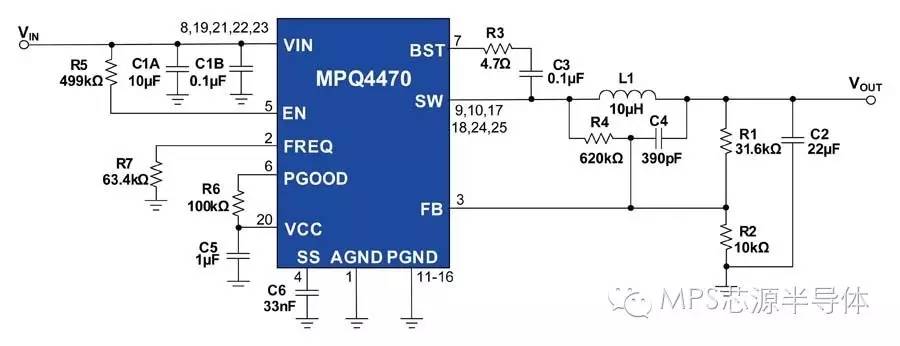

0 MPQ4470采用对称的输入引脚配置,使其在PCB设计时可以放置对称电容,不仅减小了高频环路的面积,而且对称的环路也抵消了大部分的电磁辐射,EMI性能因此得到了很大的提升。配以适当的输入EMI滤波器

2019-10-11 17:05:08 3465

3465

小编给大家分享一下PCB设计电容中必须要知道的知识点,期待对大家的PCB设计有作用。 去耦电容:电源附近的 旁路电容:芯片的电源管脚根部,10-0.1-0.01uF电容组,用于滤除高频噪声,防止自己

2020-08-12 10:38:44 6857

6857

今天给大家分享的是:去耦电容,去耦电容PCB设计和布局。

2023-07-05 09:37:14 888

888

其中一个附属文件就可能包含PCB设计用到全部去耦电容。如果电容数低于或高于期望值,就将在可能出现电源线dv/dt问题地方标注红色记号。

2023-10-31 15:06:37 159

159 高速PCB设计电容的应用

2022-12-30 09:22:16 29

29 高速PCB设计电容的应用

2023-03-01 15:37:57 2

2 本篇介绍PCB设计时处理去耦电容和旁路电容的注意事项。

去耦电容(另见退耦电容、缓冲电容、储能电容等),可以放置在电源电路公共出口处,或者外部电源输入PCB的连接器旁。较大的电路板可以放置多个,但通常2、3个就够了。

2023-11-21 15:33:26 392

392

电子发烧友App

电子发烧友App

评论