本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB设计。

2014-07-24 11:11:21 4410

4410

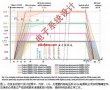

和 x16 配置中均可提供高达 2133Mbps 的数据传输速率,并可与1.5V DDR3实现100%兼容。目前,华邦的 DRAM 产品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR2

2022-04-20 16:04:03 2554

2554

导读:DDR5协议发布已经有一段时间了,其中的变化还是比较大的,地址信号采取了ODT的端接形式,本篇文章为大家仿真一下DDR5地址信号。同时,我也推荐大家关注我在仿真秀原创的精品课《DDR3/4/5系列信号完整性仿真24讲》,让你清楚掌握DDR协议和仿真关键技术要点。

2022-12-01 10:24:03 933

933 DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 464

464

DDR2 DDR3 dimm接口封装文件,金手指接口

2017-12-03 22:22:02

本次设计中CPU的封装为BGA844-SOC-Y,DDR2的封装为FBGA84,DDR2的控制总线采用星形连接,使用的PCB软件为AltiumDesigner10

2019-07-30 06:29:28

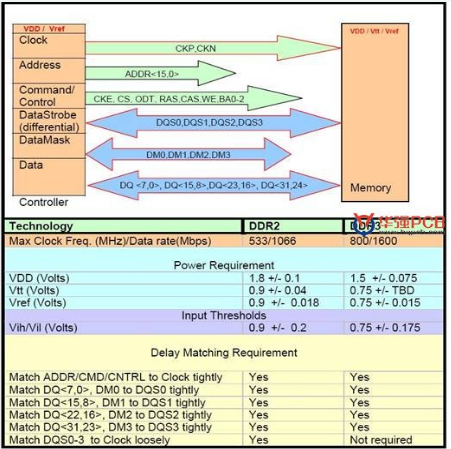

DDR2设计原理 DDR2 designBasic knowledge? Source Sync Bus Analysis? On-Die Terminations (ODT)? Slew Rate

2009-11-19 09:59:04

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:53:43

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-03-12 16:05:56

江山科技最新推出JS-9500内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条,笔记本

2009-08-17 22:58:49

概述: JS-9300A内存检测仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测

2009-03-13 15:46:57

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:50:27

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条, 内存

2009-02-10 22:55:45

江山科技最新推出JS-9500内存测试仪(SD/DDR/DDR2/DDR3)为领先业界的软硬件测试系统,采用国际内存业界最先进自动储存器测试程序,能快速、准确检测内存条,笔记本

2009-08-17 23:00:19

了极大的挑战。 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性

2014-12-15 14:17:46

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间不需要考虑等长;地址、控制、时钟信号:地址、控制

2019-06-03 08:14:09

阻抗的连续性;2)禁止所有信号线跨越不同的电源平面;3)避免其它类型的信号线穿越 DDR 走线区域;4)DQS 不要与 CLK 信号相邻;5)注意蛇形走线的线与线中心间距保持 3W 线距;6)主芯片

2019-09-20 09:05:04

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

,DDR2还引入了三项新的技术,它们是OCD、ODT和Post CAS。1.OCD(Off-Chip Driver):也就是所谓的离线驱动调整,DDR II通过OCD可以提高信号的完整性。DDR II

2011-02-27 16:47:17

[size=14.3999996185303px]我有个ARM的板子,DDR2和NAND的数据线是复用的,这样PCB走线的时候,除了原来DDR2高速信号走线阻抗和等长以外,还需要特别注意什么吗。NAND的线长是不是不算入DDR2总的线长中。

2016-10-10 17:09:28

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-25 06:51:11

所谓“万丈高楼平地起”,想从事信号完整性工作就必须对整个信号完整性的理论基础有一个很明晰的了解。至少要熟读几本信号完整性方面的书籍,了解什么是信号完整性;了解信号完整性研究的对象和内容是什么;信号

2019-09-03 17:54:59

等长解析(1/2/4片)5、DDR、DDR2、DDR3、DDR4区别与联系6、你问我答10个关于DDR设计问题现场答疑`

2018-10-10 11:49:20

Cadence 平板电脑6层板DDR3 PCB layout设计视频教程下载链接链接:http://pan.baidu.com/s/1FJNhO密码:jfa3播放密碼:QQ521122524完整

2015-07-30 21:34:09

DR2与DDR有哪些区别?DDR3与DDR2的区别是什么?

2021-10-26 06:15:07

大家好,我们可以在这里讨论使用DDR2 / DDR3内存与FIFO(我的好奇心)的差异/优点/缺点。以上来自于谷歌翻译以下为原文Hi All, Can we discuss here

2019-02-14 06:14:38

不同的标准外,还应该能够提供动态的OCT和可变摆率,以此来管理信号的上升和下降时间。结论DDR3在未来即将超越DDR2的使用,高端FPGA提供的低成本、高效能、高密度和良好的信号完整性方案必须满足JEDEC读写均衡要求。来源:EDN CHINA

2019-04-22 07:00:08

hyperlynx Sigrity信号完整性仿真之高速理论视频教程Allegro 平板电脑DDR3 PCB设计视频教程链接:https://pan.baidu.com/s/1P1elXupWFQ8KNh-u7QhCDg 密码:fc5q

2018-08-25 15:54:28

SDRAM 相连的是BANK35 的 IO,DDR3 的硬件设计需要严格考虑信号完整性,我们在电路设计和 PCB设计的时候已经充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,保证DDR3 高速

2021-07-30 11:23:45

DDR3的频率就是外频的8倍 133=1066DDR2和DDR3的区别内存相对于DDR2内存,其实只是规格上的提高,并没有真正的全面换代的新架构。DDR3接触针脚数目同。DDR2皆为240pin。但是

2014-12-30 14:35:58

DDR3的频率就是外频的8倍 133=1066DDR2和DDR3的区别内存相对于DDR2内存,其实只是规格上的提高,并没有真正的全面换代的新架构。DDR3接触针脚数目同。DDR2皆为240pin。但是

2014-12-30 14:36:44

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关

2019-07-30 07:00:00

使用VTT电源。一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。DDR2的地址和控制信号线如果是多负载的情况下

2018-08-09 22:09:18

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

用DDR3获得更好的性能,DDR3的可用性可能不如DDR2,但我不想在部件选择中出错并选择一个已知的部件,并得到MIG发电机的支持在ISE。最好的祝福,埃尔维斯·道森以上来自于谷歌翻译以下为原文Hi, I

2019-05-21 06:16:43

本手册以 DDR3 器件为例讲解硬件设计方法,包括 FPGA I/O 分配、原理图设计、电源网络设计、PCB 走线、参考平面设计、仿真等,旨在协助用户快速完成信号完整性好、低功耗、低噪声的高速存储

2022-09-29 06:15:25

时,DDR2对信号完整性[4]的要求比较高,在很多地方都要求T型连接;而DDR3引入了write leveling的模块[5],专门用于各个模块间时钟的对齐,因此可以采用菊花链的连接方式,大大方便了PCB

2018-08-30 09:59:01

出现问题时,不知道从哪里下手找原因。而这篇文章的目的就是简单的探讨DDR2的使用,以及DDR2使用中会遇到的问题。其中这篇文章包含以下几个方面1 : 如何生成IP2 : 使用IP的注意事项。3 : 关于

2015-03-16 20:21:26

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些

2019-08-09 07:42:01

你好 ! 我想设计一个框架,我们想出的设计具有以下特点: 1:DDR3(MT47H64M16HR-3 ofmicron inc。) 2:USB 但我不知道如何设计DDR2原理图,而且我还没有找到关于

2019-09-06 07:55:42

如何进行兼顾电源影响的DDR4信号完整性仿真

2021-01-08 07:53:31

我生成了DDR2设计但是当我在硬件上运行它时,led_error输出总是很高,表明读回失败。为了缩小问题范围,我需要查看接口中的总线传输,但是当我尝试将chipcope信号挂钩到DDR2总线实现失败

2019-05-10 14:25:23

本人菜鸟初学者一个,求大神帮忙设计一个ddr2,ddr3供电电源,查了很多资料,自己也尝试着设计了一下,但是发现问题很多,只能求助各位了,能帮我设计的本人必有酬谢,200元话费。。。。。 求会的大神直接联系我qq447420097

2014-03-25 23:02:56

DDR,DDR2,DDR3,DDR4,LPDDR区别文所有权归作者Aircity所有1什么是DDRDDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师

2021-09-14 09:04:30

PCB布线设计的好坏直接影响到硬件电路能否正常工作或运行多快的速度。而在高速数字PCB设计中,DDR2是非常常见的高速缓存器件,且其工作频率很高本文将针对DDR2的PCB布线进行讨论。DDR2

2016-12-26 16:56:05

针对DDR2-800和DDR3的PCB信号完整性设计

2012-12-29 19:12:39

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

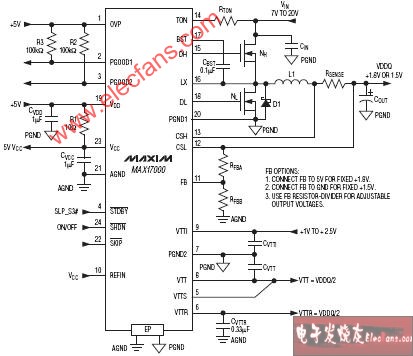

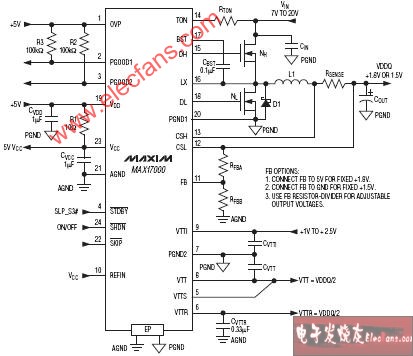

79 MAX17000 完备的DDR2和DDR3电源管理方案

MAX17000 概述

MAX17000脉宽调制

2009-01-22 12:59:21 1018

1018

台湾DRAM厂商大举转产DDR3

2010年PC主流内存标准从DDR2向DDR3的转换正在逐步成为现实。据台湾媒体报道,由于下游厂商的DDR2订单量近期出现急剧下滑,多家台系DRAM芯片

2010-01-18 09:25:13 602

602 DDR2乏人问津 DRAM厂抢转产能

DDR2和DDR3 1月上旬合约价走势迥异,DDR2合约价大跌,DDR3却大涨,凸显世代交替已提前来临,将加速DDR2需求急速降温,快速转移到DDR3身上,

2010-01-18 16:04:44 1094

1094 DDR2芯片价格有望在下半年超过DDR3

报道,威刚主席Simon Chen今天表示,随着DRAM制造商把重点放在DDR3芯片生产上,DDR2芯片的出货量将开始减少,其价格有望在今年下半

2010-02-05 09:56:18 955

955 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2010-03-24 16:06:36 1381

1381 金士顿:DDR2/DDR3价格可能会继续上涨

据报道,存储大厂金士顿亚太地区副总裁Scott Chen近日表示,虽然1Gb DDR2/DDR3的芯片价格已经超过了3美元大关,

2010-04-09 09:11:05 676

676 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4257

4257

MAX17000A脉宽调制(PWM)控制器为笔记本电脑的DDR、DDR2、DDR3存储器提供完整的电源方案。该器件集成了一路降压控制器、一路可

2010-11-25 09:26:24 682

682

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,DDR4雏形初现。但是在我们利用这些新技术前,设计人员必须了解如何

2011-07-11 11:17:14 5033

5033

本文章主要涉及到对 DDR2 和DDR3 在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB 层数,特别是4 层板

2011-07-12 17:31:10 0

0 SDRAM, DDR, DDR2, DDR3 是RAM 技术发展的不同阶段, 对于嵌入式系统来说, SDRAM 常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3 中,目前基本上已经以DDR2 为主导,相信不久DDR3 将全面取代

2012-01-16 14:53:01 0

0 总结了DDR和DDR2,DDR3三者的区别,对于初学者有很大的帮助

2015-11-10 17:05:37 36

36 针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank

2017-11-07 10:48:51 52790

52790

SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。

2017-11-17 13:15:49 25152

25152 本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

2018-02-06 18:47:57 2638

2638

本节提供了DDR2接口作为一个PCB设计和制造的时间规范规范。设计规则限制PCB轨迹长度、PCB跟踪歪斜、信号完整性、串扰,信号定时。这些规则,之后,在一个可靠的DDR2内存系统的结果而不需要

2018-04-18 14:26:10 4

4 性能和成本达到最佳收益的选择,就是在布线方面,DDR3需要注意的问题比DDR2就略多。这里对AM335x关于DDR3的软硬件设计资源以及这些注意事项做一个简单汇总

2018-04-24 16:08:20 18

18 DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17:00 8959

8959

突发长度,由于DDR3的预期为8bit,所以突发传输周期(BL,Burst Length)也固定位8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3为此增加了

2018-06-21 09:20:54 14616

14616

针对 DDR2高速电路中存在的信号完整性问题进行了分析,提出了PCB设计要点。并以单个DDR2存储器与控制器间的 PCB设计为例,对如何在减少仿真工作的情况下成功完成一个可用的设计进行了论述。

2019-03-04 08:00:00 0

0 DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技术,明显提高了存储带宽;其工作电压为1.5V,保证相同频率下功耗更低。

2019-06-25 15:49:23 1736

1736 DDR3 SDRAM是DDR3的全称,它针对Intel新型芯片的一代内存技术(但目前主要用于显卡内存),频率在800M以上。DDR3是在DDR2基础上采用的新型设计,与DDR2 SDRAM相比具有功耗和发热量较小、工作频率更高、降低显卡整体成本、通用性好的优势。

2019-10-29 08:00:00 0

0 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 注意事项。 信号完整性问题和印刷电路板 频率 在低频下,您应该不会遇到信号完整性方面的任何重大问题。但是,随着信号速度的提高,您会获得更高的频率,这会影响系统的模拟和数字属性。在较高的频率下,您可能会遇到反射,地面反弹,串扰和振铃

2020-09-21 21:22:51 2094

2094 用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准

2021-03-19 08:44:50 13

13 15V、双通道 3A 单片同步降压型稳压器为 DDR1、DDR2 或 DDR3 存储器供电

2021-03-20 15:29:10 6

6 用于 DDR 终端的高效率 ±6A 开关稳压器符合 DDR / DDR2 / DDR3 标准

2021-03-21 05:20:16 4

4 本文章主要涉及到对DDR2和DDR3在PCB设计时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。 文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中

2021-03-25 14:26:01 3864

3864

引言:本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信号完整性及时序考虑等问题。 1.介绍 Artix-7和Spartan-7器件有各种各样的软件包

2021-08-26 10:12:21 3289

3289

DDR4电路板设计与信号完整性验证挑战

2021-09-29 17:50:07 10

10 DDR,DDR2,DDR3,DDR4,LPDDR区别作者:AirCity 2019.12.17Aircity007@sina.com 本文所有权归作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 本手册以 DDR3 器件为例讲解硬件设计方法,包括 FPGA I/O 分配、原

理图设计、电源网络设计、PCB 走线、参考平面设计、仿真等,旨在协助用

户快速完成信号完整性好、低功耗、低噪声的高速存储方案的硬件设计。

2022-09-15 10:31:36 3

3 电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 电子发烧友网站提供《完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表.pdf》资料免费下载

2024-03-13 13:58:12 0

0 电子发烧友网站提供《适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表.pdf》资料免费下载

2024-03-13 13:53:03 0

0

正在加载...

电子发烧友App

电子发烧友App

评论