信号完整性问题是高速PCB设计者必需面对的问题。阻抗匹配、合理端接、正确拓扑结构解决信号完整性问题的

2010-10-11 10:43:57 1941

1941

信号完整性是指电路系统中信号的质量。如果在要求的时间内,信号能够不失真地从源端传送到接收端,就称该信号

2010-12-30 15:57:01 883

883

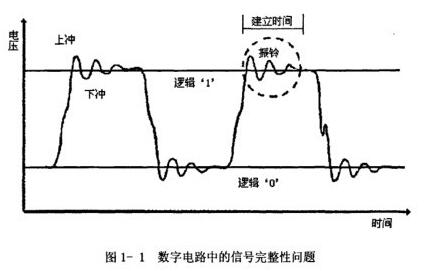

通常说的信号完整性就是指信号无失真的进行传输。前面我们讨论很多信号完整性问题,包括时序、串扰、衰减、反射、电源完整性、EMC等等。

2022-09-29 17:00:06 1045

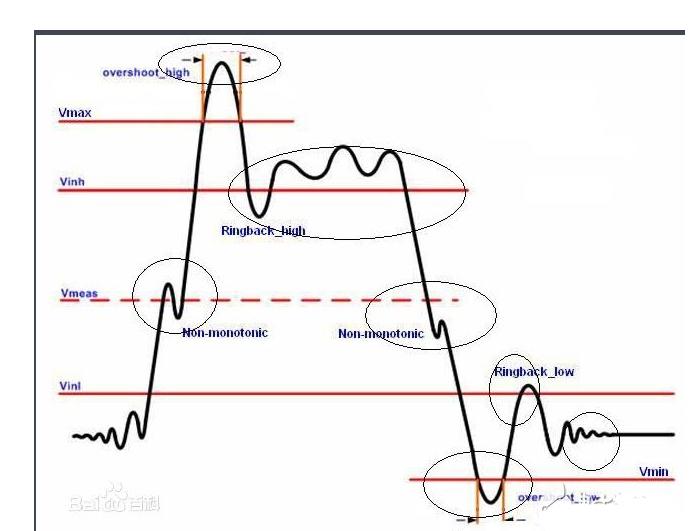

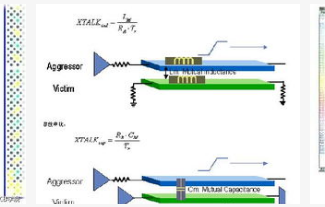

1045 在实际的应用场景中,会遇到多种信号完整性问题,典型问题有如下几种:反射、串扰,电源/地噪,时序等。其中,发射和串扰是引起信号完整性问题的两大主要原因。

2022-10-09 10:56:55 3291

3291 定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同 引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

2023-03-02 09:41:06 1094

1094

PCB中信号完整性分析的基础知识可能不是基本的。信号完整性仿真工具非常适合在原理图和布局设计期间计算不同网络中信号的行为,但您仍然需要采取一些步骤来解释结果。

2023-06-09 10:31:57 628

628

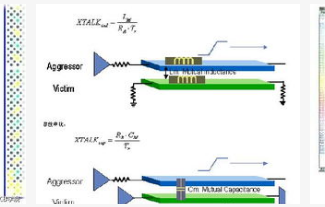

串扰是四类信号完整性问题之一,指的是有害信号从一个线网传递到相邻线网。任何一对线网之间都存在串扰。

2023-09-25 11:29:07 691

691

信号完整性(Signal Integrity,SI)是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。

2023-09-28 11:27:47 1003

1003

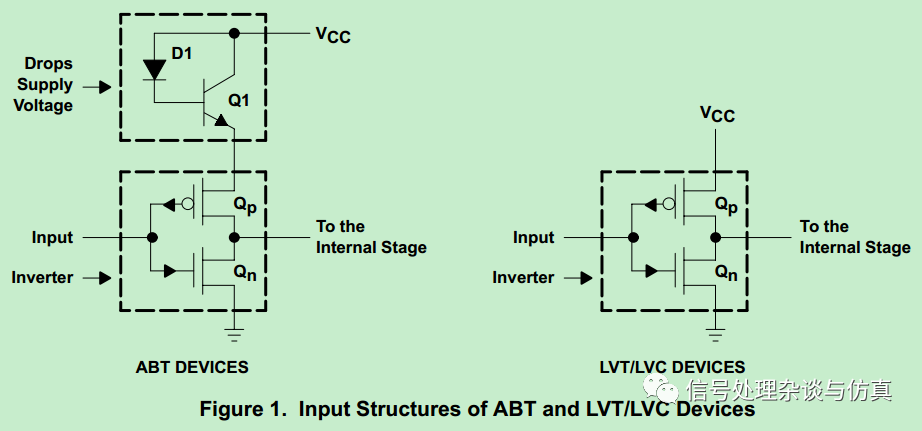

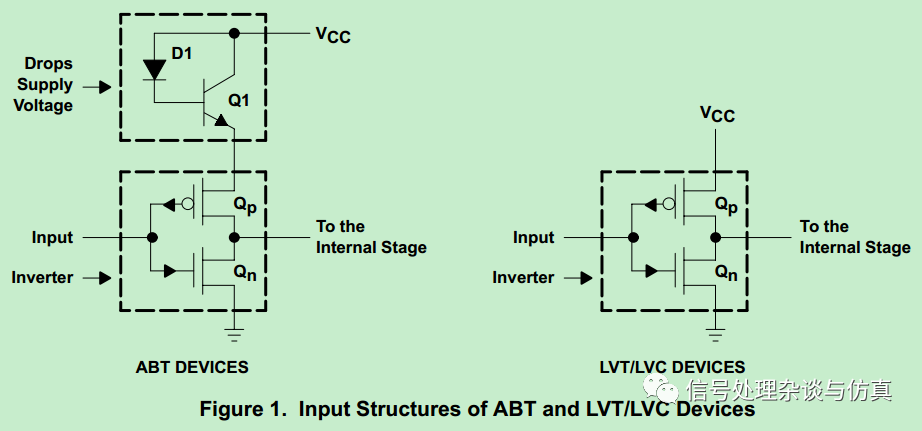

CMOS器件的输入信号上升时间或下降时间统称为输入转换时间,输入转换时间过长也称为慢CMOS输入。如果输入信号上升时间过长,超过器件手册允许的最大输入转换时间,则有可能在器件内部引起大的电流浪涌,造成器件损坏或引起器件输出电平翻转(输入原本为0,输出为1;或者相反情况)。

2023-10-31 10:39:53 560

560

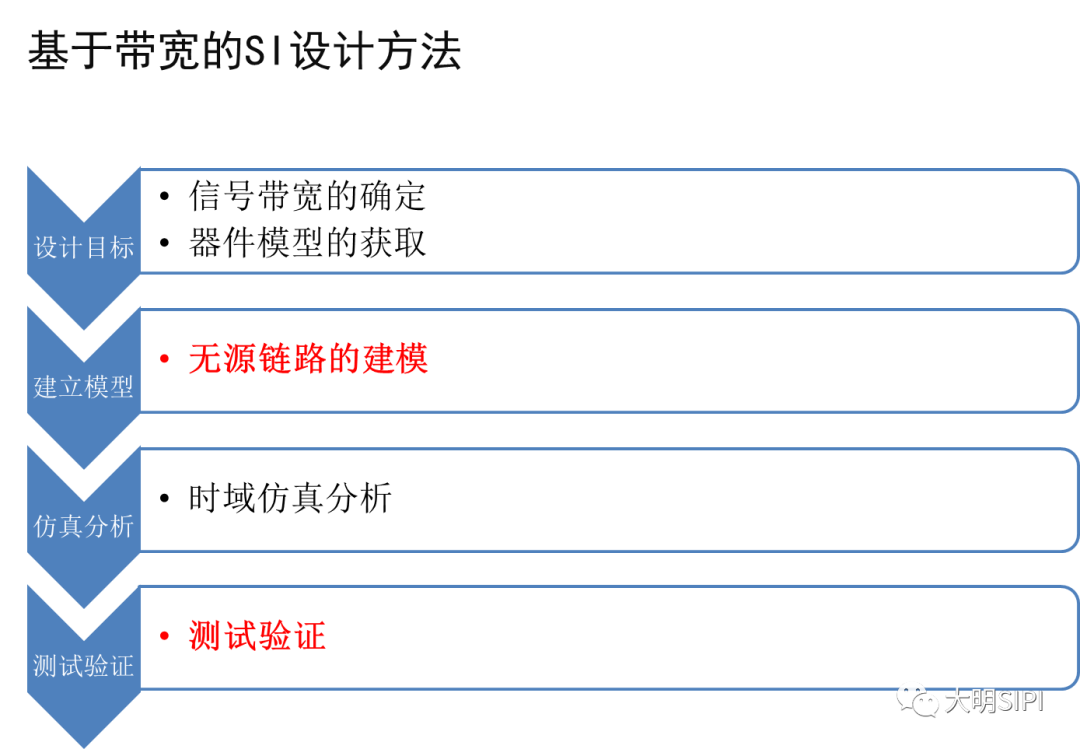

、仿真软件优劣等概况;概述后面诸讲的各种基本概念。同时,简要介绍相关技术资料、国内外最新科研成果、国内出版的原版译著情况等。第二讲 信号/互连线带宽与时频域阻抗 介绍信号完整性的研究对象——上升边

2010-12-16 10:03:11

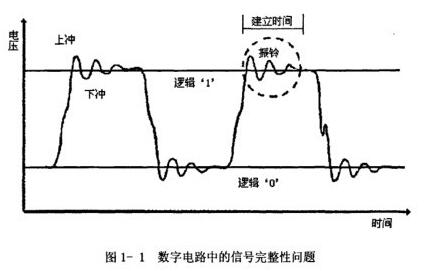

信号完整性问题 1、信号完整性的定义 信号完整性(SignalIntegrity),是指信号未受到损伤的一种状态。它表明信号通过信号线传输后仍保持其正确的功能特性,信号在电路中能以正确的时序和电压

2013-12-05 17:44:44

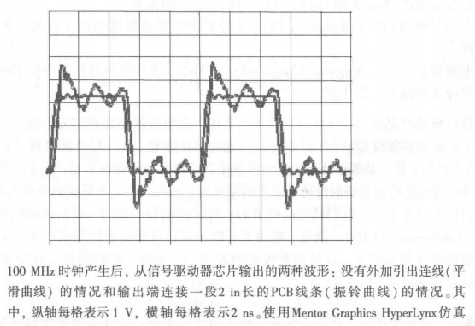

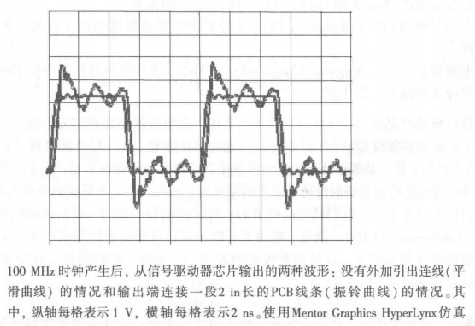

手工连线面成的样机同规范布线的最终印制板产品一样都能正常工作。

但是现在时钟频率提高了,信号上升边也已普遍变短。对大多数电子产品而言,当时钟频率超过100MHz或上升边小于1 ns时,信号完整性效应

2023-09-28 08:18:07

扰、轨道塌陷和电磁干扰。3、随着上升边的减小或者时钟频率的提高,各种信号完整性问题变得更严重,并且更加难以解决。4、由于晶体管越来越小,它们的上升边将越来越短,信号完整性也将成为越来越大的问题,这是

2015-12-12 10:30:56

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-25 06:51:11

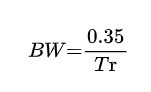

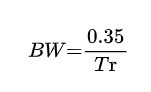

的第一次谐波幅度约为0.6V,第三次谐波的幅度约是0.2V。3、信号的带宽和上升时间的关系为:BW=0.35/RT。例如,如果上升时间是1NS,则带宽是350MHZ。如果互连线的带宽是3GHZ,则它可

2019-07-08 06:05:10

的分析技术主要有:经验法则,例如1nh/1mm 等;解析近似,例如Z0=√L/C,给出IPC 权威机构及传输线分析中重要的解析表达式;数值仿真,给出互连不当与信号不完整的定性定量关系。 一、举办单位

2010-05-29 13:29:11

什么是DSP图像处理系统?DSP图像处理系统中信号完整性的问题是什么?有哪些解决方案?

2021-06-01 06:40:35

信号完整性(Signal Integrity, SI)是指信号在信号线上的质量,即信号在电路中以正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达接收器,则可

2018-11-27 15:22:34

征上升时间就要小于该信号上升时间的50%,这是个简单的经验法则。2.从频域角度看,为了比较好的传输带宽为1GHz的信号,互连线的带宽至少为信号带宽的两倍,即2GHz频域与时域的总结1.上升时间通常

2017-12-06 08:46:10

与理想方波越接近。同理降低信号带宽如删除高频分量,其上升时间会变长。有两种损耗机理:导体损耗和介质损耗。这两种损耗对高频分量的衰减大于对低频分量的衰减。这种选择性衰减使得在互连线中传播的信号的带宽降低

2017-12-01 09:55:07

一般来说:时钟下降沿比上升沿时间短。这是典型的CMOS输出驱动器造成的,为P管和N管的串联,而P管的导通时间短。一般来说,时钟下降沿比上升沿更容易出现信号完整性的问题,如果将N沟做得比P沟长,可使

2017-11-29 08:46:06

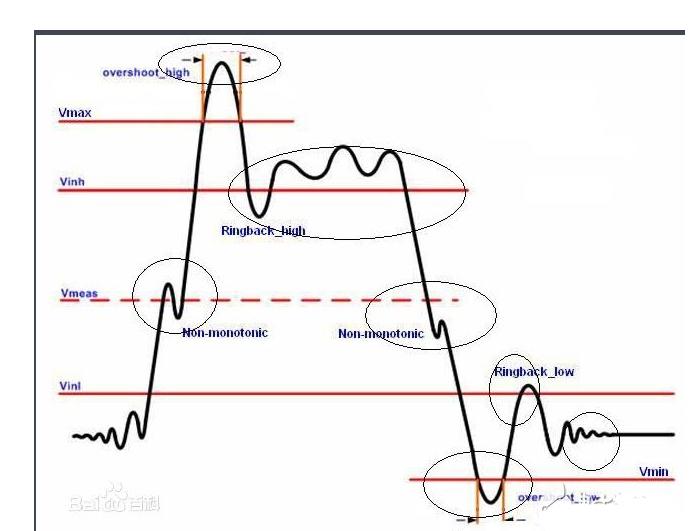

、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。信号完整性包含:1、波形完整性(Waveform integrity)2、时序完整性(Timi...

2021-12-30 08:15:58

的时延有关,《信号完整性分析》中描述说,“当传输线延时Td>信号上升时间的20%时,就要开始考虑由于导线没有终端端接而产生的振铃噪声。当时延大于上升时间的20%时,振铃会影响电路功能,,必须加以控制,否则这是造成信号完整性问题的隐患。吐过Td

2019-05-22 06:07:06

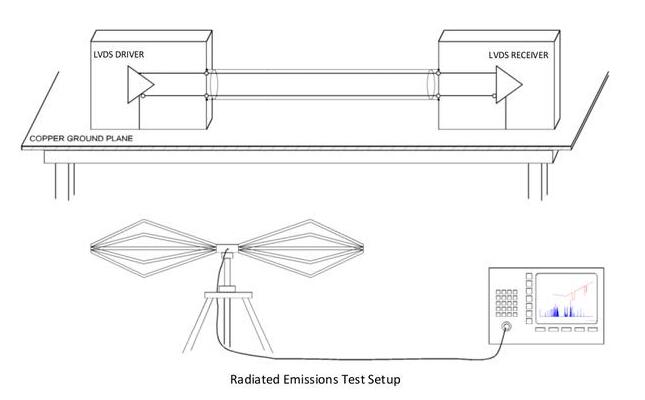

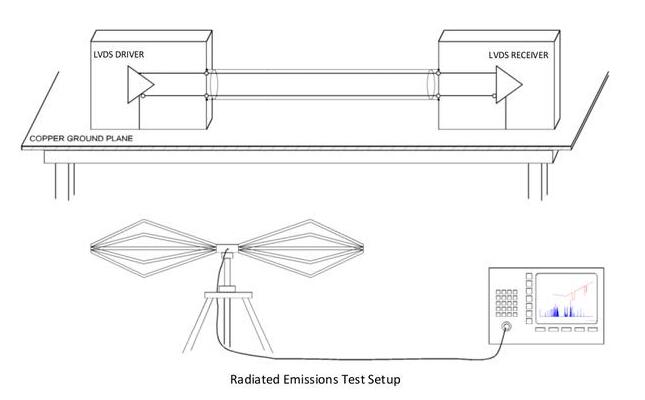

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2021-10-26 06:59:21

在高速设计中,如何解决信号的完整性问题?

2009-09-06 08:42:10

引言信号完整性是指电路系统中信号的质量。如果在要求的时间内,信号能够不失真地从源端传送到接收端,就称该信号是完整的。随着半导体工艺的迅猛发展、IC开关输出速度的提高,信号完整性问题(包括信号过冲

2015-01-07 11:30:40

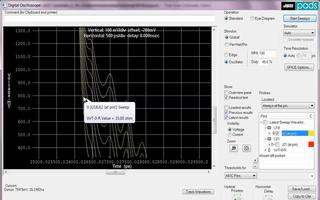

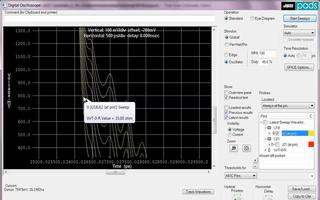

1 示波器探头的上升时间和带宽示波器主要的限制为三个方面:灵敏性的不足、输入电压的幅度不够大、带宽限制。只要数字测试中的灵敏度不是特别的高,一般示波器的灵敏度是满足要求的。在高电平时,数字信号一般

2018-04-19 10:42:59

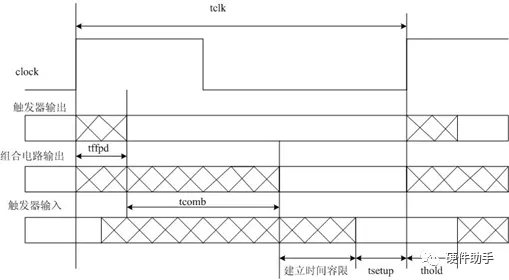

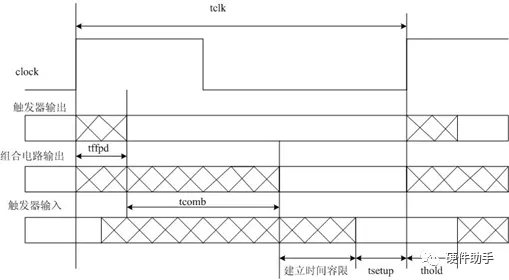

时序分析-- 信号完整性问题(SI)

2014-05-16 10:44:11

解决背板互连中信号完整性问题的两种方案

2019-09-16 09:08:59

如何快速解决高速系统的信号完整性问题?

2021-04-27 06:03:49

:介绍信号完整性的研究对象——上升边,介绍上升边的宽带信号特点。介绍信号带宽与信号频率/周期的表达式。介绍信号带宽、互连线带宽、本证上升时间、互连线模型带宽、测量带宽等的应用。第三讲 电感与地弹、趋肤

2010-11-09 14:21:09

高速PCB设计的信号完整性问题 随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成爲传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具

2012-10-17 15:59:48

高速pcb的信号完整性问题主要有哪些?应如何消除?

2023-04-11 15:06:07

高速电路信号完整性分析与设计—信号完整性仿真仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上升沿从20%~80%VCC的时间,一般是ns级或

2009-09-12 10:31:31

在高速电路设计中信号完整性分析由于系统时钟频率和上升时间的增长,信号完整性设计变得越来越重要。不幸的是,绝大多数数字电路设计者并没意识到信号完整性问题的重要性,或者是直到设计的最后阶段才初步认识到

2009-10-14 09:32:02

高速数字硬件电路设计中信号完整性在通常设计的影响是什么?高速电路设计中信号完整性面临的挑战有哪些?怎么处理?

2021-04-22 06:26:55

本文分析了高速电路设计中的信号完整性问题,提出了改善信号完整性的一些措施,并结合一个VGA视频分配器系统的设计过程,具体分析了改善信号完整性的方法。

2021-06-03 06:22:05

本文分析了高速电路设计中的信号完整性问题,提出了改善信号完整性的一些措施,并结合一个VGA视频分配器系统的设计过程,具体分析了改善信号完整性的方法。

2021-06-04 06:16:07

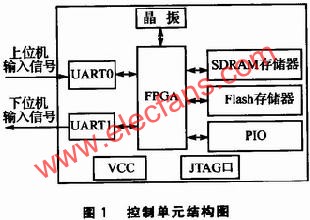

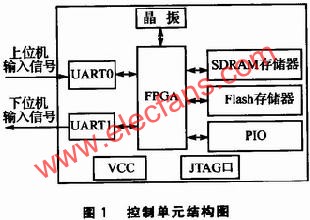

深入研究高速数字电路设计中的信号完整性问题;分析电路中破坏信号完整性的原因;结合一个实际的DSP 数据采集系统, 阐述实现信号完整性的具体方法。

2009-04-15 09:08:03 16

16 深入研究高速数字电路设计中的信号完整性问题;分析电路中破坏信号完整性的原因;结合一个实际的DSP 数据采集系统, 阐述实现信号完整性的具体方法。

2009-05-18 13:24:58 17

17 由于系统时钟频率和上升时间的增长,信号完整性设计变得越来越重要。不幸的是,绝大多数数字电路设计者并没意识到信号完整性问题的重要性,或者是直到设计的最后阶段才

2009-09-18 09:28:46 0

0 高速电路信号完整性分析与设计—信号完整性仿真:仿真信号仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上

2009-10-06 11:19:50 0

0 信号完整性原理分析

什么是“信号完整性”?在传统的定义中“完整性(integrity)”指完整和末受损的意思。因此,具有良好完整性的数字信号应是干净,

2009-11-04 12:07:06 210

210 信号完整性基础根据定义, “完整性”是指“完整和无损害的”。 同样,一个具有良好的完整性的数字信号有干净、快速的上升沿;稳定和有效的逻辑电平;准确的时间位置和

2010-08-05 15:11:33 242

242 什么是信号完整性

信号完整性(Signal Integrity):就是指电路系统中信号的

2009-06-30 10:23:18 4852

4852

在高速设计中,如何解决信号的完整性问题?

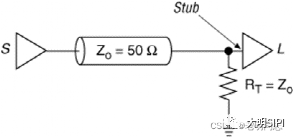

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻

2010-01-02 11:15:06 1097

1097

BOB购买了一台标称300MHZ的示波器,探头的标称值是300MHZ,两个指标均为3DB带宽。问:对于上升时间为2NS的信号,这个组合信号的影响如何?

2010-06-03 16:20:14 779

779

BOB购买了一台标称300MHZ的示波器,探头的标称值是300MHZ,两个指标均为3DB带宽。问:对于上升时间为2NS的信号,这个组合信号的影响如何?

2010-07-05 11:44:24 2072

2072

文章介绍了数字电路设计中的信号完整性问题, 探讨了振铃、边沿畸变、反射、地弹、串扰和抖动等各种信号完整性问题的成因和抑制措施。针对常见的反射和串扰给出了较为详细的分

2011-09-07 16:14:58 104

104 多长的走线才是传输线?这和信号的传播速度有关,在FR4板材上铜线条中信号速度为6in/ns。简单的说,只要信号在走线上的往返时间大于信号的上升时间,PCB上的走线就应当做传输线来处

2011-11-23 17:45:06 3533

3533

本文就谈谈一个基础概念:信号上升时间和信号带宽的关系。对于数字电路,输出的通常是方波信号。方波的上升边沿非常陡峭,根据傅立叶分析,任何信号都可以分解成一系列不同频

2011-11-30 15:48:44 3607

3607

在当前的高工作频率下,影响信号上升时间、脉宽、定时、抖动或噪声内容的任何事物都会影响整个系统的可靠性。为保证信号完整性,必需了解和控制信号经过的传输环境的阻抗。阻

2011-12-21 14:30:46 131

131 本书全面论述了信号完整性问题。主要讲述了信号完整性和物理设计概论,带宽、电感和特性阻抗的实质含义,电阻、电容、电感和阻抗的相关分析,解决信号完整性问题的四个实用技术手段,物理互连设计对信号完整性

2015-11-10 17:36:24 0

0 所谓“万丈高楼平地起”,说的就是这个道理,想从事信号完整性工作就必须对整个信号完整性的理论基础有一个很明晰的了解。至少要熟读几本信号完整性方面的书籍,了解什么是信号完整性;了解信号完整性研究的对象和内容是什么;信号完整性与哪些因素有关系;信号完整性会影响到产品的哪一个方面;等等。

2017-08-29 15:47:22 20096

20096 随着半导体工艺的进步,晶体管特征尺寸将持续减小,因而信号的上升边必然持续减小且时钟频率也必然持续提高。相应的时钟频率的不断提高则又促进了上升边的不断下降,因此也就引发了愈发严重的信号完整性问题

2017-11-09 16:24:32 13

13 引起的。主要的信号完整性问题包括反射、振铃、地弹、串扰等。 源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面

2017-11-16 13:24:51 0

0 现在的高速数字系统的时钟频率可能高达数百兆Hz,其快斜率瞬变和极高的工作频率,以及很大的电路密集度,必将使得系统表现出与低速设计截然不同的行为,出现了信号完整性问题。破坏了信号完整性将直接导致信号

2017-12-01 17:24:00 1390

1390

的时序可知,如果信号在稳态时间(为了正确识别和处理数据,IC要求在时钟边沿前后输入数据保持不变的时间段)内发生了较大的跳变,IC就可能误判或丢失部分数据。若信号具有良好的信号完整性,则电路具有正确的时序关系和信号幅度,数据不会出现错误的

2017-12-04 11:42:06 0

0 信号的上升时间,对于理解信号完整性问题至关重要。

2018-04-02 17:45:57 13820

13820

信号上升时间并不是信号从低电平上升到高电平所经历的时间,而是其中的一部分。业界对它的定义尚未统一,最好的办法就是跟随上游的芯片厂商的定义,毕竟这些巨头有话语权。

2018-04-11 11:16:00 8090

8090

信号上升时间并不是信号从低电平上升到高电平所经历的时间,而是其中的一部分。业界对它的定义尚未统一,最好的办法就是跟随上游的芯片厂商的定义,毕竟这些巨头有话语权。通常有两种:第一种定义为10-90

2019-06-26 15:40:06 1515

1515

当信号在高速PCB板上沿传输线传输时可能会産生信号完整性问题。布线拓扑对信号完整性的影响,主要反映在各个节点上信号到达时刻不一致,反射信号同样到达某节点的时刻不一致,所以造成信号质量恶化。一般来讲,星型拓扑结构,可以通过控制同样长的几个分支,使信号传输和反射时延一致,达到比较好的信号质量。

2019-06-18 15:09:36 635

635 信号完整性(S i gnal Integri ty,SI)是指信号在信号线上传输的质量。对于数字电路,就是要信号在电路中能以正确的时序和电压做出响应。如果电路中信号能够以要求的时序、持续时间和电压

2019-05-27 13:58:16 1753

1753

当前要创建高难度的电子产品,需要采取战略性的方法来解决信号和电源完整性问题。在 Layout 开始之前提前研究敏感信号中存在的信号完整性问题,有助于实施布线策略、端接方法和叠层选择,并最终减少测试工作量、降低电路板设计遍数、并缩短设计时间。

2019-05-20 06:20:00 2527

2527

使用 HyperLynx® 可以轻松地查找并修复 PCB 上的信号完整性问题。从 PCB Layout 导出设计后,您可以采用批量模式和/或交互模式运行仿真,以查找信号完整性问题。内置的端接器向导

2019-05-16 06:22:00 3879

3879

在PCB信号完整性问题可以很容易地定位和固定使用HyperLynx®。出口你的设计从PCB布局之后,可以以批处理方式运行模拟和/或交互模式发现信号完整性问题。内置的终结者向导可以分析一个拓扑和建议

2019-10-12 07:08:00 2565

2565 信号的第一次谐波幅度约为0.6V,第三次谐波的幅度约是0.2V。 3、信号的带宽和上升时间的关系为:BW=0.35/RT。例如,如果上升时间是1NS, 则带宽是350MHZ。如果互连线的带宽是3GHZ,则它可传输的最短上升时间约为0.1NS。

2020-09-08 10:46:00 1

1 随着电路速度的增加,信号完整性在电子设计中变得更加重要。更快的数据速率和更短的上升/下降时间使信号完整性更具挑战性。信号的失真和降级会对电磁兼容性产生不利影响。随着信号完整性降低,电路辐射和电路抗扰性都可能会增加。

2020-07-09 15:29:48 3296

3296

去的低速时代,电平跳变时信号上升时间较长,通常几个 ns。器件间的互连线不至于影响电路的功能,没必要关心信号完整性问题。

2020-07-15 08:00:00 3

3 PCB基板:PCB构造期间使用的基板材料会导致信号完整性问题。每个PCB基板具有不同的相对介电常数(εr )值。它决定了将信号走线视为传输线的长度,当然,在这种情况下,设计人员需要注意信号完整性威胁。

2020-09-17 15:48:23 2514

2514 本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题? 信号完整性是指高速产品设计中由互连线引起的所有问题。包括以下几部分: 时序 噪声 电磁干扰(EMI) 数据采样

2020-09-18 11:01:48 4328

4328 在这里,我们将讨论潜在的信号完整性问题,它们的来源,理解它们的重要性,以及我们如何分析和解决这些问题。关于电气设计,信号完整性应该集中在两个主要方面:定时和信号质量。

2020-09-26 09:22:36 7239

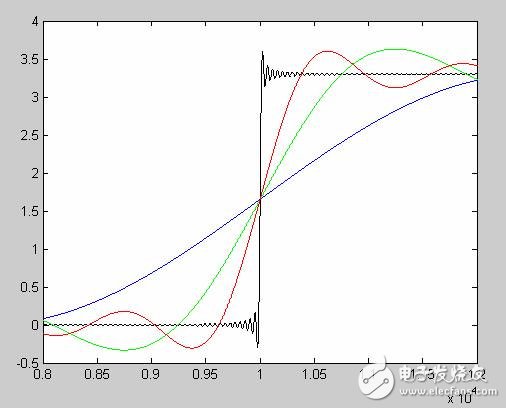

7239 我们在介绍信号完整性的时候通常会说“当传输延时大于六分之一的信号的上升时间时,需要考虑信号完整性问题”,于是乎教科书里面都会配上一副类似于这样表现上升时间或者传输延时与反射的图片: 最开始的时候小陈

2021-04-13 09:46:29 2360

2360

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-20 14:22:53 1011

1011

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

信号完整性是指高速产品设计中由互连线引起的所有问题。包括以下几部分:

时序

噪声

2022-02-09 16:14:50 996

996

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-23 08:45:50 28

28 本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

信号完整性是指高速产品设计中由互连线引起的所有问题。包括以下几部分:

时序

噪声

电磁干扰(EMI

2021-01-26 09:28:30 12

12 信号完整性(SignalIntegrity)就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。

2021-03-14 14:51:31 3520

3520 信号完整性问题与PCB设计说明。

2021-03-23 10:57:06 0

0 、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。信号完整性包含:1、波形完整性(Waveform integrity)2、时序完整性(Timi...

2022-01-07 15:38:32 0

0 高速电路信号完整性分析与设计—信号完整性仿真

2022-02-10 17:29:52 0

0 定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同 引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

2022-11-16 14:56:00 1778

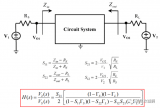

1778 由信号频率升高、上升时间减小所引起PCB互连线上的所有信号质量问题都属于信号完整性的研究范畴。本论文的主要研究可概括为传输线在PCB设计制造过程中所产生的信号完整性问题,具体分为三个方面

2023-03-27 10:40:30 0

0 经常在书上看到这个公式,信号带宽与上升沿的关系

2023-05-25 11:23:47 1481

1481

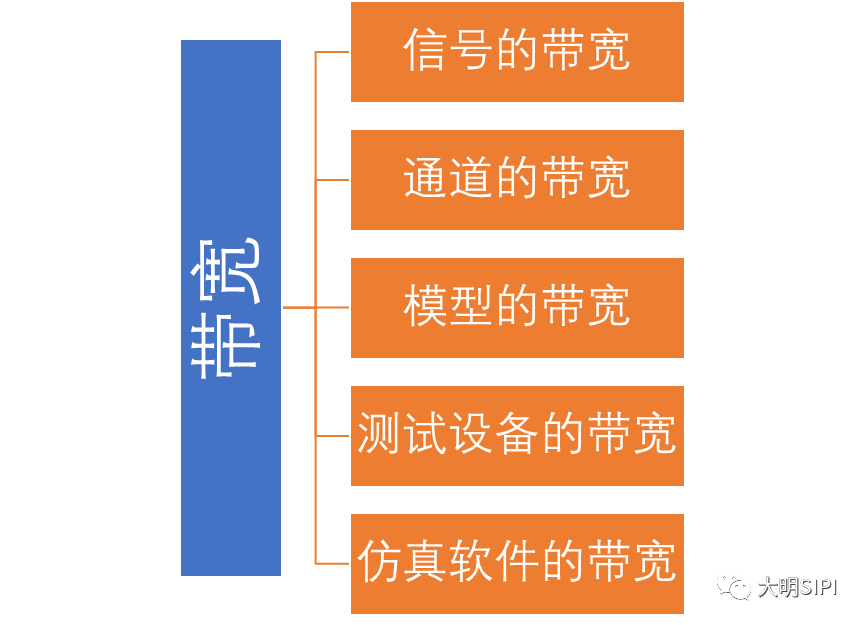

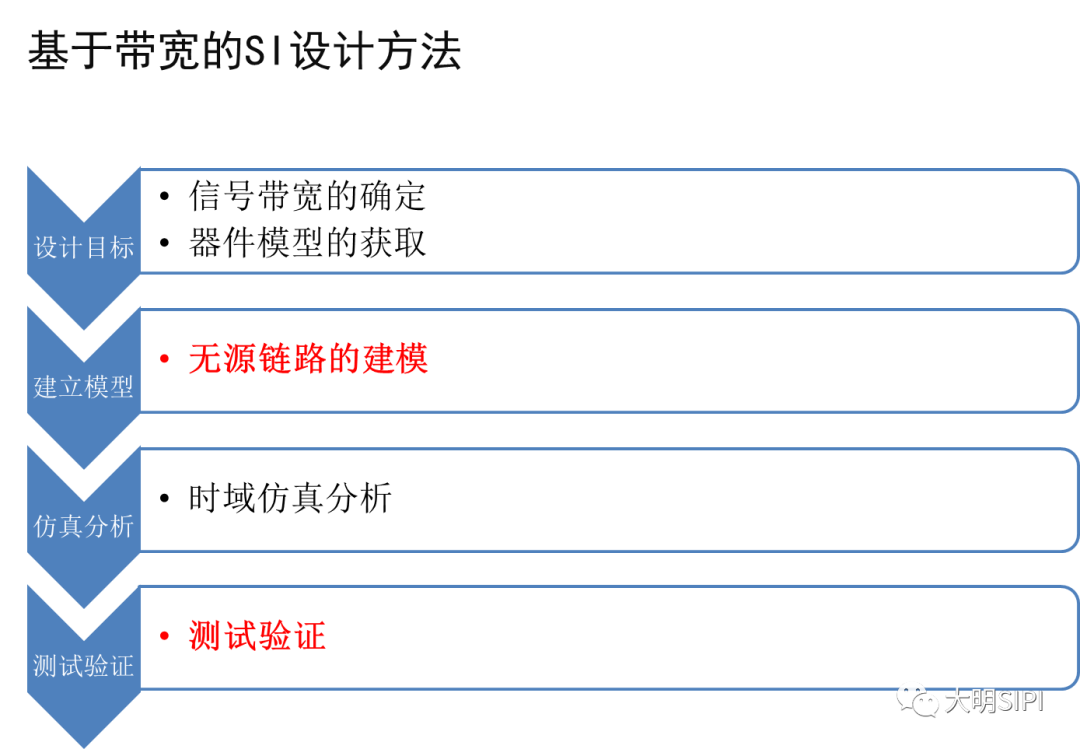

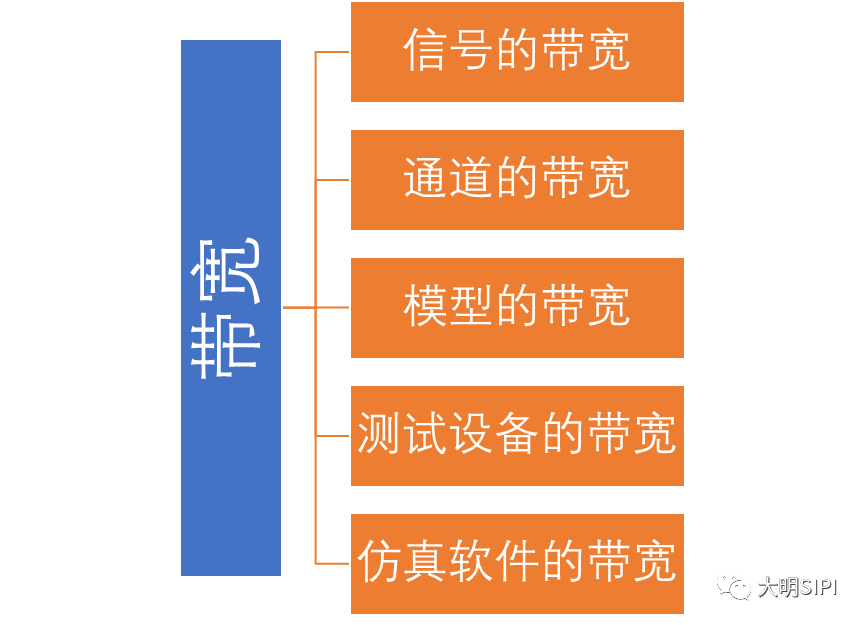

时域是真实存在的域,频域只是一个数学构造,但频域对我们分析解决信号完整性问题非常重要。那么如何将频域和时域建立联系方便的分析解决信号完整性问题?因此引出了时域和频域之间的纽带--带宽。对于信号完整性分析来说,带宽实在是太重要了,这里再唠叨唠叨。

2023-06-14 10:20:06 1045

1045

信号完整性分析的两个维度--时域和频域,而带宽是连接时域和频域的桥梁。同样,带宽也将信号的特性、传输通道、测试设备联系在一起,可见带宽是信号完整性分析中非常重要的一个概念。

2023-06-14 10:36:10 598

598

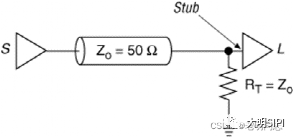

终端端接对于信号完整性有着重要的意义,它和源端匹配一样都是解决信号完整性问题的重要手段。

2023-06-15 11:08:03 892

892

随着速率的不断提高,信号能够在链路中传输的难度越来越大,信号质量会不断下降,我们把高速信号在传输中遇到各种问题统称为信号完整性问题。

2023-06-21 14:17:56 1021

1021

业界经常流行这么一句话:“有两种设计师,一种是已经遇到了信号完整性问题,另一种是即将遇到信号完整性问题”。固态硬盘作为一种高集成度的高时钟频率的硬件设备,信号完整性的重要性不言而喻。借着这句话本文主要跟大家聊下信号完整性的一些基本内容。

2023-06-27 10:43:26 1112

1112

用小的成本,快的时间使产品达到波形完整性、时序完整性、电源完整性的要求;我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,

2023-08-17 09:29:30 3111

3111

信号完整性是指在规定的时间内,信号从源端传输到接收端,信号不失真(能判断出信号的高低电平)。

2023-09-21 16:30:14 1278

1278

示波器和探头的上升时间与带宽之间具有怎样的量化关系? 示波器和探头是现代电子测量技术中不可或缺的两个部分。其中,示波器是一种测量电信号波形的仪器,而探头则是将电信号引入示波器中的装置。在电子测量

2023-10-22 12:43:33 536

536 信号频率和上升时间的关系 信号频率和上升时间是电子领域中两个常用的概念。它们之间的关系是比较密切的,一个信号的频率越高,它的上升时间就会越短。在本文中,我将会详细介绍信号频率和上升时间的相关知识

2023-11-06 11:01:07 1546

1546 信号传输并非严格针对网络设计师,您的PCB设计可能会遇到相同类型的问题。由于您无需费力地摆弄耳朵,因此防止电源完整性和信号完整性问题对于您的PCB设计流畅且无静电至关重要。

2023-11-08 17:25:01 344

344

导致信号失真、时序错误、带宽衰减等问题,从而影响整个系统的可靠性和性能。为了解决信号完整性问题,以下是一些必要的措施和方法。 首先,正确的信号完整性设计需要一个全面而准确的信号完整性分析。这包括对布线、噪声

2023-11-24 14:32:28 227

227

电子发烧友App

电子发烧友App

评论