可控阻抗是由PCB迹线及其相关参考平面形成的传输线的特性阻抗。当高频信号在PCB传输线上传播时,它是相关的。控制阻抗对于解决信号完整性问题,即无失真的信号传播。

2023-09-28 10:01:01 2107

2107

因素,并且将其降级到板上所剩的空间,那么这肯定无助于确保高效且可靠的电源设计。层的放置在多层 PCB板上,非常需要将 DC接地层或 DC输入或输出电压层放置在高电流功率组件层和敏感的小信号走线层之间

2020-09-24 12:21:18

传输过程中的质量且实现最佳的信号传输效果。 PCB上常用50Ω阻抗主要有以下6个原因: 1. 信号传输的一致性:50Ω阻抗可以匹配常用高速信号传输线材料的特性阻抗,并且可以保证信号在整个传输线上具有

2023-04-14 16:41:14

,不久以后,在象Hewlett-Packard这样在业界占统治地位的公司的影响下,欧洲人也被迫改变了,所以50欧姆最终成为业界的一个标准沿袭下来,也就变成约定俗成了,而和各种线缆连接的PCB,为了阻抗的匹配,最终也是按照50欧姆阻抗标准来要求了。

2019-06-04 07:51:57

请教:1. PCB板上 RS485 的 A B线 在 走线时 需要注意哪些 问题 ?2.PCB板上 RS485 的 A B线 需要做阻抗匹配吗 ?谢谢!

2016-10-25 14:29:05

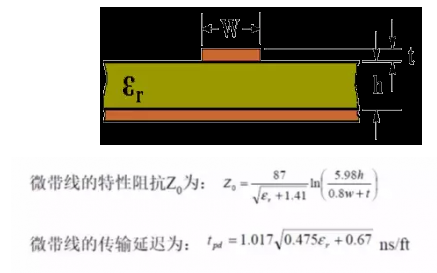

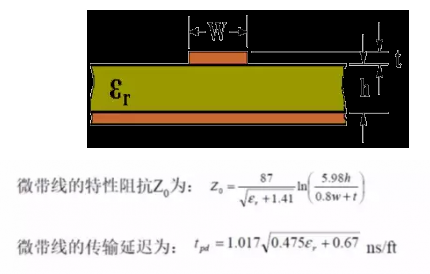

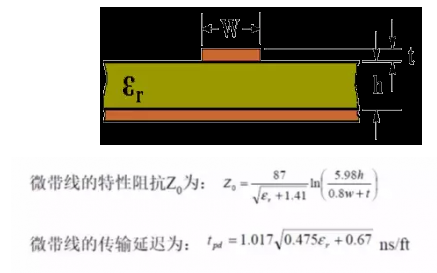

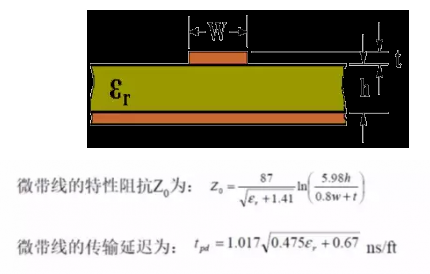

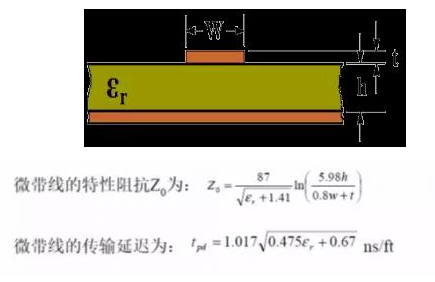

时一定要对板上走线的阻抗进行控制,才能尽可能避免信号的反射以及其他电磁干扰和信号完整性问题,保证PCB板的实际使用的稳定性。PCB板上微带线和带状线阻抗的计算方法可参照相应的经验公式。 五、印制电路板

2018-09-18 15:50:04

PCB板阻抗设计:阻抗线有无参考层阻抗如何变化?生产PCB时少转弯的阻抗线的阻抗更容易控制稳定性?

2023-04-10 17:03:31

抬高0.1mm就足以导致虚焊开路。 3、电路板的设计影响焊接质量 在布局上,电路板尺寸过大时,虽然焊接较容易控制,但印刷线条长,阻抗增大,抗噪声能力下降,成本增加;过小时,则散热下降,焊接不易控制

2019-05-08 01:06:52

PCB板对贴装压力控制的要求是什么对贴装精度及稳定性的要求芯片装配工艺对贴装设备的要求对照像机和影像处理技术的要求对板支撑及定位系统的要求

2021-04-25 06:35:35

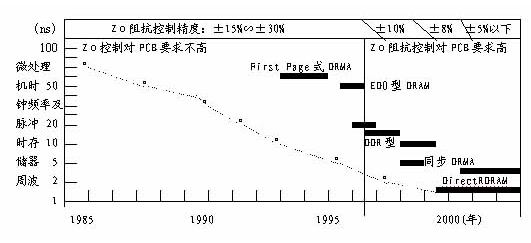

(Delay)等问题,严重时会传错信 号,死机。 3、缘由三 严格选择板材和控制生产流程,多层板上的Z0 才能符合 客户所要求的规格。元件的电子阻抗越高时,其传输速度才会越快,因而 PCB的Z0 也要随之

2018-09-14 16:21:15

本文具体分析了PCB板的特性阻抗和特性阻抗的控制办法。

2021-04-25 07:27:35

PCB阻抗控制 详情见附件

2017-11-26 14:13:37

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。印制电路板上导线的特性阻抗

2019-05-30 07:18:53

PCB阻抗控制打样要注意哪些问题?

2023-04-14 15:55:11

上比较难满足:过高的阻抗又需要较细的线宽及较厚的介质或较小的介电常数,不利于EMI及串扰的抑制,同时对于多层板及从量产的角度来讲加工的可靠性会比较差。控制50欧姆阻抗在使用常用板材(FR4等)、常用芯

2023-04-11 10:32:34

PCB做板阻抗要求计算

2015-03-02 16:46:50

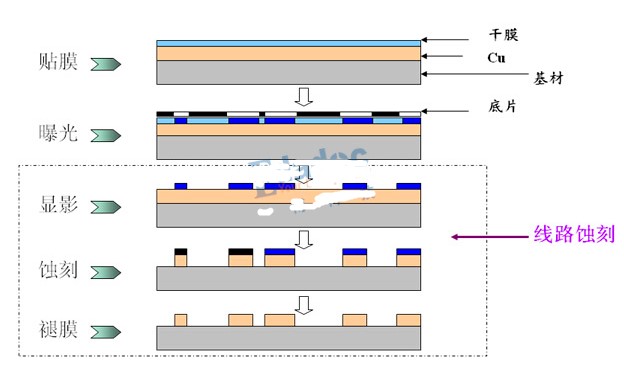

造成夹膜。(一般PCB厂所用干膜厚度1.4mil) ② 图形电镀线路铜厚加锡厚超过干膜厚度可能会造成夹膜。 三、PCB板夹膜原因分析 1.易夹膜板图片及照片 图三与图四,从实物板照片可看出线路较

2018-09-20 10:21:23

,这个阻抗也要控制在公差以内,否则,只有报废、返工。对于有阻抗控制要求的板,目前,PCB工厂比较常见的做法就是在PCB的生产拼版板边适当位置设计一些阻抗试样,这些阻抗试样具有与PCB相同的分层和阻抗线

2015-03-05 14:56:39

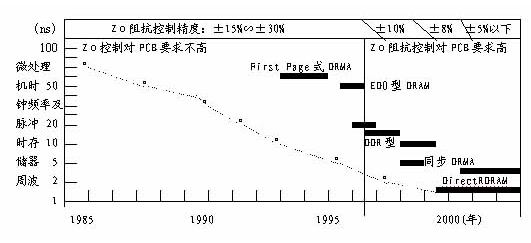

搭载RIA的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的 PCB 板件的特性阻抗控制精度不在局限于原来的±15%或士10%,有的阻抗控制精度要求提高到±8%甚至

2023-09-21 06:14:35

起着阻碍作用。在PCB加工中,阻抗处理是必不可少的。

1.PCB线路板要考虑接插安装电子元件,接插后考虑导电性能和信号传输性能等问题,所以就会要求阻抗越低越好

2.PCB线路板在生产过程中要经历沉铜

2023-06-01 14:53:32

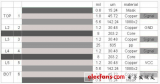

信号层直接相邻,以减少串扰。 主电源尽可能与其对应地相邻,构成平面电容,降低电源平面阻抗。 兼顾层压结构对称,利于制板生产时的翘曲控制。 以上为层叠设计的常规原则,在实际开展层叠设计时,PCB

2023-04-12 15:12:13

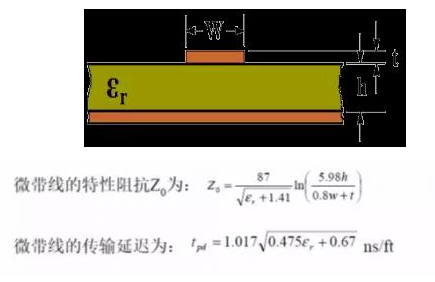

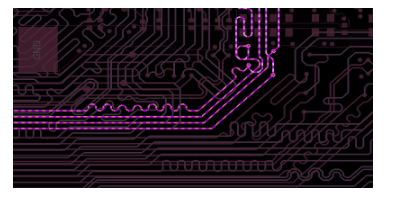

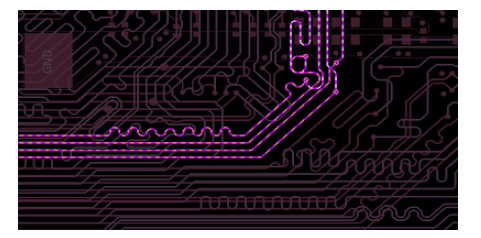

越小,同时藕合线长度尽量减短。 同一层上的信号线改变方向时应该避免直角拐弯,尽可能走斜线,且曲率半径大些的好。导线的分布应考虑均匀、美观。 2. 走线宽度和中心距 PCB板线条的宽度要求尽量一致

2012-10-23 10:39:25

会存在误差,误差就肯定会导致我们传输线的阻抗发生变化。因此PCB板厂经过这么多年的发展,无数次的走过这么一套PCB加工的流程,肯定会把阻抗的加工误差控制到一个合理的范围,目前常规的板厂也就是控制在10

2023-02-07 18:44:23

会存在误差,误差就肯定会导致我们传输线的阻抗发生变化。因此PCB板厂经过这么多年的发展,无数次的走过这么一套PCB加工的流程,肯定会把阻抗的加工误差控制到一个合理的范围,目前常规的板厂也就是控制在10

2023-02-13 14:38:37

的相对位置。特性阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。

由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层

2023-05-26 11:46:06

分享Agilent4294A阻抗分析仪维修案例: 一、仪器型号:Agilent4294A精密阻抗分析仪; 二、故障描述:开机自检报错;迹线不稳,不能测量; 三、检测过程: a)检查信号源,发现

2017-08-25 15:27:02

的标准,一些线缆和天线都是使用的75欧姆,此时就需要与之匹配的PCB线路阻抗。另外还有一些特殊的芯片通过改善芯片驱动能力,来降低传输线的阻抗,以此得到更好的抑制EMI和串扰的效果,如Intel的多数芯片要求阻抗控制在37欧姆、42欧姆甚至更低。

2019-05-30 08:13:09

线缆连接的PCB,为了阻抗的匹配,最终也是按照50欧姆阻抗标准来要求了。其次,从线路板制作可实现的角度出发,50欧姆实现起来比较方便。从前面阻抗计算公式可知,过低的阻抗需要较宽的线宽以及薄介质(或较大

2019-08-07 09:59:20

为什么说控制阻抗在对PCB线路板如此重要?

2023-04-14 15:09:13

越小其特性阻抗越低(差分阻抗与差份线队之间的间距成反比)。差分传输线特性阻抗通常情况下为100Ω,有时也用到75Ω。考虑到多层PCB板生产时PCB迹线可分布于表面或者内层,这两种情况下PCB迹线

2009-09-28 14:48:47

pcb线路板阻抗是指电阻和对电抗的参数,对交流电所起着阻碍作用。在pcb线路板生产中,阻抗处理是必不可少的。原因如下: 1、PCB线路(板底)要考虑接插安装电子元件,接插后考虑导电性能和信号传输

2023-06-26 15:38:22

在能量上的传输。3、特性阻抗控制(Z0 )上述此种“讯号”传输时所受到的阻力,另称为“特性阻 抗”,代表符号为Z0。所以,PCB导线上单解决“通”、“断”和“短路”的问题还 不够,还要控制

2015-04-10 20:52:45

PCB板上的布局、高速信号的布线等因素,都会引起信号完整性问题,导致系统工作不稳定,甚至完全不工作。 如何在PCB板的设计过程中充分考虑到信号完整性的因素,并采取有效的控制措施,已经成为当今PCB

2018-08-29 16:28:48

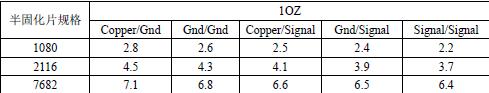

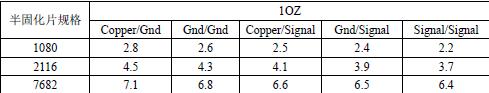

左右)。正由于PP的半固态特性,制作完成的各PCB中的PP厚度也会有所偏差,因此,阻抗控制的一致性也可能存在偏差。配合使用Core和PP以实现多层PCB的设计制作。2.铜箔铜箔厚度经常以盎司(oz)为

2022-11-15 16:38:29

双层pcb板在设计USB差分90欧姆的阻抗时为何选择共面阻抗模式计算?具体什么时共面阻抗?

2019-09-10 04:37:34

如何让PCB板上的阻抗越小?是线路越宽线的路径越短阻抗越小吗?

2023-04-12 15:30:12

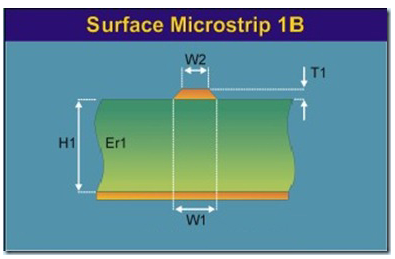

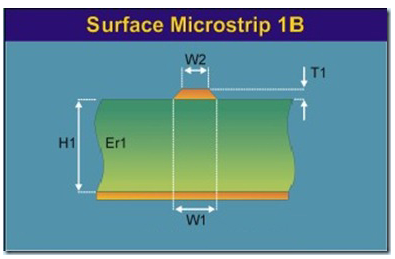

实现阻抗控制的传输线配置方式控制阻抗 PCB 通常使用微波传输带或带状线传输线路,以单端(未平衡)或差分(已平衡)配置的方式生产。单端配置以下为几种常见单端微波传输带和带状线传输带的配置:注意以下各

2009-09-28 16:16:56

/接口电路PCB打板:软件算法:通信协议:硬件和软件可靠性分析:工业控制板开发的原因替代PLC 不可能完成的任务,突破某个功能在速度或是数量上的限制,特殊的功能要求或是须要降低成本。博主在工控板方面积累了相当的经验,现在就为新手们铺下路吧。PCB画板软件:AD ( Altium Designer )硬件

2021-08-23 06:51:29

关于 PCB 板的变形,可以从设计、材料、生产过程等几方面来进行分析,这里简单地阐述下,供大家参考。 设计方面:(1)涨缩系数匹配性一般电路板上都会设计有大面积的铜箔来当作接地之用,有时候 Vcc

2022-06-01 16:07:45

,增大线厚可减小阻抗;线厚可通过图形电镀或选用相应厚度的基材铜箔来控制。对铜厚的控制要求均匀,对细线、孤立的线的板加上分流块,其平衡电流,防止线上的铜厚不均,影响阻抗对cs与ss面铜分布极不均的情况,要对

2020-09-07 17:54:12

影响印刷电路板PCB的特性阻抗因素及对策摘要:本文给出了印刷电路板PCB特性阻抗的定义,分析了影响特性阻抗的因素及的构造,参数对特性阻抗精度的影响最后给出了一些对策。关键词:印刷电路板, 特性阻抗,精度

2009-05-16 21:42:20

制作的线路板的铜线),相对某一参考层(也就是常说的屏蔽层、影射层或参考层),其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它实际上是电阻抗、电感抗、电容抗等一个矢量总和。2、控制PCB

2016-10-10 14:38:27

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗

2020-09-07 17:52:55

pcb板阻抗与导线长度有关吗?在对FR的天线进行阻抗计算时,对天线的长度有要求吗?我举个例子哦。比如说做读卡器的天线:在板上我们画了一圈一圈的导线做板载天线。这个我们要画多少圈最合适?我知道天线

2019-01-30 03:51:45

/4mil,我们输出的要求是DDR部分阻抗控制50+/- 10%,切换PCB厂家时经常会遇到厂家无法满足我们的阻抗控制要求,而需要反复确认,请帮忙明确下该芯片对DDR走线的阻抗控制的具体要求?以及影响?对应的影响又如何测试,详细的问题请见附件

2018-06-22 01:59:57

应该是另作它用,与PCB制板时的阻抗控制是两回事。因此在设计PCB时,依然要控制阻抗,就像DDR的时钟那样。这么理解对吗?

2017-11-20 10:21:31

1、pcb时钟频率超过5MHZ或信号上升时间小于5ns,一般需要使用多层板设计。原因:采用多层板设计信号回路面积能够得到很好的控制。2、对于多层板,关键布线层(时钟线、总线、接口信号线、射频线、复位

2014-12-25 10:19:32

在高速pcb设计中,经常听到要求阻抗匹配。而设计中导致阻抗不匹配的原因有哪些呢?一般又对应着怎么的解决方案?欢迎大家来讨论

2014-10-24 13:50:36

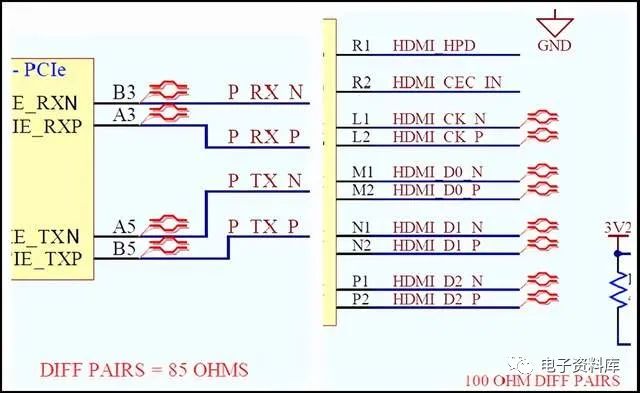

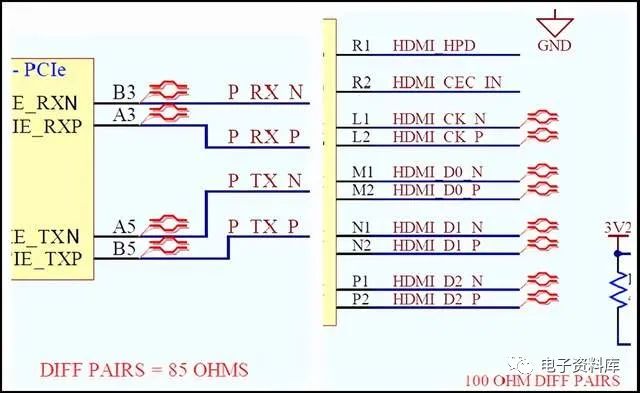

HDMI 规范文件里面规定其差分线阻抗要求控制在 100Ω ±15%,其中 Rev.1.3a 里面规定相对放宽了一些,容忍阻抗失控在100Ω ±25%范围内,不要超过 250ps。 通常,在

2019-05-17 10:40:14

的相对位置。特性阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。

由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层

2023-05-26 11:30:36

越来越多的厂商要求指定PCB板上的DC迹线阻抗。以下从设计商的角度道出了指定和

2006-04-16 20:23:26 607

607 PCB迹线的阻抗控制简介

PCB上的阻抗控制电信和计算机设备操作的速度和切换速率正在不断增长。尽管在低频情况下,这是一个可以

2009-09-28 14:42:44 1258

1258 传输线阻抗计算中的有关问题

结合目前我公司PCB板加工厂家的工艺能力,在用polar公司阻抗计算器CITS25计算PCB板上迹线特性阻抗时,

2009-09-28 14:54:20 2005

2005

Cadence PCB SI分析特性阻抗变化因素教程

Cadence 的PCB SI工具是一个强大的SI分析软件,下面我们将采用SI这个软件对对阻抗参数进行分析!

1、概

2010-03-21 18:37:49 3316

3316

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,我对这个问题有了一些粗浅的认识,愿和大家分享。

2011-05-06 11:28:46 4254

4254

随着PCB 信号切换速度不断增长,当今的PCB 设计厂商需要理解和控制PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

2016-03-24 14:48:57 0

0 PCB阻抗设计方面的干货。

2017-01-13 17:13:49 0

0 时,若导线的长度接近信号波长的1/7, 此时的导线便成为信号传输线,一般信号传输线均需做阻抗控制。PCB制作时,依客户要求决定是否需管控阻抗,若客户要求某一线宽需做阻抗控制,生产时则需管控该线宽的阻抗。

2017-07-27 11:20:07 0

0 随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线

2017-11-26 14:28:01 1036

1036 PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2018-10-14 09:28:00 1441

1441 基于多层板介质层厚度对阻抗的影响,了解其均匀性分布及掌握其控制方法对阻抗产品阻抗控制至关重要。本文从PCB层压介质层设计及层压工艺相关控制点着手探究介质厚度均匀性的控制方法,指出提升介质厚度匹准度以满足阻抗设计要求的有效途径。

2018-11-03 10:13:40 3948

3948 PCB迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB阻抗的范围是 25 至120 欧姆。

2019-08-08 15:23:43 3818

3818

。不仅搭载RIMM的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的PCB板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对PCB制造厂来说确实是很大的挑战。

2019-05-21 14:47:01 818

818

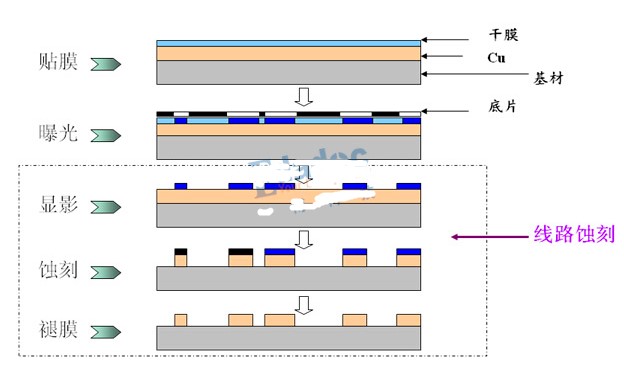

为什么常规阻抗控制只能是10%的偏差,那一定要了解加工步骤,其中包括层压、蚀刻及PCB覆铜板材公差及PCB阻焊工序的制作。

2019-04-19 15:48:04 5655

5655

阻抗控制线是否会增加PCB板的成本?是的,会增加PCB的制造成本设计。但是,有3个主要元素可以控制PCB制造成本。

2019-07-31 11:09:56 2860

2860 、PCB供应商反馈信息等,而最终得出此推荐设计。适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

2019-08-01 17:45:55 0

0 随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。

2019-08-30 08:45:40 3032

3032 阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-09-06 11:52:29 12487

12487

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17:00 10393

10393

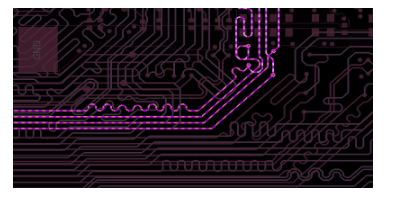

常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-12-31 15:42:08 2238

2238

PCB设计为何一般控制50欧姆阻抗?

2020-01-15 16:17:41 9751

9751 设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2020-07-14 10:25:00 6

6 对于模拟或高频数字电路,确保在PCB板上传播的信号的完整性至关重要。实际上,高于100 MHz的信号会受到导体走线的 阻抗 的影响,如果不加以适当考虑,则会导致不便的错误,并且特别难以分析。幸运

2020-09-03 19:04:58 6541

6541 还可以确保沿着互连的一致的传播延迟,从而允许并行高速 PCB 信号(例如 PCIe 中的信号)的长度精确匹配以防止歪斜。 由于阻抗控制的布线需要精确制造 PCB 互连件,因此制造商已花费大量精力完善蚀刻工艺,以确保迹线几何形状与 PCB 设计软件中使用

2020-09-25 18:59:16 1531

1531 迹线阻抗控制是正确确定迹线大小的简单问题。当单独考虑一条走线时,其阻抗将具有明确定义的值。但是,当靠近另一个走线或导体时,由于意外耦合,走线的阻抗将不同于其设计值。这种令人讨厌的事实会导致沿互连

2021-02-17 05:32:00 3111

3111

迹线阻抗控制是正确确定迹线大小的简单问题。当单独考虑一条走线时,其阻抗将具有明确定义的值。但是,当靠近另一个走线或导体时,由于意外耦合,走线的阻抗将不同于其设计值。这种令人讨厌的事实会导致沿互连

2021-02-13 07:06:00 1199

1199

在 PCB 设计阶段要注意阻抗控制,这一点很重要。阻抗控制涉及为 PCB 上的走线和传输线指定所需的阻抗。这对于高速信号尤其重要,并且可能会受到您的影响。基材,铜线宽度和布线。即使在布置好电路板

2020-10-09 21:12:57 1297

1297 更高速的动作。不仅搭载 RIMM 的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的 PCB 板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对 PCB 制造厂来说确实是很大的挑战。本文主要针对如何满足客户

2023-02-03 14:02:05 794

794 在PCB制造中,迹线代表导体,层压板代表绝缘体,平面代表屏蔽。因此,印刷电路板的阻抗取决于制造过程中使用的尺寸和材料。

2021-02-27 10:26:01 2180

2180 最近设计了一块四层板pcb,因为是高速电路,有阻抗匹配的要求,所以在发给pcb板厂打样时,特定指定了哪些线要做

2020-12-07 12:08:23 18299

18299 在 STM32 无线系列产品的 PCB 设计中,需要对射频部分电路进行阻抗控制,良好的阻抗控制可以减少信号衰减、反射和 EMC 辐射。本篇 LAT 主要介绍印制电路板(PCB)上射频走线阻抗仿真计算

2022-06-16 16:36:21 5063

5063 单面PCB,没有地平面,采用双侧都有地线的共面波导结构,就能实现布线阻抗控制:

2022-08-12 14:58:43 1347

1347 决于选择的PCB叠层结构。 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 PCB叠层设计 “ 层的定义设计原则 1、主芯片相临层

2023-07-19 07:45:02 543

543 阻抗控制pcb

2023-09-18 10:40:37 596

596 从理论到实践之pcb阻抗控制表的使用

2023-09-26 10:34:15 324

324 造成pcb板开裂原因分析

2023-11-16 11:01:24 937

937 pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷电路板)设计和制造过程中,通过优化电气特性和信号完整性,确保设计满足特定的阻抗要求。在高速数字和模拟电路中,阻抗控制

2024-01-17 16:38:04 722

722 pcb开路分析,这6个原因要注意

2024-02-21 16:43:39 181

181 一站式PCBA智造厂家今天为大家讲讲如何解决pcb设计阻抗不连续的问题?解决PCB设计中的阻抗不连续的方法。当涉及到PCB(Printed Circuit Board)设计时,阻抗一直是一个非常重要

2024-03-21 09:32:59 89

89

电子发烧友App

电子发烧友App

评论