布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中

2015-01-12 14:53:57

、高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7、有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2018-09-13 15:50:25

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中

2019-06-10 10:11:23

效的减少相互间的耦合。6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2014-08-13 15:44:05

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-05-23 08:52:37

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2017-07-07 11:45:56

怎么把走线加长呢?绕呗!Bingo! 终于绕回主题了,真不容易。这就是蛇形线在高速系统中的主要作用。绕线,等长。就是这么简单。蛇形线就是用来绕等长的,通过画蛇形线,我们能让同组信号实现等长,这样在接收

2023-04-13 16:19:17

是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。 高速数字PCB板的等

2013-08-29 15:43:30

倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

2017-11-22 20:04:14

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2020-07-14 18:02:17

走线的线距>=2倍的线宽。PCI板上的蛇?线就是为?适应PCI 33MHzClock的线长要求。?在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

2018-09-20 11:05:23

现在做数字电路方面的工作,每个板子上都有很多路的时钟信号,而且时钟信号线贯穿整条pcb,造成辐射超标,我想大家给我些PCB设计上的建议。希望大家畅所欲言,不吝赐教。

2014-11-07 09:45:42

PCB设计中跨分割的处理高速信号布线技巧

2021-02-19 06:27:15

请问大伙PCB设计中,常见的串口通讯线(TX、RX)是否属于高速信号线?然后高速信号的标准到底是什么?在网上浏览了一些相关知识,感觉始终不太理解。

2023-01-26 20:39:13

效的减少相互间的耦合。 6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2014-12-09 16:45:27

中铺铜的作用(ZT)

直角走线为什么不可取?差分走线的优势是啥?蛇形走线如何走?——PCB设计走线的几点专家建议(ZT)

……

BTW,这些分享不过瘾,希望听到你的分享,哪怕吐槽也行!来吧,吐

2018-08-13 08:14:18

考虑很多参数的影响,在高频信号下,很多普通电路可以忽略的参数不能忽略,因此可能要考虑到传输线效应 。30[问]高速PCB,布线过程中过孔的避让如何处理,有什么好的建议?答高速PCB,最好少打过孔,通过

2018-04-09 10:57:20

可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。 主要从直角走线,差分走线,蛇形线等三个方面来阐述。 1. 直角走线 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量

2018-09-17 17:31:52

的分区设计PCB设计技巧Tips11:蛇形走线有什么作用?PCB设计技巧Tips12:确保信号完整性的电路板设计准则PCB设计技巧Tips13:印制电路板的可靠性设计PCB设计技巧Tips14:磁场

2014-11-26 15:19:20

就是为了适应PCI 33MHzClock的线长要求 关于蛇形走线,因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,若在一般普通PCB板中

2014-11-19 11:54:01

的分区设计PCB设计技巧Tips11:蛇形走线有什么作用?PCB设计技巧Tips12:确保信号完整性的电路板设计准则PCB设计技巧Tips13:印制电路板的可靠性设计PCB设计技巧Tips14:磁场屏蔽

2014-11-19 15:43:00

PCB设计者必看,18种特殊走线的画法与技巧01PCB设计者必看,AD布蛇形线方法Tool里选Interactive length tuning要先布好线再改成蛇形,这里用的是布线时直接走蛇形:先

2020-06-24 08:03:05

。 5、可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。 6、高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7、有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2018-12-05 09:36:02

;=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等

2019-05-22 02:48:05

33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC 滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

2010-10-28 00:05:05

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2018-11-23 17:02:19

要求蛇形线间距最少是线宽的两倍。信号的上升时间越小,就越易受分布电容和分布电感的影响。四、分布参数LC滤波器蛇形走线在某些特殊的电路中起到一个分布参数的LC滤波器的作用。总结: PCB蛇形运用是根据场景变化的,欢迎补充,谢谢!

2023-03-22 10:33:44

我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间? 一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定。下图为信号

2015-05-05 09:30:27

高速PCB设计中常规PCB布线,有以下基本要求:(1)QFP、SOP等封装的矩形焊盘出线,应从PIN中心引出(一般采用铺shape)(2)布线到板边的距离不小于20MIL。(3)金属外壳器件下

2017-02-16 15:06:01

` 本帖最后由 飞翔的乌龟005 于 2017-2-10 10:43 编辑

高速PCB设计中常规PCB布线,有以下基本要求:(1)QFP、SOP等封装的矩形焊盘出线,应从PIN中心引出(一般采用

2017-02-10 10:42:11

高速PCB设计中的若干误区与对策

2012-08-20 14:38:56

阻抗匹配阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速PCB设计中,阻抗的匹配与否关系到信号的质量优劣。

2019-05-31 08:12:33

高速PCB设计之一 何为高速PCB设计电子产品的高速化、高密化,给PCB设计工程师带来新的挑战。PCB设计不再是产品硬件开发的附属,而成为产品硬件开发中“前端IC,后端PCB,SE集成”3个环节中

2014-10-21 09:41:25

电路应具备信号分析、传输线、模拟电路的知识。错误的概念:8kHz帧信号为低速信号。 问:在高速PCB设计中,经常需要用到自动布线功能,请问如何能卓有成效地实现自动布线? 答:在高速电路板中,不能只是看

2019-01-11 10:55:05

高速PCB设计指南之五第一篇 DSP系统的降噪技术 随着高速DSP(数字信号处理器)和外设的出现

2009-03-25 08:56:30

本帖最后由 eehome 于 2013-1-5 09:53 编辑

高速PCB设计已成为数字系统设计中的主流技术,PCB的设计质量直接关系到系统性能的好坏乃至系统功能的实现。针对高速PCB

2012-03-31 14:29:39

`请问高速PCB设计规则有哪些?`

2020-02-25 16:07:38

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地

2016-01-19 22:50:31

。 而绝对的要求是控制两个器件之间的走线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由高速电路设计者提出,而由PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要

2018-11-27 15:22:54

在高速pcb设计中,经常听到要求阻抗匹配。而设计中导致阻抗不匹配的原因有哪些呢?一般又对应着怎么的解决方案?欢迎大家来讨论

2014-10-24 13:50:36

、PCB的可靠性设计4、电磁兼容性和PCB设计约束三、1、改进电路设计规程提高可测性2、混合信号PCB的分区设计3、蛇形走线的作用4、确保信号完整性的电路板设计准则四、1、印制电路板的可靠性设计五、1

2012-07-13 16:18:40

蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如

2019-03-22 06:20:09

高速中的蛇形走线,适合在那种情况?有什么缺点没,比如对于差分走线,又要求两组信号是正交的。回答:”蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感

2019-05-09 07:35:35

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟

2019-05-21 07:14:41

,选中Options对话框中的Routing页表项,其中红色框中的参数即针对蛇形线,这里我们把平行线段距离(Gap)设置为3,点击OK,即可完成蛇形线的设置。(6)在PCB中选定一个引脚,按F3开始走线

2015-01-12 15:40:09

Blazerouter怎么布蛇形线及如何走蛇形线Powerpcb本身布不了蛇形线,要用pads带的Blazeroutel来布.Blazeroute是PADS专用的布线工具.用Blazeroute打开pcb,如图

2008-07-18 17:55:40

、高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。2...

2021-12-31 06:22:08

(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中是至关重要

2009-05-31 10:08:49

;/p><p style="TEXT-INDENT: 2em">6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能

2009-05-31 10:43:01

,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。

2009-08-20 20:58:49

是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。01直角走线直角走线一般是PCB布线中要求尽量避免

2018-07-08 13:28:36

差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢

2018-09-21 11:53:08

一线工程师整理的PCB设计技巧,包含高速,混合信号和低电平应用,例举众多实例说明。工程师们绝对福利~PCB设计是一门艺术,好的PCB设计需要花费数十年的时间才能不断磨砺而成。设计一个可靠的高速,混合

2017-07-26 17:37:44

周期!原来PCB的影响这么大,我们板子上超过1inch的走线是很常见的。 那么延迟会对板子正常工作有影响么?看看实际系统,如果只是一个信号,和其他信号不想关,那么延迟似乎不会有什么影响。但是,在高速

2014-12-25 10:45:24

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2016-12-07 22:20:49

线,尤其不能在小范围内蜿蜒走线。5.可以经常采用任意角度的蛇形走线,如图1-8-20中的C结构,能有效的减少相互间的耦合。6.高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量

2019-03-18 21:38:12

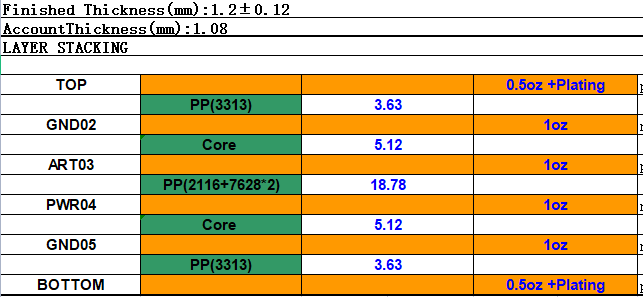

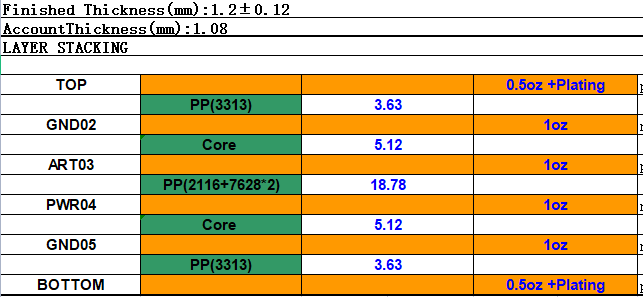

PCB设计中层叠结构的设计建议:1、PCB叠层方式推荐为Foil叠法2、尽可能减少PP片和CORE型号及种类在同一层叠中的使用(每层介质不超过3张PP叠层)3、两层之间PP介质厚度不要超过21MIL

2017-01-16 11:40:35

高速PCB设计中常规PCB布线,有以下基本要求:(1)QFP、SOP等封装的矩形焊盘出线,应从PIN中心引出(一般采用铺shape)(2)布线到板边的距离不小于20MIL。(3)金属外壳器件下

2017-01-23 16:04:35

高速PCB设计中常规PCB布线,有以下基本要求:(1)QFP、SOP等封装的矩形焊盘出线,应从PIN中心引出(一般采用铺shape)(2)布线到板边的距离不小于20MIL。(3)金属外壳器件下

2017-01-23 09:36:13

本期讲解的是PCB设计中处理关键信号的注意事项。一、关键信号的识别关键信号通常包括以下信号:时钟信号(*CLK*),复位信号(*rest*,*rst*), JTAG信号(*TCK*)二、处理关键信号

2017-11-01 17:06:26

通用的高速信号PCB设计处理原则有:(1)层面的选择:处理高速信号优先选择两边是GND的层面处理(2)处理时要优先考虑高速信号的总长(3)高速信号Via数量的限制:高速信号允许换一次层,换层时加

2017-02-07 09:40:04

在高速PCB设计中,过孔有哪些注意事项?

2021-04-25 09:55:24

图解在高速的PCB设计中的走线规则

2021-03-17 07:53:30

在高速PCB设计过程中,由于存在传输线效应,会导致一些一些信号完整性的问题,如何应对呢?

2021-03-02 06:08:38

解决高速PCB设计信号问题的全新方法

2021-04-25 07:56:35

。 6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以 只作时序匹配之用而无其它目的。 7. 有时可以考虑螺旋走线的方式进行绕线。

2014-12-16 09:47:09

在一般的非高速PCB设计中,我们都是认为电信号在导线上的传播是不需要时间的,就是一根理想的导线,这种情况在低速的情况下是成立的,但是在高速的情况下,我们就不能简单的认为其是一根理想的导线了,电信号

2019-05-30 06:59:24

,能有效的减少相互间的耦合。6. 高速PCB 设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7.有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2015-03-05 15:53:35

,尤其不能在小范围内蜿蜒走线。 5、可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。6、高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7、有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2013-11-13 21:42:25

规则一:高速信号走线屏蔽规则 在高速的设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。 图1

2018-09-20 10:38:01

的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。规则二:高速信号的走线闭环规则由于PCB板的密度越来越高

2017-11-02 12:11:12

什么是高速pcb设计高速线总体规则是什么?

2019-06-13 02:32:06

内蜿蜒走线。5. 可以经常采用任意角度的蛇形走线,如图1-8-20中的C结构,能有效的减少相互间的耦合。6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配

2012-12-18 12:12:55

高速PCB设计的叠层问题

2009-05-16 20:06:45 0

0 高速PCB设计指南之七

第一篇 PCB基本概念

1、“层(Layer) ”的概念 与字处理或其它许多

2009-11-11 15:07:15 433

433 高速PCB抄板与PCB设计方案

目前高速PCB的设计在通信、计算机、图形图像处理等领域应用广泛。而在这些领域工程师们用的高速PCB

2009-11-18 14:11:47 824

824 基于Cadence的高速PCB设计

随着人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快.相应的高速PCB的应用也越来越广,设计也越来越

2009-12-12 17:50:27 954

954 高速PCB设计指南............................

2016-05-09 15:22:31 0

0 高速PCB设计电容的应用

2017-01-28 21:32:49 0

0 信号上升时间时,产生的串扰将达到饱和。 3.带状线(Strip-Line)或者埋式微带线(Embedded Micro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。 4.高速以及对时序要求较为严格的信号线,尽

2017-12-01 10:51:57 0

0 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

2018-04-14 11:06:00 3225

3225

布线(Layout)是 PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB设计

2018-07-06 15:28:18 5349

5349 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05:42 4494

4494

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计

2019-07-01 15:24:50 5303

5303 高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。

2020-01-22 12:18:00 1377

1377 如上图所示:在PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2

2020-06-05 10:54:04 2839

2839 蛇形走线是PCB设计中会遇到的一种比较特殊的走线形式(如下图所示),很多人不理解蛇形走线的意义,下面对蛇形走线的作用进行简单介绍。

2023-03-30 18:14:23 3564

3564 高速PCB设计当中铺铜处理方法

2023-11-24 18:03:58 263

263

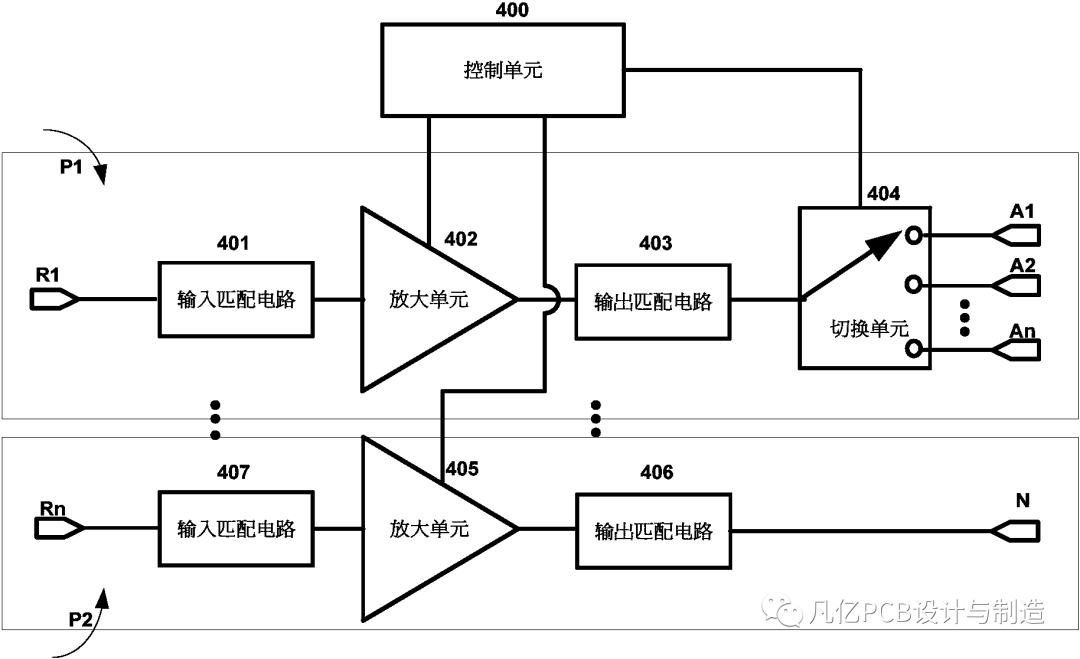

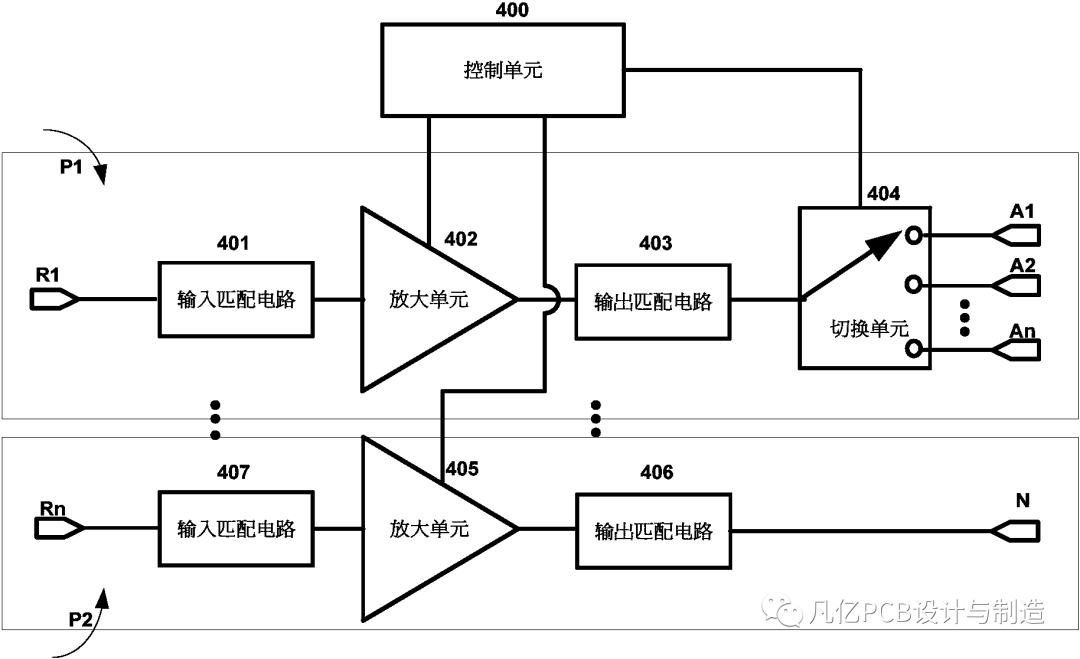

射频(Radio Frequency,RF)电路在现代电子领域中扮演着至关重要的角色,涵盖了广泛的应用,从通信系统到雷达和射频识别(RFID)等。在高速PCB设计中,射频电路的分析和处理是一项具有

2023-11-30 07:45:01 317

317

电子发烧友App

电子发烧友App

评论