内存广泛应用于各类电子产品中,内存测试也是产品测试中的热点和难点。内存测试中最为关键的测试项目为DQ/DQS/CLK之间的时序关系。##Jitter Sim是力科示波器中的一个通过软件仿真的方法实现信号源的功能,该功能可以实现时钟信号,正弦信号,NRZ,RZ等种类多样的码型。

2014-01-06 14:31:02 2776

2776

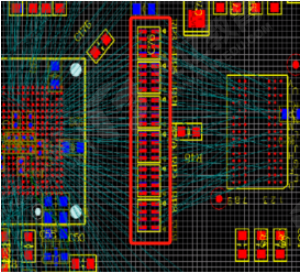

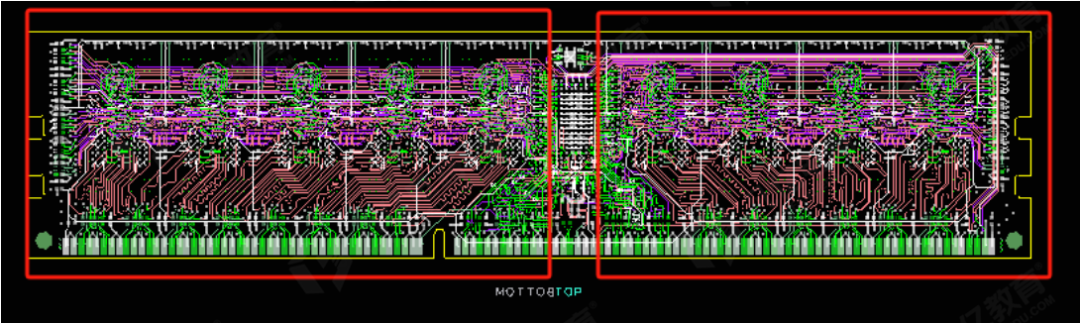

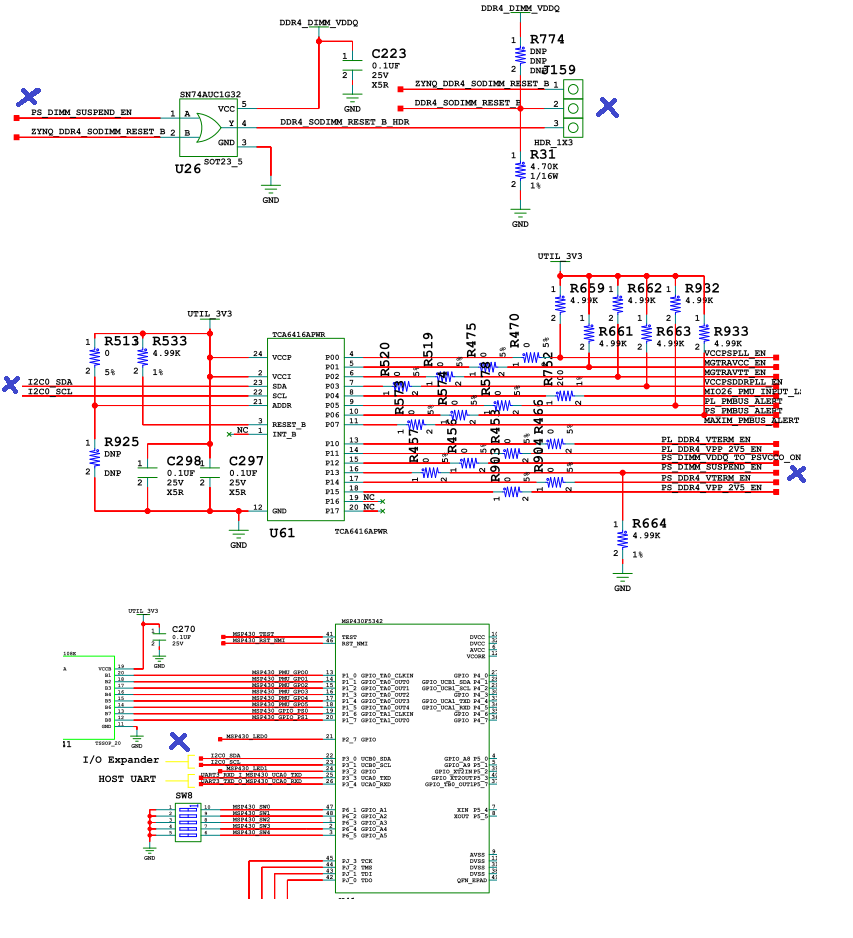

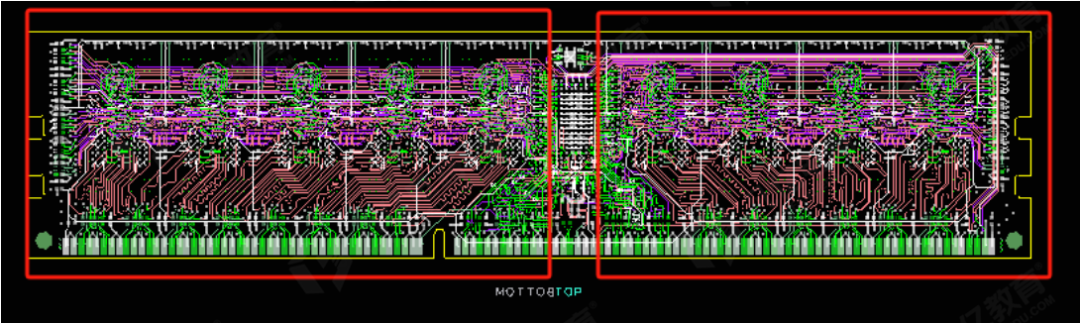

本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB设计。

2014-07-24 11:11:21 4410

4410

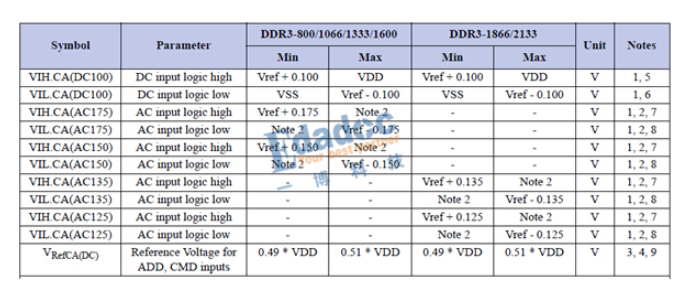

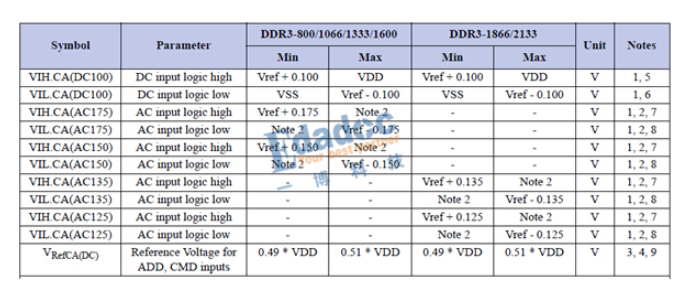

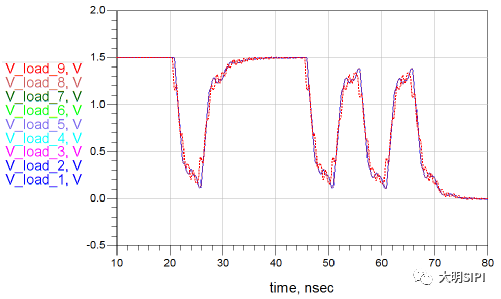

导读:DDR5协议发布已经有一段时间了,其中的变化还是比较大的,地址信号采取了ODT的端接形式,本篇文章为大家仿真一下DDR5地址信号。同时,我也推荐大家关注我在仿真秀原创的精品课《DDR3/4/5系列信号完整性仿真24讲》,让你清楚掌握DDR协议和仿真关键技术要点。

2022-12-01 10:24:03 933

933 信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 889

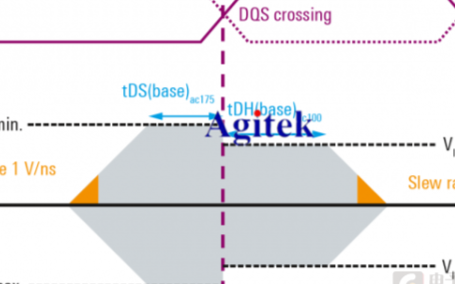

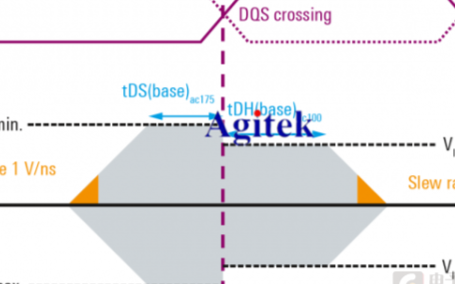

889 DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 464

464

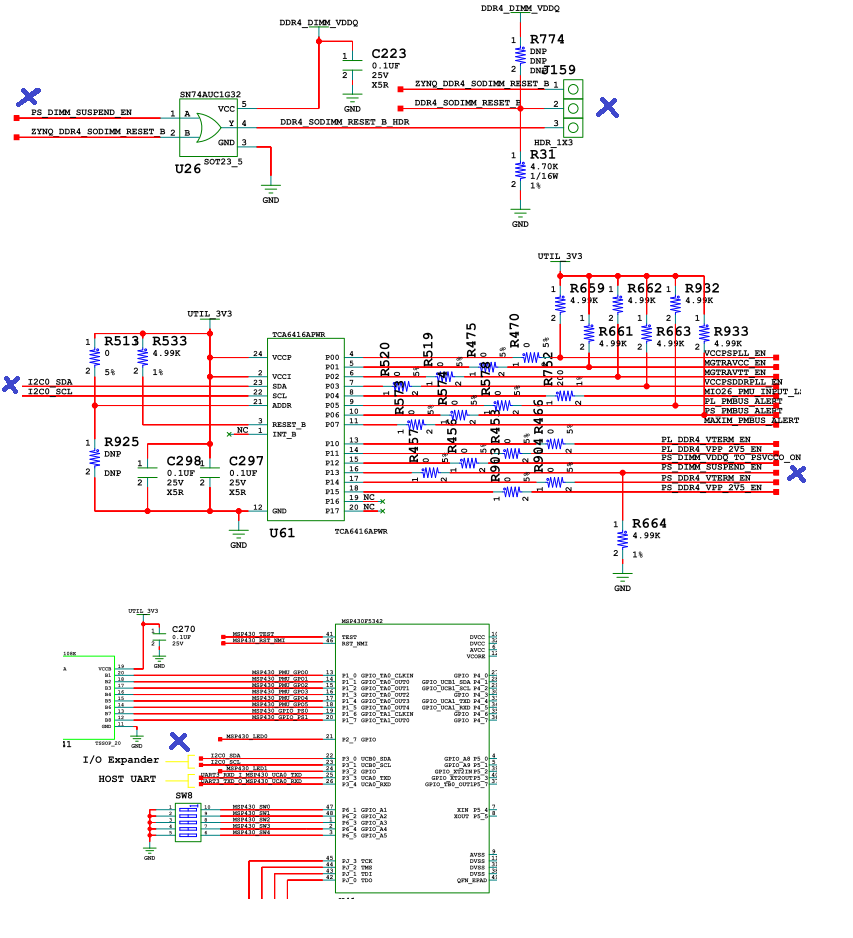

】设置仿真库;【2】设置信号和电源的归类,电源要赋予电压;【3】设置层叠;【4】设置三种原件模型;【5】设置XNET网络;【6】设置差分对;【7】检查仿真的网络相关设置是否正确。4、IBIS模型到

2020-07-06 16:09:27

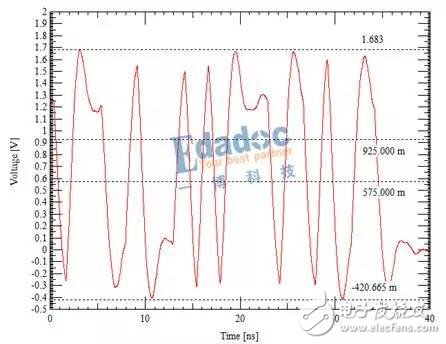

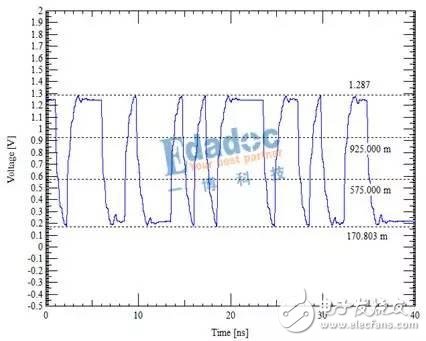

孤立铜的存在。 5 PCB板后仿验证 DDR3的PCB设计结束后进行后仿分析,用以对前面的仿真分析进行验证。PCB板后仿主要是对DDR3信号质量和时序关系进行分析。 5.1 DDR3的差分时钟验证

2014-12-15 14:17:46

作者:黄刚DDR仿真作为一个非常普遍的仿真模块,基本上入门SI行业的人都会首先接触到。记得本人刚接触这个行业的时候,也是先接触DDR模块的仿真。从DDR2到DDR4,可能很多同行都一直使用同一

2019-07-24 06:56:33

DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号

2018-09-20 10:29:55

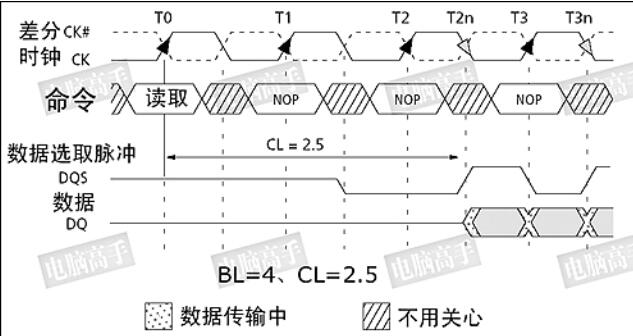

上篇文章我们用仿真实例向大家展示了DDR中地址相对于时钟的建立时间与保持时间。那么数据信号相对于DQS又是什么样的关系呢?我们知道,DDR和普通的SDRAM相比起来,读取速率为普通SDRAM的两倍

2016-11-08 16:59:51

时间的时序裕量不足,我们知道,时序裕量问题的确也是可以通过降频来弥补的,因此我们对仿真的精度有了更大的信心!好!最后再试一种组合,一定要成功!就是地址控制信号和CLK时钟都选用MEDIUM模式,我们先来

2023-02-02 13:45:09

本帖最后由 一只耳朵怪 于 2018-5-25 14:46 编辑

TI工程师: 您好,我在官网上下载了DM368的IBIS模型,仿真DDR2时,DM368的DDR2地址信号和其它控制信号,以及

2018-05-25 07:24:50

时序分析-- 信号完整性问题(SI)

2014-05-16 10:44:11

Altium Designer的混合电路信号仿真工具,在电路原理图设计阶段实现对数模混合信号电路的功能设计仿真,配合简单易用的参数配置窗口,完成基于时序、离散度、信噪比等多种数据的分析。Altium

2019-07-19 07:52:07

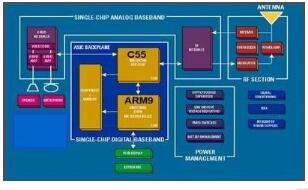

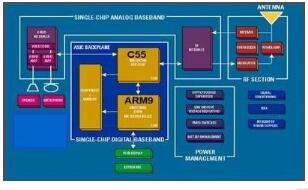

TI 通用数字信号处理系统技术支持摘要 本文详细介绍了DM368 视频前端支持的输入数字信号格式。并以MT9D131 和PC VGA 信号为例,将两者的时序和 DM368 视频前端配置参数一一匹配

2019-06-13 05:00:08

地传送到接收端,就必须进行精确的时序计算和分析。同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。因此,对于一个信号

2012-08-11 17:55:55

ORCAD16.3 仿真的 VSIN信号 相位没有设置的吗?

2017-07-25 13:31:33

,两者相差12.78ps,与仿真结果的12.5ps相吻合。上述,我们通过理论和仿真的验证分析,知道了在线长相等的情况下微带线和带状线会存在时延差异以及导致差异的原因,那在布线设计中,对于一些速率较高,时序要求严格的信号,如DDR的数据信号,建议采用同组同层进行布线的原因之一正是如此。

2022-12-01 09:48:01

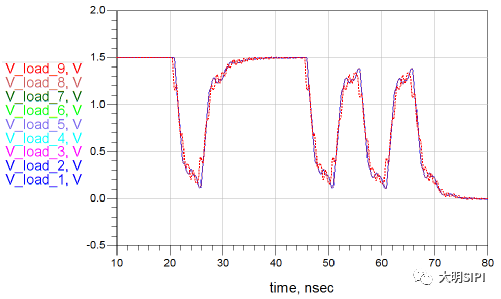

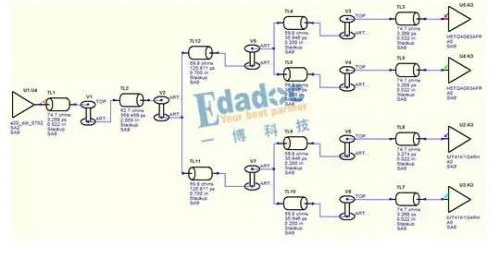

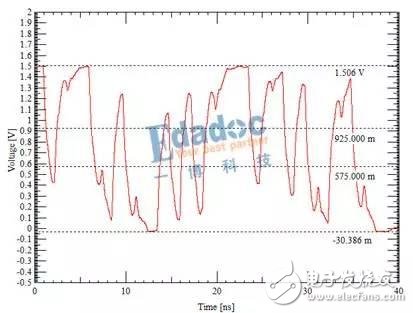

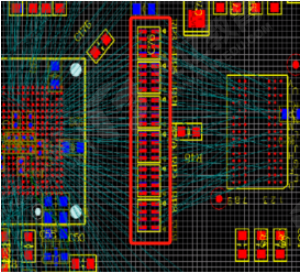

一下具体波形。 建立如下通道,分别模拟3的地址信号与时钟信号。 图1 地址/时钟仿真示意图 为方便计算,我们假设DDR的时钟频率为500MHz,这样对应的地址信号的速率就应该是500Mbps

2018-09-20 10:59:44

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

本文针对以上问题对本人设计的主板PCB的高速信号基本噪声,高速内存时序和电源分配系统噪声进行分析和设计;采用软件仿真的方法对问题进行分析,得出设计解决方案,并将仿真结果转化为设计约束规则指导PCB布局布线设计,最后通过物理测试对设计进行了验证。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:02:40

工程师也知道这种情况下,应该和设计人员普及一下关于时序方面的知识,不然后续遇到类似的DDR,不做仿真的话,可能会需要降频运行。于是将U1的仿真结果给设计人员看,蓝色的是CS,ODT,CKE等信号,绿色

2019-06-20 09:06:44

Speed2000软件使用方法。掌握电路板DDR3/DDR通用时域仿真分析方法, 高速互联信号质量评估与串扰分析,EMC_EMI的信号辐射仿真等仿真技巧等。3.学会将直接将仿真的思路和方法应用与自己

2019-12-06 13:50:07

的掌握Sigrity Speed2000软件使用方法。掌握电路板DDR3/DDR通用时域仿真分析方法, 高速互联信号质量评估与串扰分析,EMC_EMI的信号辐射仿真等仿真技巧等。3.学会将直接将仿真的思路

2019-11-22 14:35:58

什么情况,我们需要DDR信号仿真分析呢?

2021-03-17 07:38:51

时就能看到像在功能仿真的工程文件层次结构,可以找到定义的内部信号。因为在做后仿时,源文件中的信号名称已经没有了,被映射为软件综合后自己生成的信号名,观察起来很不方便。这个设置与ISE里综合右键属性

2012-03-01 11:46:29

功能仿真:可以验证代码的逻辑性,不加任何的时延信息。仿真工具为modelsim(组合逻辑和时序逻辑都可以功能仿真),modelsim不能综合。在modelsim中添加相应的激励信号,调用

2016-08-23 16:57:06

的选定输出作为驱动,并考虑所有已设置的有效终止方式,来进行详细的信号反射仿真。仿真结果以图形方式显示在波形分析器中。 波形分析器 使用波形分析器可以方便地显示出反射仿真和串扰仿真的结果,并可以直接

2018-08-27 16:13:55

引起误触发。Cadence Allegro 17.2反射仿真分析流程中怎么进行信号分析?【1】Cadence Allegro 17.2启动后选择Allegro Sigrity SI产品就可以启动

2020-03-16 11:20:19

线性的均衡基础上加上了一个额外的判决功能。通过仔细阅读DDR5协议,可以看到,DDR5的data信号标准配置是一个4tap的DFE模块。 好,关于协议和理论都太过枯燥,说点仿真的东西吧。我们直接拿到

2021-08-27 16:39:08

时。如果我查看发送的数据和数据从内存中读回并存储在fifo中,chipcope cdc会导致时序约束失败并且还会改变设计的时序性能,因此我无法捕获可靠的数据。我尝试将DDR2信号路由到另一组I / O

2019-05-10 14:25:23

数字信号时序分析装置毕业设计,本人来自中国地质大学通信工程专业,2020学年大二上的通信与信号处理的实习题目便是参考2018年TI杯G题——数字信号时序分析装置,此实习需要自学stm32单片机,具有

2021-08-09 08:33:45

求助一篇关于信号波形仿真的课程设计利用matlab设计出原理框图和主要参数以及程序

2012-12-24 10:47:38

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

2018-01-12 15:26:17

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

2012-08-15 13:04:33

Flyby拓扑和T拓扑的组合,所以既有Flyby拓扑的特点,也就是近端颗粒的信号质量特别差;也有T拓扑的特点,近端的DRAM1和DRAM2一样差。小雷的仿真结果也验证了这一点,上一版近端颗粒的眼图(地址信号

2022-05-11 09:11:48

的stub对信号质量的影响分析。 那主要肯定是讲过孔stub(残桩)对DDR4的影响咯。首先呢作者对DDR4的信号质量做了一些前提的判定和分析,例如要求通道的插损谐振频率点要大于5倍的时钟频率,按本文

2020-02-28 17:13:27

和远端串扰这种方法来研究多线间串扰问题。利用Hyperlynx,主要分析串扰对高速信号传输模型的侵害作用并根据仿真结果,获得了最佳的解决办法,优化设计目标。【关键词】:信号完整性;;反射;;串扰;;近

2010-05-13 09:10:07

高速电路信号完整性分析与设计—信号完整性仿真仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上升沿从20%~80%VCC的时间,一般是ns级或

2009-09-12 10:31:31

高速电路信号完整性分析与设计—时序计算引入:在数字电路中,从一个芯片发信息A到另一个芯片变成信息B,那么这个数字系统失败;如何保证信息不变?关键点,就是在传输过程的任意点都保持时序的正确性。时序概念

2009-09-12 10:28:42

ISA总线信号时序简介:1.0 ISA概况2.0 ISA文献2.1 ISA规范2.2 ISA书籍3.0 ISA结构形式4.0 PC/104结构形式5.0 ISA信号描述6.0 ISA时序图7.0 ISA信号用法8.0 ISA连接器引脚

2009-05-21 11:06:54 242

242 用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)(ALTERA 篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1 界面的。我个人认为,如果是开发StratixII 或CycloneII 或MAXII

2009-06-19 00:26:41 70

70 高速电路信号完整性分析与设计—信号完整性仿真:仿真信号仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上

2009-10-06 11:19:50 0

0 各种液晶屏信号描述及时序分析:TFT 液晶屏接口(数字屏)信号说明VSYNC: vertical synchronization [siŋkrənaizeiʃən]:水平同步信号.HSYNC: horizontal synchronization 垂直同步信号.

2010-03-18 17:47:58 47

47 信号完整性和时序分析的模式变化:简单的接口分析经验法则在分析现代高速接口(如DDR2、PCI Express和SATA-II)时非常不合适。随着新兴标准(如DDR3 和5-10 Gbps串行接口)逐渐普及,

2010-04-27 08:25:54 70

70 新一代数字RF信号分析和信号仿真系统测试:• 雷达和宽带通信系统的测试挑战

• 将“实时分析”的方法带入宽带系统测试

• 为宽带系统测试提供所需带

2010-08-05 14:45:10 46

46 针对高速数字电路印刷电路板的板级信号完整性, 分析了IBIS 模型在板级信号完整性分析中的作用。利用ADS 仿真软件, 采用电磁仿真建模和电路瞬态仿真测试了某个实际电路版

2010-08-23 17:18:04 37

37 定义了时钟单位阶跃信号C(n) 提出了一种利用带相对时钟坐标的逻辑方程表示逻辑信号的方法通过对所设计的DDR SDRAM控制器的读写时序的分析建立了控制器主要信号的时序表达式并利用

2011-09-26 15:34:12 39

39 为保证线阵CCD在图像测量中正常、稳定工作.必须设计出适合其工作的时序驱动电路。在分析TCDl501D线阵CCD驱动时序关系的基础上,通过分析CCD输出的图像信号1,给出了内、外相关双采

2011-11-07 15:08:43 148

148 介绍引起信号完整性问题的主要因素, 利用。进行信号仿真的步骤, 给出了的信号仿真的时比结果, 并以该信号作为分析对象, 详细分析了为判断信号质童的优劣, 对仿真波形进行定量分析

2011-11-30 11:09:46 0

0 文中主要以Matlab为平台,对GPS信号的信号结构(数据信号,C/A码)、GPS的多种干扰方式进行仿真,并分析了不同干扰的干信比与误码率关系。

2011-12-14 14:37:11 101

101 通过Cadence软件建立DDRⅡ信号拓扑结构、仿真信号的串扰、码间干扰、过冲等与信号质量相关的参数,从仿真波形中可以测量出与信号时序相关的参数,从而计算出信号的时序裕量,并为DDRⅡ

2012-02-13 15:16:22 52

52 电路中,数据的传输一般都是在时钟对数据信号进行有序的收发控制下进行的。芯片只能按规定的时序发送和接收数据,过长的信号延迟或信号延时匹配不当都会影响芯片的建立和保持

2012-05-28 16:10:59 1786

1786

ALTERA公司:用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)之学习笔记

2012-08-15 16:00:59 68

68 MATLAB环境下的跳频信号分析与仿真.

2016-01-15 15:15:57 36

36 针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 DDR_SDRAM介绍和时序图,DDR_SDRAM介绍和时序图

2016-02-23 11:58:38 6

6 24C02中IIC总线的应答信号(ACK)时序图分析,很好的单片机学习资料。

2016-03-21 17:30:06 93

93 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 双频GPS信号仿真的电离层误差补偿模型研究_谢杰

2017-03-14 08:00:00 1

1 最新版本的李黎明DDR时序PPT

2017-11-02 17:05:17 0

0 越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。 1.引言 信号要能正常工作都必须满足一

2017-12-01 11:09:05 0

0 高速 PCB 信号完整性仿真分析.pdf

2018-05-07 14:52:31 48

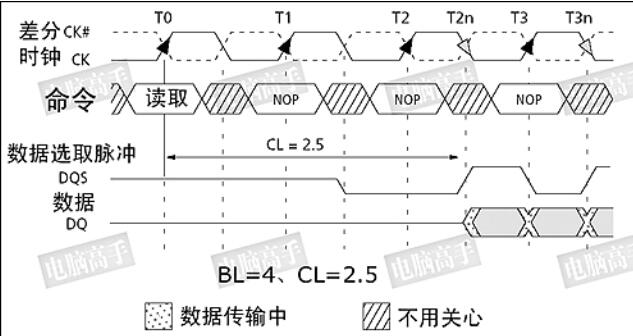

48 Random Access Memory的缩写,即同步动态随机存取存储器。本文首先介绍了DDR工作原理及结构图,其次阐述了DDR DQS信号的处理,具体的跟随小编一起来了解一下。

2018-05-23 16:07:19 50490

50490

本文主要介绍了基于Multisim仿真的交通信号灯设计.

2018-06-28 08:00:00 70

70 对于Layout人员来说,对于DDR这一块,可能主要关注的是信号线之间的等长。下面我们也来复习一下,DDR各组信号需要满足的时序关系:地址/命令,控制和时钟之间等长;DQ与之对应的DQS组内等长;DQS与CLK之间有一个相对宽松的等长关系。

2018-09-15 10:58:00 5804

5804 Altium Designer的混合电路信号仿真工具,在电路原理图设计阶段实现对数模混合信号电路的功能设计仿真,配合简单易用的参数配置窗口,完成基于时序、离散度、信噪比等多种数据的分析。Altium

2018-09-12 08:00:00 0

0 在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题。但是如果信号是100M以上的速度时,布线就很有讲究了。由于最近布过速度高达300M的DDR信号,所以仔细说明一下DDR信号的布线原则和技巧。

2019-03-24 10:00:06 6906

6906

信号完整性的问题主要包括传输线效应,如反射、时延、振铃、信号的过程与下冲以及信号之间的串扰等,涉及传输线上的信号质量及信号定时的准确性。

良好的信号质量是确保稳定时序的关键。由于反射和串扰造成

2019-06-24 15:27:25 1197

1197

学习如何垫分析工具可以识别你的电路设计仿真的关键区域。我们将研究如何分析和快速实现信号和电源完整性和突出关键原因垫桌面仿真和验证是你最好的选择。

2019-11-01 07:10:00 2832

2832 工程师要快速检查信号质量,眼图测试有助于在极短时间内获悉信号完整性状况。 测试 DDR 接口信号质量时,数据眼图分析有助于揭示潜在的信号完整性问题。因此,许多信号完整性工程师都使用眼图功能迅速测定

2020-07-23 15:50:45 4919

4919

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是

2020-11-04 17:02:46 2422

2422

容易引起电路的 SI 问题,信号测试验证也变得越来越困难。一般 DDR 信号测试、仿真验证,大多数用 SPEED2000,大家在学习 DDR 仿真前,可以先补充 SPEED2000 的时域波形仿真

2023-02-07 16:37:34 896

896 通常,DDR设计完成之后 ,对信号质量并没有一个完全确定的概念,需要我们通过仿真和测试的手段去判断和验证。而此时,往往我们拿到的就是一个波形,测试波形或者仿真波形,该如何去判断其信号质量,参照的标准

2021-04-09 10:04:19 4876

4876

今天要给大家分享的文章如下,这次的题目很容易读懂,就叫DDR4通道里,过孔的stub对信号质量的影响分析。 那主要肯定是讲过孔stub(残桩)对DDR4的影响咯。首先呢作者对DDR4的信号质量做了

2021-03-23 11:46:59 6157

6157 一些设计方法在以前已经成熟的使用过。 1 介绍 目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。 对于如此高的速度,从PCB的设计角度来帮大家分析,要做到严格的时序匹配,以满足信号的完整性,

2021-03-25 14:26:01 3864

3864

电子发烧友网为你提供什么情况,我们需要DDR信号仿真分析呢?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-30 08:44:49 14

14 Hyperlynx信号完整性仿真性分析。

2021-04-07 13:59:10 121

121 高速电路信号完整性分析与设计—时序计算

2022-02-10 17:16:41 0

0 高速电路信号完整性分析与设计—信号完整性仿真

2022-02-10 17:29:52 0

0 华为硬件信号质量与时序测试指导书

硬件信号测试用例

建立保持时间

信号质量等测量方法

2022-10-21 16:18:29 27

27 定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同 引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

2022-11-16 14:56:00 1778

1778 随着信号速率的不断提高,对信号时序的要求也越来越严格。在PCB设计中,我们等长的最终目的都是为了等时,以满足信号的时序要求。因此,需要我们对信号在传输线上的时延有一定的了解,下面小编将会通过理论分析和利用SIGRITY软件进行仿真验证跟大家一起深入的了解信号在传输线上的时延情况。

2022-12-01 09:46:17 483

483 信号的时序要求就是数据信号与其对应的时钟信号保持某种同步关系。数据的采样同样依赖于某特定的时钟,由于信号边沿频谱高最容易受干扰,因此在采样时钟对数据信号进行采样时,应尽可能远离信号变化的边沿。

2023-03-08 15:38:00 1730

1730 目前对于DDR4、DDR5等并行信号,信号速率越来越高,电源性能要求也越来越高,今天我们就来看看电源噪声对信号质量的影响;

2023-04-21 09:47:46 1291

1291 这里介绍两种方式改善带有ECC的奇数负载的DDR2信号质量。一种不需要改变拓扑结构,另一种需要对拓扑结构进行调整。

2023-06-15 17:39:34 474

474

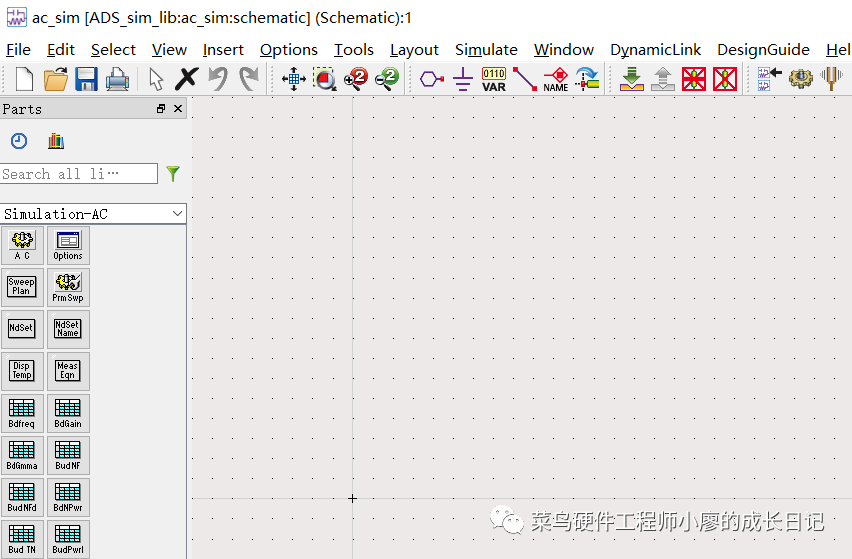

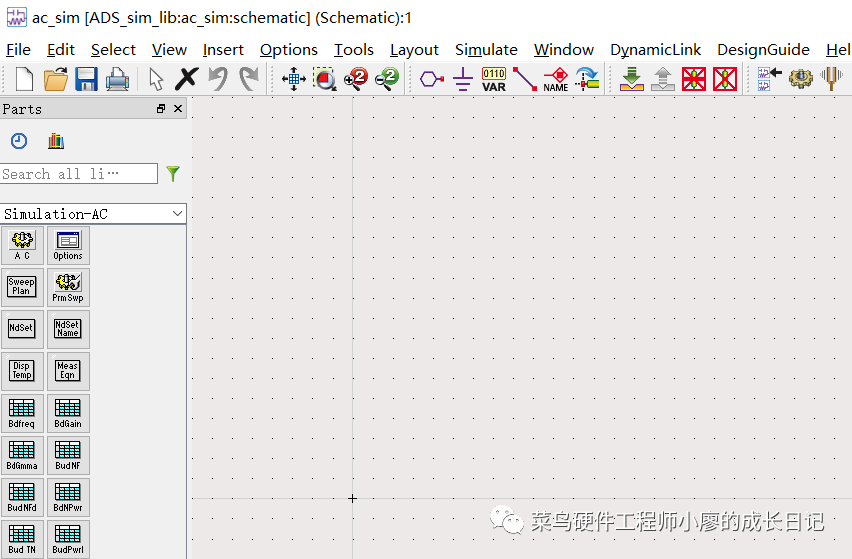

交流仿真的概念:交流放着是射频电路中最重要的仿真方式之一,主要用于分析电路的小信号特性和噪声特性。

2023-06-29 11:17:31 8086

8086

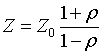

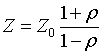

当信号进入射频后,阻抗匹配变得十分重要,差的匹配造成的反射将严重影响信号质量,甚至可能造成误操作,因此必须以传输线理论进行分析,即印制电路板上每条连线都有其特性阻抗。

2023-07-03 11:29:24 1430

1430

何为信号完整性的分析信号完整性包含:波形完整性(Waveformintegrity)时序完整性(Timingintegrity)电源完整性(Powerintegrity)信号完整性分析的目的就是

2023-08-17 09:29:30 3111

3111

现一系列问题,如串扰、反射波、时钟抖动等。为了确保高速信号传输的稳定和可靠性,需要进行仿真串扰。本文将详细介绍高速信号仿真的串扰以及为什么需要进行仿真。 对于高速信号来说,串扰是一种令人头疼的问题。串扰是指高速信

2023-09-05 15:42:31 472

472 时序仿真与功能仿真的区别在于 时序仿真与功能仿真是电子设计自动化(EDA)中最常见的两种仿真方式。虽然二者都是仿真技术,但根据仿真模型和目的的不同,它们之间还是存在一些根本差异。 1.定位 时序仿真

2023-09-08 10:39:40 2654

2654 EDA仿真,它模拟一个数字电路中时序的行为。时序行为通常包括数据信号传输的时序,如周期时间或LATCH信号的上升沿下降沿。它通常应用于验证设计延迟、时序、时序违规和时序冲突等问题。 时序仿真的主要目的是在设计的任何阶段,从RTL级别

2023-09-17 14:15:02 2254

2254 高速电路板设计与仿真--信号与电源完整性分析

2022-12-30 09:22:20 82

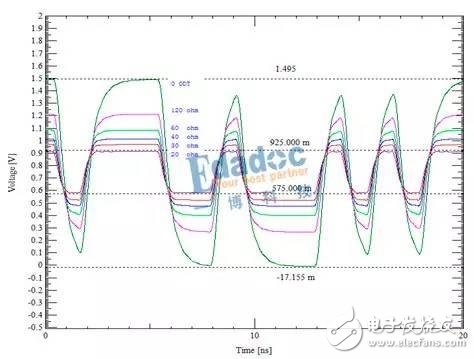

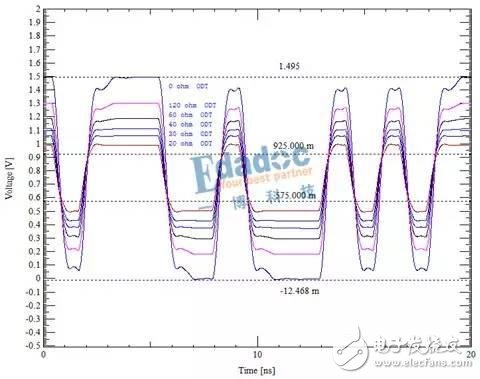

82 数据线都有串联一个电阻,其实这个串联电阻的作用是进行阻抗匹配的,防止信号发生反射。 我们接下来用allegro软件自带的sigxplorer软件进行仿真验证一下, 我们主要分析验证一下这个电阻他是如何进行阻抗匹配以及电阻阻值应该如何选取! 首先我们需要按

2023-11-06 07:45:02 205

205

是指在芯片设计过程中,对电路的功能和性能进行仿真验证的环节。它主要关注电路的功能性、时序和功耗等方面,以确保设计的正确性和可行性。前仿真通常在物理布局之前进行,因此也称为静态时序分析或网表级仿真。 后仿真:后仿

2023-12-13 15:06:55 1484

1484 DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行

2023-12-25 07:45:01 211

211

DDR加终端匹配电阻和不加信号质量的区别 DDR(双倍数据传输速率)是一种常用于计算机内存的高速数据传输技术。在DDR中,终端匹配电阻和信号质量是对于数据传输稳定性至关重要的两个方面。下面将详细

2023-12-29 13:54:22 316

316

电子发烧友App

电子发烧友App

评论