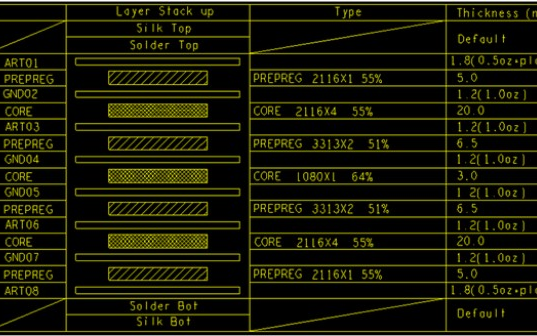

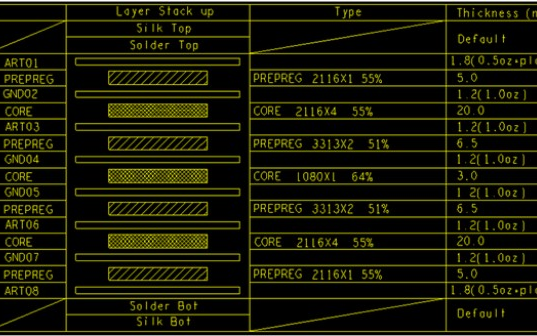

向大神请教:在设计一个10层板PCB时,一些关键信号需要做阻抗匹配,对于如何选择参考层有一些不明白,如下:1、中间信号层5做阻抗匹配时,是否可以选用电源层4和电源层7共同作为参考层?2、TOP信号层1某些信号做阻抗匹配时,是否可选用信号层3作为参考层?层叠示意图

2022-04-24 11:23:09

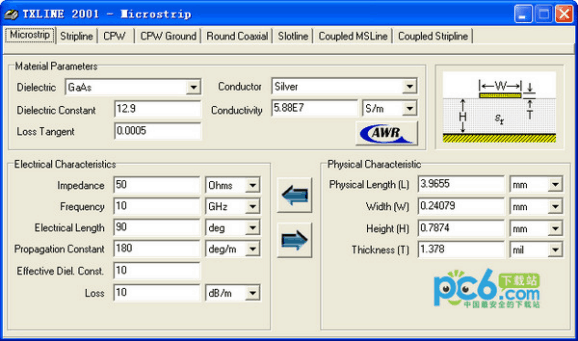

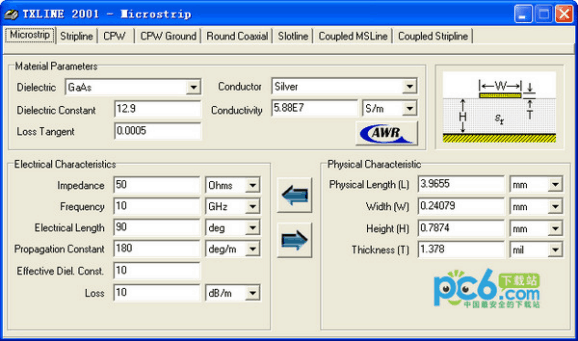

在高速数字电路设计流程中,第一步需要做的就是根据系统的复杂程度,成本因素等相关方面决定印制电路板(PCB)的叠层结构(Stack),而在PCB stack设计的过程中,特征阻抗也是一个重点关注的问题。

2019-05-23 07:13:34

4.3.3 实验设计3:4层PCB 本章将考虑4层PCB叠层的几种不同变体。这些变化中最简单的是基于实验设计2层叠层(第4.3.2节),外加两个额外的内部信号层。假设附加层主要由许多较薄的信号

2023-04-20 17:10:43

扰,从而导致电路功能失效。在两信号层之间加入地平面可以有效地避免串扰。(5)多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。(6)兼顾层

2015-03-06 11:02:46

了信号线的特征阻抗,也可有效地减少串扰。所以,对于某些高端的高速电路设计,已经明确规定一定要使用6层(或以上的)的叠层方案,如Intel对PC133内存模块PCB的要求。这主要就是考虑到多层板在电气

2016-05-17 22:04:05

本帖最后由 lee_st 于 2017-10-31 08:48 编辑

PCB叠层设计及阻抗计算

2017-10-21 20:44:57

PCB叠层设计及阻抗计算

2017-09-28 15:13:07

PCB叠层设计及阻抗计算

2016-06-02 17:13:08

到的电源优先铺整块铜皮;易受干扰的、高速的、沿跳变的优选走内层等等。 下表给出了多层板层叠结构的参考方案,供参考。 PCB设计之叠层结构改善案例(From金百泽科技) 问题点 产品有8组网口与光口,测试

2018-09-18 15:12:16

、EMC、制造成本等要求有关。对于大多数的设计,PCB的性能要求、目标成本、制造技术和系统的复杂程度等因素存在许多相互冲突的要求,PCB的叠层设计通常是在考虑各方面的因素后折中决定的。高速数字电路和射须电路通常采用多层板设计。

2019-09-17 14:11:49

是电路板设计的一个重要指标,特别是在高频电 路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

2019-05-30 07:18:53

成反比.在一定厚度范围内,防焊厚度越厚,阻抗越低,防焊厚度越薄,阻抗越高。

12 问:阻抗计算那个工具最方便?答:当然是华秋DFM啦!华秋DFM阻抗工具自动生成叠层图,支持单独计算某条阻抗和全部计算所有阻抗,还支持反算功能,计算好的阻抗数据可以导出保存,同时导出阻抗计算图和叠层图方便用户存档。

2024-01-05 10:50:17

,所以折中采用50Ω阻抗是当时最优的选择。三、50Ω容易进行阻抗匹配PCB设计中,经常需要进行阻抗匹配,以减少信号反射和干扰。设计PCB走线时,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材

2023-04-11 10:32:34

时一定要对板上走线的阻抗进行控制,才能尽可能避免信号的反射以及其他电磁干扰和信号完整性问题,保证PCB板的实际使用的稳定性。PCB板上微带线和带状线阻抗的计算方法可参照相应的经验公式。 五、印制电路

2018-09-18 15:50:04

PCB板阻抗设计:阻抗线有无参考层阻抗如何变化?生产PCB时少转弯的阻抗线的阻抗更容易控制稳定性?

2023-04-10 17:03:31

4.4.3 实验设计9:通用的4层PCB 通过增加两个内部信号层,实验设计6的2层叠加现在将增加到4层。与以前一样,假设这些层主要由许多较薄的信号走线组成,而不是大面积连续铺铜。 模拟的内部

2023-04-21 15:04:26

`实用的PCB阻抗计算,图文并茂,超级齐全!`

2020-06-20 11:43:14

PCB线路板叠层设计要注意哪些问题呢?

2021-03-29 08:12:19

PCB设计中叠层算阻抗时需注意哪些事项?

2019-05-16 11:06:01

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到

2018-01-22 14:41:32

本帖最后由 yfsjdianzi 于 2014-5-11 14:23 编辑

叠层电感也就是非绕线式电感,是电感分类的其中一类。外形尺寸小,闭合电路,无交互干扰,适合于高密度安装,无方

2014-05-10 20:04:18

叠层电感在现实中应用也十分广泛,目前叠层电感类产品被广泛用于笔记本电脑数位电视,数位录放影机,列表机,硬式磁碟机,个人电脑和其安一般消费性及电脑主品上输入、输出线路之杂讯消除。

2019-10-17 09:00:27

% ,如其他默认的参数需要调整,可以在参数配置里面填写修改,保存即可。

二、计算阻抗匹配介质厚度压合图

1、硬板叠层图

1) 华秋DFM软件可以 自动生成叠层图 ,也可以手动填写层数、板厚、铜厚等,用叠层图

2023-09-13 11:03:22

阻抗计算方法,希望有所帮助

2013-06-10 16:58:32

就是降低了成本;另一方面,合拼的PCB板,如采用相对一致的叠层结构,在压合工序可提高产品质量。

下图是华秋推荐叠层结构其中之一,更多的叠层设计可参考华秋DFM阻抗计算,也可参考华秋PCB官网推荐叠层

2023-05-26 11:46:06

之前很多学员不知道如何去计算阻抗,如何去进行叠层,这里写了一个详细的图文教程,希望对大家有所帮助。不懂的大家也可以进我们小组进行讨论

2018-11-05 15:15:15

路径变长,这个电源层是否还是可以作为阻抗的参考,实际测试的信号阻抗是否会有影响呢?这种叠层非常常见,而且很多时候内层还会放置一些重要的如DDR4等信号,比如下面的真实PCB设计。图中白色为Art05层上

2021-11-05 17:33:47

为此困扰,这里推荐一款可以一键智能计算阻抗自动叠层的工具: 华秋DFM软件 ,使用其阻抗计算功能,可以高效轻松反算和计算所需阻抗和线宽线距等。

2023-12-25 13:46:25

为此困扰,这里推荐一款可以一键智能计算阻抗自动叠层的工具: 华秋DFM软件 ,使用其阻抗计算功能,可以高效轻松反算和计算所需阻抗和线宽线距等。

2023-12-25 13:48:49

不慌不忙的打开PCB文件,雷豹见Chris直接跳过了检查PCB上的走线这一步,径直的打开了叠层设置,然后给雷豹指一下这个地方,没错,指的就是下面这个红框框的地方。

雷豹感觉好像懂了一点了,原来该客户

2023-06-02 15:32:02

请问LED灯的阻抗计算方法是什么?

2020-03-06 14:43:47

allegro16.5多层PCB板的叠层设计时,内电层设计为正片或负片的选项不知道怎样处理,我原来用的是allegro15.7,allegro15.7设置内电层时,它有个选项,可选为正片或负片,但allegro16.5没看到这个选项,求教知道的人指导一下

2015-09-20 18:45:24

影响因素则与特性阻抗相同。

7、共面阻抗

阻抗线距导体的间距与阻抗成正比,间距越大,阻抗越大,其它影响因素则与特性阻抗相同。

阻抗计算神器验证影响因素

1、叠层图制作

这里推荐一款免费的国产工具:华

2023-05-04 16:43:04

,可以在参数配置里面填写修改,保存即可。

计算阻抗匹配介质厚度压合图

硬板叠层图

1、华秋DFM软件可以 自动生成叠层图 ,也可以手动填写层数、板厚、铜厚等,用叠层图的介质厚度匹配阻抗。

2、如需调整叠

2023-09-15 14:11:33

如题,一个计算线路板叠层参数的算数表格。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:15:56

您还在为阻抗设计头疼吗?这里有齐全的阻抗参数及叠层结构。有它您无需再去仿真,我们已将其一一列出,如 90ohm线宽线距为7/6mil 或 5/4mil ,结合布线空间选择对应的线宽线距。

2020-06-10 20:54:11

基于优化多层印制板,改进信号完整性的设计,主要通过调整叠层设计中的各层导线宽度、基板厚度、填充层厚度和绝缘材料厚度,4个维度参数,从而改变信号传输路径特性阻抗的方法,有具体应用实例。

2021-04-06 11:15:43

多层板叠层设计规则,单层、双层PCB板的叠层,推荐设计方式,设计方案讲解。

2021-03-29 11:58:10

`非常经典的PCB阻抗设计教程资料,详细介绍了阻抗参数计算、多层面板设计步骤与思路,值得一看。`

2021-03-29 14:14:04

常见的PCB叠层结构,四层板、六层板、八层板十层板叠层设计及注意事项。

2021-03-29 11:49:35

阻抗的电流返回路径最重要的就是合理规划这些参考平面的设计。图1所示为一种典型多层PCB叠层配置。图1 一种典型多层PCB叠层配置回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:18:25

的众多变量。本文将讨论如何确定哪些PCB叠层信息需要了解的方式方法。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:13:17

手机PCB Layout层数选择与叠层设计方案剖析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:10:24

本文主要介绍多层PCB设计叠层的基础知识,包括叠层结构的排布一般原则,常用的叠层结构,叠层结构的改善案例分析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:06:58

本帖最后由 张飞电子学院吕布 于 2021-4-12 16:36 编辑

一到八层电路板的叠层设计方式 电路板的叠层安排是对 PCB 的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机

2021-04-12 16:35:28

,其余影响因素则与特性阻抗相同。

共面阻抗

阻抗线距导体的间距与阻抗成正比,间距越大,阻抗越大,其它影响因素则与特性阻抗相同。

阻抗计算神器验证影响因素

叠层图制作

这里推荐一款免费的国产工具:华秋

2023-04-28 11:01:02

高速叠层设计原则:考虑因素:BGA 扇出、局部布线密度、阻抗控制、顾客要求、SI/PI考虑、成本、电设计源分割、板厚、板厚与孔径比工艺要求:对称性表层与内层不要选择4.0mil以下介质不要选

2022-03-02 06:09:06

则与特性阻抗相同。

共面阻抗

阻抗线距导体的间距与阻抗成正比,间距越大,阻抗越大,其它影响因素则与特性阻抗相同。

阻抗计算神器验证影响因素

叠层图制作

这里推荐一款免费的国产工具:华秋DFM软件

2023-04-28 11:12:07

PCB设计中层叠结构的设计建议:1、PCB叠层方式推荐为Foil叠法2、尽可能减少PP片和CORE型号及种类在同一层叠中的使用(每层介质不超过3张PP叠层)3、两层之间PP介质厚度不要超过21MIL

2017-01-16 11:40:35

听说多级阻抗PCB有独特的计算方法?一起来看看吧

2023-04-14 15:50:20

多层PCB如何定义叠层呢?

2023-04-11 14:53:59

各位pcb设计师你们好请问PCB布线有关的如何计算阻抗 收到者求回复感谢!

2019-09-25 03:18:38

双层pcb板在设计USB差分90欧姆的阻抗时为何选择共面阻抗模式计算?具体什么时共面阻抗?

2019-09-10 04:37:34

搞定叠层,你的PCB设计也可以很高级

2020-12-28 06:44:43

计算出外部微带的所需走线宽度为2.17mil,内部带状线为2.23mil,目标阻抗为50欧姆。 ML605文件说,外层需要4.5mil的痕迹,内层需要3.25mil。ML605叠层是使用2D场解算器

2019-08-29 09:58:17

影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。 一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度

2020-09-07 17:54:12

制作的线路板的铜线),相对某一参考层(也就是常说的屏蔽层、影射层或参考层),其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它实际上是电阻抗、电感抗、电容抗等一个矢量总和。2、控制PCB

2016-10-10 14:38:27

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗

2020-09-07 17:52:55

普通铁氧体电感、叠层扼流电感及叠层功率电感有何区别?

2011-10-16 20:20:01

贴片电感从制造工艺上可分为:绕线型、叠层型、编织型和薄膜片式电感器,常用的为绕线型电感和叠层型电感,绕线型电感是传统绕线电感器小型化的产物,而叠层型电感采用多层印刷技术和叠层生产工艺制作,体积比绕线

2020-06-02 09:33:23

`叠层电感也就是非绕线式电感,叠层电感是电感按结构不同对电感进行分类的其中一类。特 性: 1.外形尺寸小。 2.闭合电路,无交互干扰,适合于高密度安装。 3.无方向性,规范化的自动贴片安装外形

2013-08-29 17:41:52

电路板的叠层设计是对PCB的整个系统设计的基础,叠层设计若有缺陷,将最终影响到整机的EMC性能。叠层设计是一个复杂的,严谨过程,当然,设计开发,没必要从零开始经过一系列的复杂计算和仿真,来确定设计方案是否合适,仅需要总结前人的经验,选择合适系统的叠层方案。

2021-11-12 07:59:58

工作,其他7组光口通信正常。1、问题点确认根据客户端提供的信息,确认为L6层光口8与芯片8之间的两条差分阻抗线调试不通;2、客户提供的叠构与设计要求改善措施 影响阻抗信号因素分析: 线路图分析:客户

2019-05-29 08:11:41

、电源的分割,一般的BGA都有IO电压和Core电压,需要在电源层将其分隔开。7、阻抗的控制,如果BGA的某些信号线需要特殊阻抗,要注意线径和线宽,并计算好阻抗,连同PCB的Stack一起计算。8

2011-10-21 09:48:17

本帖最后由 山文丰 于 2020-9-4 14:44 编辑

华秋DFM软件的阻抗计算使用方法视频地址:

2020-09-04 14:43:46

PCB阻抗怎么来的?如何计算?

2021-03-18 06:27:04

,可以在参数配置里面填写修改,保存即可。

计算阻抗匹配介质厚度压合图

硬板叠层图

1、华秋DFM软件可以 自动生成叠层图 ,也可以手动填写层数、板厚、铜厚等,用叠层图的介质厚度匹配阻抗。

2、如需调整叠

2023-09-15 14:12:46

这个叠层图是什么意思呢

2015-06-11 09:23:35

信号线(高速信号)数量不多,区域集中,也可以使用这个层叠方案,局部高速信号区域对应的相邻层铺地铜,做成局部3层布线(L1&L4&L6)。叠层如下(阻抗计算从略,大家可以自己算算,后面

2019-05-30 07:20:55

信号线(高速信号)数量不多,区域集中,也可以使用这个层叠方案,局部高速信号区域对应的相邻层铺地铜,做成局部3层布线(L1&L4&L6)。叠层如下(阻抗计算从略,大家可以自己算算,后面

2022-03-07 16:04:23

关键信号线(高速信号)数量不多,区域集中,也可以使用这个层叠方案,局部高速信号区域对应的相邻层铺地铜,做成局部3层布线(L1&L4&L6)。叠层如下(阻抗计算从略,大家可以自己算算,后面

2019-05-29 07:26:53

铜排的导电能力的计算方式,不一定所有的汽车工程师了解,所以在设计电池导电连接时,对于铜排的设计中,载流量的核算成了工程师们一个头疼的问题,有没有准确的叠层铜排的导电电流计算公式呢?铜排软连接载流量也会

2020-06-07 18:50:22

的低阻抗的电流返回路径最重要的就是合理规划这些参考平面的设计。图1所示为一种典型多层PCB叠层配置。 信号层大部分位于这些金属实体参考平面层之间,构成对称带状线或是非对称带状线。此外,板子的上、下两个

2018-11-27 15:14:59

高速PCB设计的叠层问题

2009-05-16 20:51:30

而言就是降低了成本;另一方面,合拼的PCB板,如采用相对一致的叠层结构,在压合工序可提高产品质量。

下图是华秋推荐叠层结构其中之一,更多的叠层设计可参考华秋DFM阻抗计算,也可参考华秋PCB官网推荐叠层

2023-05-26 11:30:36

PCB设计时阻抗计算的板材常识学习,介电常数是个重要的参数,在阻抗计算公式里,它对阻抗是有较大影响的

2011-11-09 16:22:57 3737

3737

附件是一款PCB阻抗匹配计算工具,点击CITS25.exe直接打开使用,无需安装。附件还带有PCB连板的一些计算方法,连板的排法和PCB联板的设计验验。 PCB设计的經驗建議: 1.一般連板長寬比率

2012-11-02 17:11:10 1081

1081 PCB阻抗匹配计算工具与教程,感兴趣的小伙伴们可以瞧一瞧。

2016-10-14 14:17:18 0

0 PCB阻抗匹配计算工具与教程

2017-01-04 14:57:53 0

0 特征阻抗的计算方法

2017-06-09 14:53:12 27

27 本文主要介绍的是阻抗匹配,首先介绍了阻抗匹配条件,其次阐述了如何理解阻抗匹配及常见阻抗匹配的方式,最后介绍了pcb阻抗匹配如何计算,具体的跟随小编一起来了解一下。

2018-05-02 17:11:28 38669

38669

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。

2018-12-01 10:56:49 3296

3296 计算方法非常成熟,不同软件的计算方法也没有差别。阻抗计算和过程之间的一些权衡相对麻烦。主要目的是实现我们的阻抗控制目的,同时也确保处理方便,并最大限度地降低处理成本。 下面我们总结一下设计时阻抗计算的一些注意事项PCB层叠起来可以帮助

2019-07-29 14:02:17 2435

2435

关于阻抗的话题已经说了这么多,想必大家对于阻抗控制在pcb layout中的重要性已经有了一定的了解。俗话说的好,工欲善其事,必先利其器。要想板子利索的跑起来,传输线的阻抗计算肯定不能等闲而视之。

2019-10-27 09:54:03 20187

20187

为了很好地对PCB进行阻抗控制,首先要了解PCB的结构。

2021-03-22 14:30:38 0

0 在 STM32 无线系列产品的 PCB 设计中,需要对射频部分电路进行阻抗控制,良好的阻抗控制可以减少信号衰减、反射和 EMC 辐射。本篇 LAT 主要介绍印制电路板(PCB)上射频走线阻抗仿真计算

2022-06-16 16:36:21 5063

5063 PCB阻抗设计及计算简介

2022-12-30 09:20:41 11

11

电子发烧友App

电子发烧友App

评论