一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型

1.用户自定义数据类型

使用关键字TYPE,例如:

TYPE my_integer IS RANGE -32 TO 32;

–用户自定义的整数类型的子集

TYPE student_grade IS RANGE 0 TO 100;

–用户自定义的自然数类型的子集

TYPE state IS (idle, forward, backward, stop);

–枚举数据类型,常用于有限状态机的状态定义

一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型

在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)

ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;

–定义新的数组类型语法结构

SIGNAL signal_name: type_name [:= initial_value];

–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明

例如:

TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);

–滤波器输入延迟链类型定义

TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);

–滤波器系数类型定义

SIGNAL delay_regs: delay_lines;– 信号延迟寄存器声明

CONSTANT coef: coeffs := (); –常量系数声明并赋初值

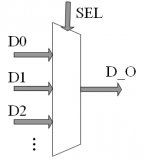

4.端口数组

在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

—————————————PACKAGE———————————-

library ieee;

use ieee.std_logic_1164.all;

——————————————

PACKAGE my_data_types IS

TYPE vector_array IS ARRAY (natural range 《》) OF STD_LOGIC_VECTOR(7 DOWNTO 0); –声明8位的数组

END my_data_types;

———————————–Main Code—————————————

library ieee;

use ieee.std_logic_1164.all;

use work.my_data_types.all; –用户自定义包集

——————————————————————

ENTITY mux IS

PORT (inp: IN vector_array(0 to 3);

END mux;

——————————————————————————-

5.有符号数和无符号数

要使用SIGNED和UNSIGNED类型数据,必须在代码开始部分声明ieee库中的包集std_logic_arith。它们支持算术运算但不支持逻辑运算。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

……

SIGNAL a: IN SIGNED (7 DOWNTO 0);

SIGNAL b: IN SIGNED (7 DOWNTO 0);

SIGNAL x: IN SIGNED (7 DOWNTO 0);

……

v 《= a + b;

w 《= a AND b;–非法(不支持逻辑运算)

——————————————————————————-

STD_LOGIC_VECTOR类型的数据不能直接进行算术运算,只有声明了std_logic_signed和std_logic_unsigned两个包集后才可以像SIGNED和UNSIGNED类型的数据一样进行算术运算。

6.数据类型转换

在ieee库的std_logic_arith包集中提供了许多数据类型转换函数:

1. conv_integer(p): 将数据类型为INTEGER,UNSIGNED,SIGNED,STD_ULOGIC或STD_LOGIC的操作数p转换成INTEGER类型。不包含STD_LOGIC_VECTOR。

2. conv_unsigned(p,b):将数据类型为INTEGER,UNSIGNED,SIGNED或STD_ULOGIC的操作数p转换成位宽为b的UNSIGNED类型数据。

3. conv_signed(p,b):将数据类型为INTEGER, UNSIGNED, SIGNED或STD_ULOGIC的操作数p转换成位宽为b的SIGNED类型的数据。

4. conv_std_logic_vector(p, b):将数据类型为INTEGER, UNSIGNED, SIGNED或STD_LOGIC的操作数p转换成位宽为b的STD_LOGIC_VECTOR类型的数据。

二、运算操作符和属性

1.运算操作符

l赋值运算符

赋值运算符用来给信号、变量和常数赋值。

《=用于对SIGNAL类型赋值;

:=用于对VARIABLE,CONSTANT和GENERIC赋值,也可用于赋初始值;

=》用于对矢量中的某些位赋值,或对某些位之外的其他位赋值(常用OTHERS表示)。

例:

SIGNAL x: STD_LOGIC;

VARIABLE y: STD_LOGIC_VECTOR(3 DOWNTO 0);–最左边的位是MSB

SIGNAL w: STD_LOGIC_VECTOR(0 TO 7);–最右边的位是MSB

x 《= ‘1’;

y := “0000”;

w 《= “1000_0000”;– LSB位为1,其余位为0

w

l逻辑运算符

操作数必须是BIT, STD_LOGIC或STD_ULOGIC类型的数据或者是这些数据类型的扩展,即BIT_VECTOR, STD_LOGIC_VECTOR,STD_ULOGIC_VECTOR。

VHDL的逻辑运算符有以下几种:(优先级递减)

ŸNOT —— 取反

ŸAND —— 与

ŸOR —— 或

ŸNAND —— 与非

ŸNOR —— 或非

ŸXOR —— 异或

l算术运算符

操作数可以是INTEGER, SIGNED, UNSIGNED, 如果声明了std_logic_signed或std_logic_unsigned,可对STD_LOGIC_VECTOR类型的数据进行加法或减法运算。

+ —— 加

-—— 减

* —— 乘

/ —— 除

** —— 指数运算

MOD —— 取模

REM —— 取余

ABS —— 取绝对值

加,减,乘是可以综合成逻辑电路的;除法运算只在除数为2的n次幂时才能综合,此时相当于对被除数右移n位;对于指数运算,只有当底数和指数都是静态数值(常量或GENERIC参数)时才是可综合的;对于MOD运算,结果的符号同第二个参数的符号相同,对于REM运算,结果的符号同第一个参数符号相同。

l关系运算符

=, /=,

左右两边操作数的类型必须相同。

l移位操作符

其中左操作数必须是BIT_VECTOR类型的,右操作数必须是INTEGER类型的(可以为正数或负数)。

VHDL中移位操作符有以下几种:

usll逻辑左移– 数据左移,右端补0;

usrl逻辑右移– 数据右移,左端补0;

usla算术左移– 数据左移,同时复制最右端的位,填充在右端空出的位置;

usra算术右移– 数据右移,同时复制最左端的位,填充在左端空出的位置;

urol循环逻辑左移 — 数据左移,从左端移出的位填充到右端空出的位置上;

uror循环逻辑右移 – 数据右移,从右端移出的位填充到左端空出的位置上。

例:x 《= “01001”,那么:

y 《= x sll 2;–逻辑左移2位,y《=”00100”

y 《= x sla 2;–算术左移2位,y《=”00111”

y 《= x srl 3;–逻辑右移3位,y《=”00001”

y 《= x sra 3;–算术右移3位,y《=”00001”

电子发烧友App

电子发烧友App

评论