锁相环电路

锁相环

2009-09-25 14:28:39 7723

7723

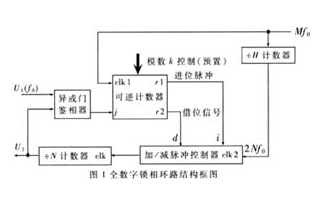

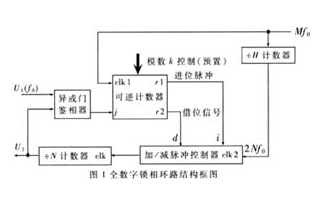

本文采用一种基于比例积分(PI)控制算法的环路滤波器应用于带宽自适应的全数字锁相环,建立了该锁相环的数学模型

2010-10-14 10:03:25 1792

1792

本文针对传统锁相环所存在的锁相范围窄、环路带宽和控制参数固定、以及提高锁相速度与减小稳态误差相互制约等问题,提出了一种新型带宽自适应全数字锁相环的设计方案。该设计方案中的系统采用比例积分控制

2014-01-17 11:33:47 3704

3704

本文在说明全数字锁相环的基础上,提出了一种利用FPGA设计一阶全数字锁相环的方法,并给出了关键部件的RTL可综合代码,并结合本设计的一些仿真波形详细描述了数字锁相环的工作过程,最后对一些有关

2018-10-25 09:17:13 9370

9370 大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 7303

7303

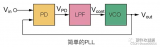

Controlled Oscillator:VCO)。有了这三个模块的话,最基本的锁相环就可以运行了。但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)

2023-09-03 12:01:12 3021

3021

什么是锁相环 (PLL)?一个锁相环PLL电路通常由哪些模块组成?

2022-01-17 06:01:54

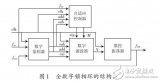

。传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。 随着数字技术的发展,全数字锁相环ADPLL(AllDigital

2010-03-16 10:56:10

捕获比较单元以及3路性能优越的PWM产生模块,轻松的实现了数字锁相环的 功能。图4 假点判断流程4 结论本文通过在硬件上提前过零检测来补偿加重滤波器带来的相位滞后;软件上加入判断过零点真伪的功能,以及

2018-12-03 14:01:24

本文按照数字锁相环设计的步骤,采用手把手的方式讲述设计过程和原理,旨在给数字锁相环初次设计者提供一个思路,缩短开发的时间。 有关数字锁相环的帖子不断出现,但大多没有讲述其原理。翻开有关锁相环的书总是

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

锁相环,而他们都是属于软件锁环的范畴。在电力仿真软件中,一般都有PLL模块,只需要将该模块应用一下即可实现锁相环的功能,即该模块可输出系统相角。其实,所谓的PLL模块就是实现上面说的这么一团东西的,在

2015-01-04 22:57:15

该文章是完全原创,用最简洁的语言讲清楚FPGA实现负反馈的精要。震撼!FPGA实现负反馈控制纯数字锁相环!.zip (225.26 KB )

2019-04-30 04:50:41

LabVIEW锁相环(PLL) 锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环

2022-05-31 19:58:27

咨询STM32F407可以实现数字锁相环功能吗,在实现中怎么设置PLL倍频

2024-07-04 07:32:00

a[10]=[0],用观察窗口观察变量时,只有a[0]=0,其他值仍然是随机值。难道数组的初始化必须对每个元素分别赋值吗?

2. 单相数字锁相环的设计。目前我们在进行单相光伏并网逆变器的开发,在对电网相位的跟踪上处理不是特别好,请问贵司有没有数字锁相环的程序包或者相关的说明文档可以参考?

2018-05-14 03:22:42

有没有大神有用Verilog代码写的数字锁相环程序呀,求 。谢谢

2017-07-05 22:54:56

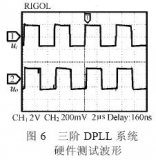

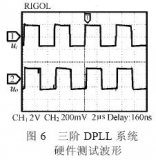

摘要:数字三相锁相环中含有大量乘法运算和三角函数运算,占用大量的硬件逻辑资源。为此,提出一种数字三相锁相环的优化实现方案,利用乘法模块复用和CORDIC算法实现三角函数运算,并用Vetilog

2019-06-27 07:02:23

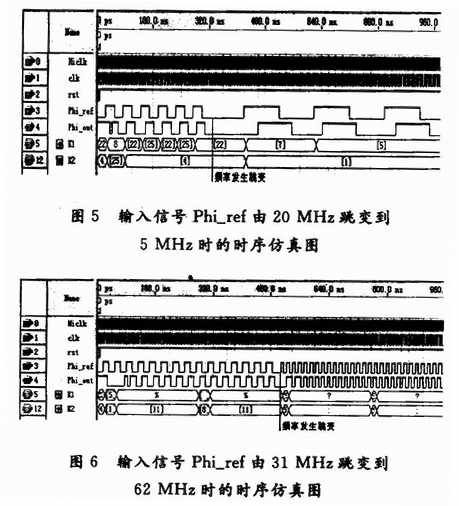

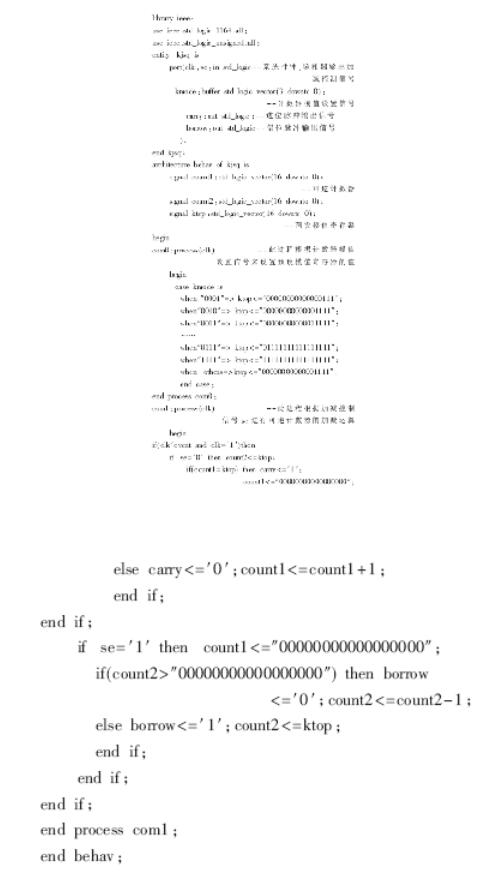

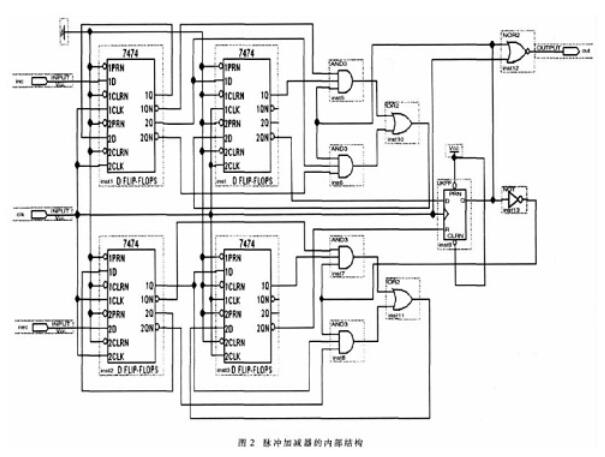

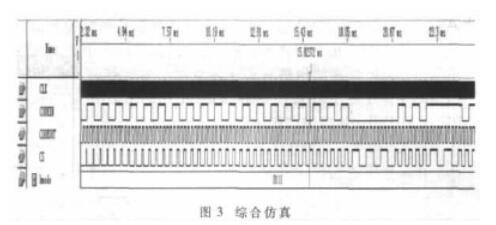

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

内部自带的16位捕获比较单元以及3路性能优越的PWM产生模块,轻松的实现了数字锁相环的功能。图4 假点判断流程4 结论 本文通过在硬件上提前过零检测来补偿加重滤波器带来的相位滞后;软件上加入判断过零点

2018-12-05 09:53:26

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

经典数字锁相环路结构及工作原理是什么?改进的数字锁相环结构及工作原理是什么怎样对改进的数字锁相环进行仿真?

2021-04-20 06:47:12

数字锁相环频率合成系统的工作原理CPU控制数字锁相环频率合成系统FPGA实现

2021-04-09 06:20:37

小的做毕业设计遇到的瓶颈,我要设计一个实现位同步的电路,基带信号是1khz,载波是10khz,图中红线是基带信号,黄色的是我经过低通,微分,整流后出来的信号,现在我需要用一个锁相环实现窄带滤波器的功能,把黄色信号变成频率和基带信号1khz一样的位定时信号,该如何实现,求大神附图,感激不尽!!!

2013-05-16 17:26:46

最近在搞锁相环,总是有问题,功能无法实现,特求一个可以锁住输入信号频率为0.01~1Hz的数字锁相环程序参考参考,最好有注。参数达不到也没关系,我可以自己修改。谢谢大神们啦!

2016-08-28 17:33:56

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

请教一下大神锁相环是如何实现倍频的?

2023-04-24 10:15:39

数字锁相环的参考信号可以是正弦信号吗

2018-08-18 06:55:49

工程师您好:ADF4351内部集成VCO振荡器,如果结合外部环路滤波器和外部参考时钟频率能构成数字锁相环吗?如果不能是不是因为ADF4351内部没有鉴相器,如果我想做数字锁相环还要和ADF4002合用吗?能实现位同步吗?期待您们的答复!

2018-09-14 14:23:29

本帖最后由 gk320830 于 2015-3-7 16:40 编辑

高速数字锁相环的原理及应用

2012-08-17 10:47:04

智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字

2008-08-14 22:12:51 56

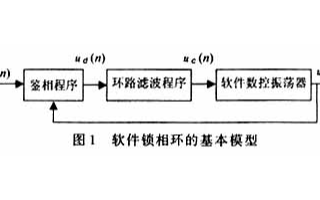

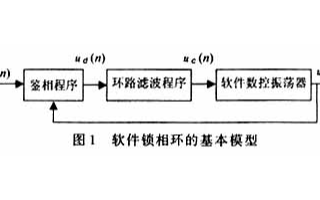

56 根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 101

101 一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 127

127 智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 72

72 基于FPGA的全数字锁相环设计:

2009-06-26 17:30:59 145

145 介绍了应用VHDL技术设计嵌入式全数字锁相环路的方法。详细叙述了其工作原理和设计思路,并用可编程逻辑器件FPCA予以实现。

2009-07-21 16:46:41 0

0 锁相环电路的设计:

2009-07-25 17:05:36 0

0 本文在介绍了经典全数字锁相环(all digital PLL, ADPLL)的基础上,提出了具有捕获锁定未知输入信号频率功能的ADPLL,使用方便,应用广泛。本文详尽的描述了系统的工作原理和关

2009-08-29 10:07:08 43

43 锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 30

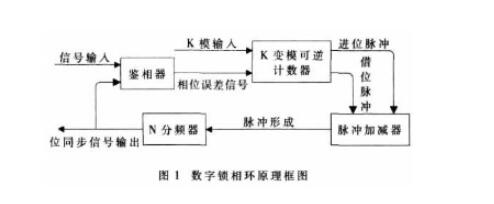

30 本文设计了一种在数字通信系统中的数字锁相位同步提取方案,详细介绍了本设计的位同步提取原理及其各个组成功能模块的VHDL语言实现,并在Quartus II开发平台上仿真验证通过。本

2010-08-06 14:28:08 64

64 本文在分析商用全数字锁相环的常用技术和低频信号的特点后,提出一种适用于低频信号的基于CPLD的锁相环实现方法。

2010-08-06 14:39:19 118

118 介绍了应用VHDL技术设计嵌入式全数字锁相环路的方法。详细描

2010-09-19 10:09:14 68

68 数字三相锁相环中含有大量乘法运算和三角函数运算,占用大量的硬件逻辑资源。为此,提出一种数字三相锁相环的优化实现方案,利用乘法模块复用和CORDIC算法实现三角函数运算

2010-09-30 16:35:54 35

35 锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进

2006-04-16 18:55:48 1974

1974 锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 5484

5484 锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 2529

2529

实验五 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27:45 6242

6242

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1760

1760

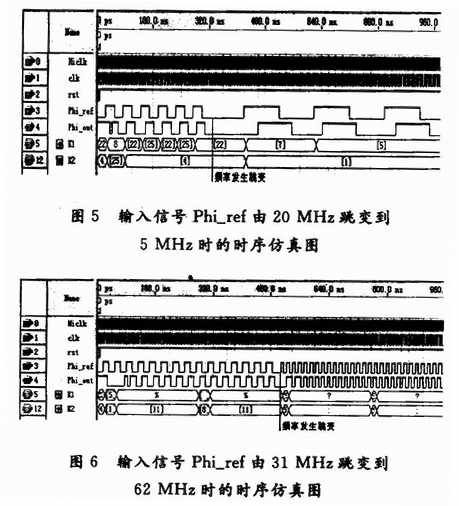

宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的

2009-11-23 21:00:58 1713

1713

锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6368

6368 数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 6110

6110 模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 6264

6264 本文鉴于 数字锁相环 在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。基于直接数字频率合成(

2011-08-05 14:51:05 79

79 针对扩频通信系统的载波同步,提出一套完善的数字锁相环设计方案. 该方案利用新颖的可控根法完成1~3阶模拟锁相环(APLL)环路参数设计,并实现从模拟域到数字域的转换,得到的数字锁相

2011-08-26 16:10:38 122

122 针对传统的全数字锁相环只能锁定已知信号和锁频范围较小的问题, 提出了一种自动变模控制的宽频带全数字锁相环。对比分析了各类全数字锁相环锁频、锁相的工作机理, 提出了一种新

2011-09-14 15:22:22 79

79 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

有关锁相环的部分资料,对制作锁相环有一定的帮助。

2015-10-29 14:16:55 70

70 基于FPGA的数字锁相环设计与实现技术论文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源码:用FPGA实现数字锁相环

2016-06-07 15:07:45 38

38 一种基于bang_bang鉴频鉴相器的全数字锁相环设计_陈原聪

2017-01-07 20:49:27 11

11 基于DSP的软件锁相环的实现

2017-06-22 09:54:06 70

70 一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 19

19 锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。因此,对全数字锁相环的研究和应用得

2017-11-24 20:03:04 14190

14190

直接影响到逆变器的性能。如何利用DSP等数字芯片,设计出一个可以克服各种电网畸变及故障的软件锁相环,是当今科学研究的热点问题。 本文首先论述的锁相环技术的发展历史及前景,简单阐述了传统的锁相环技术,指出了它们的缺点并

2017-12-08 11:12:07 25

25 一致的结果,从而消除反馈滞后一拍。所提出的锁相环仅以两个乘法器的额外开销即可大幅增强锁相环的稳定性,并且使在s域内设计的性能指标能够在z域内严格实现,克服了传统数字锁相环性能退化的问题。仿真和实验结果表明,所

2018-01-02 10:30:41 9

9 技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去,实现所谓片上系统SOC(System on a chip)。因此,可以把全数字锁相环路作为一个功能模块嵌入SOC,构成片内锁相环。下面介绍采用VHDL技术设计DPLL的一种方案。

2020-07-23 16:23:25 1784

1784

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 26

26 的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)。

2020-08-19 15:01:26 2777

2777

本文档的主要内容详细介绍的是使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载。

2020-11-02 17:15:00 77

77 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 66

66 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 20

20 为了提高全数字锁相环的系统运行速度、降低系统功耗,同时提高锁相系统的动态性能与稳态性能,提出一种基于流

2021-04-01 11:53:12 2635

2635

采用的锁相技术是基于数字信号处理技术在 DSP等通用可编程器件上的实现形式 ,由于这一类型锁相环的功能主要通过软件编程实现, 因此可将其称为软件锁相环 (software PLL )。

2021-05-28 10:44:35 34

34 基于FPGA的宽频带数字锁相环的设计与实现简介说明。

2021-06-01 09:41:14 26

26 基于FPGA的高性能全数字锁相环

2021-06-08 11:09:01 46

46 锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2022-07-03 15:23:57 2648

2648 锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2023-01-31 16:31:12 4097

4097 模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37:05 4645

4645

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 4879

4879 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 5119

5119 比较,通过不断调整内部振荡器的频率,使得输出信号的相位与参考信号的相位保持一致,从而实现同步。锁相环广泛应用于数字通信、音频解码、数字信号处理等领域。 在锁相环的基本结构中,包含一个相位检测器、一个积分环节、一个低通滤波器和一个控制振荡器。参考

2023-10-13 17:39:53 3088

3088 电子发烧友网站提供《应用于数字锁相环的NCO设计.pdf》资料免费下载

2023-10-26 10:33:45 1

1 锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环在各种不同的应用领域都有着广泛的应用,例如通信系统、控制系统、测量

2023-10-29 11:35:19 1738

1738 、无线通信、数据转换、模拟信号处理等众多应用领域。然而,频繁的开关PLL的电源可能对其造成不良影响。 PLL芯片是由多个模拟电路和数字电路组成的。在PLL芯片中,锁相环控制器是最重要的组成部分。这个控制器包含一个相位检测器

2023-10-30 10:16:40 1293

1293 为何不用一根导线代替锁相环? 锁相环(PLL)是一种广泛使用的电路,用于同步和追踪时钟和数据信号。它通常由一个锁相环振荡器(VCO)、一个相锁环(PLL)和一个数字控制器(DCO)组成。 PLL

2023-10-31 10:33:15 1057

1057 电子发烧友网站提供《基于VHDL的全数字锁相环的设计.pdf》资料免费下载

2023-11-10 09:47:34 0

0 在现代数字通信中, 数据传输中一个很重要的问题就是同步问题。而同步系统中的核心技 术就是锁相环。锁相环有模拟锁相环、模拟ö数字混合环、全数字锁相环等。前二种环路都要采 用压控振荡器V CO , 利用

2023-11-09 08:31:40 2

2 数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成

2024-01-02 17:20:25 3358

3358

电子发烧友App

电子发烧友App

评论