无论你是不是半导体行业的从业者,最近一个月内想必也被“国产化“、“芯片”等词冲洗了一波:

这是因为:受众所周知的原因影响,越来越多的人重视起了国产半导体产业链的发展;

简单的说,或许再过两年,就连街边唱《孤勇者》的小孩也将知晓光刻机的存在了。

当然,光刻机只是芯片制造中的一套关键设备,而一颗芯片的起源还是要从设计开始讲起:

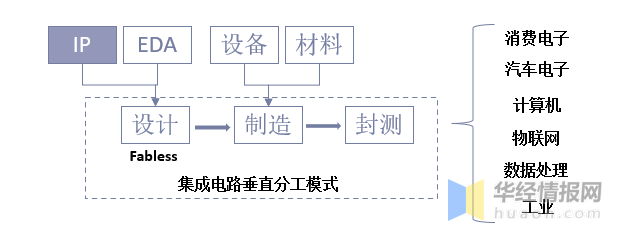

图片来自:华经产业研究院整理

图片来自:华经产业研究院整理

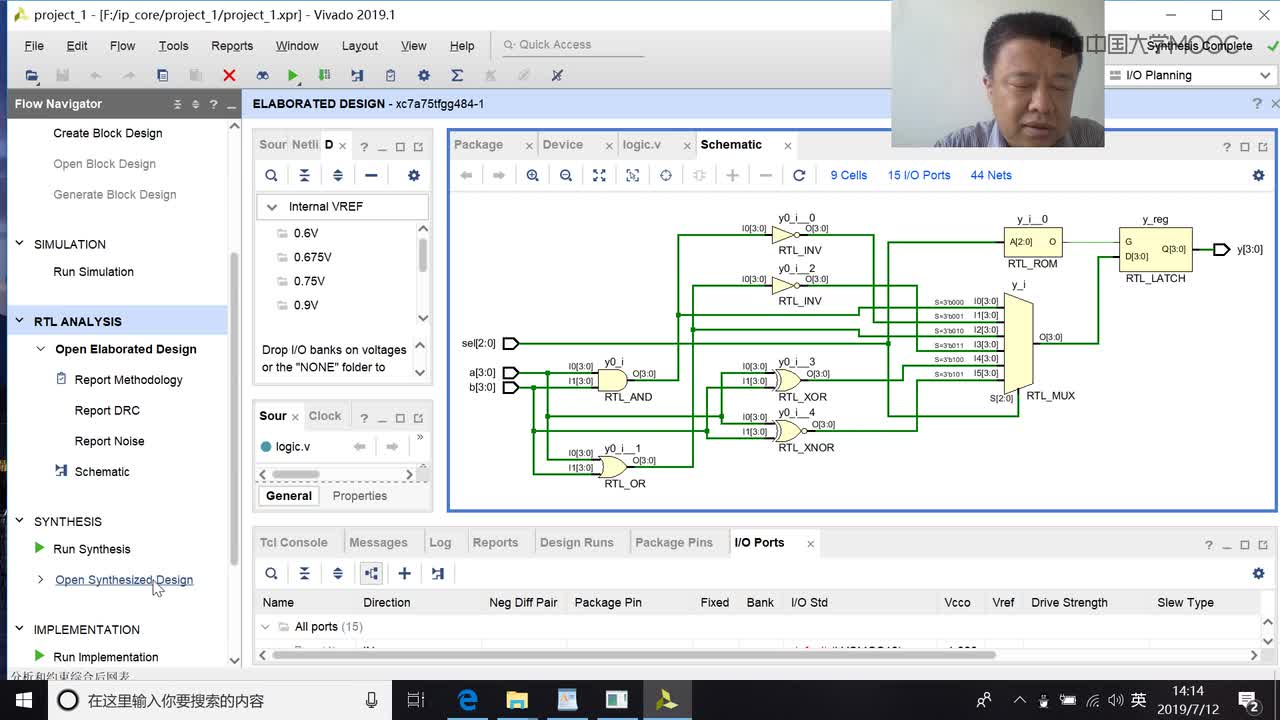

芯片的设计主要由EDA&IP核两个主要板块,它俩都是芯片设计的核心。

我们可以说:没有EDA,就没有芯片;它是最基础、最上游的领域,贯穿了半导体产业链的每个环节。

简单地说:EDA就是芯片设计师的画笔和画板,就像操作文档要用Word,制作图片要用Photoshop一样,它能高效设计、控制及管理数十亿电路元件在一颗芯片里协同工作。

而作为芯片设计核心之一的IP核:可谓是在芯片设计领域,其重要性不输芯片制造环节中的光刻机的存在。

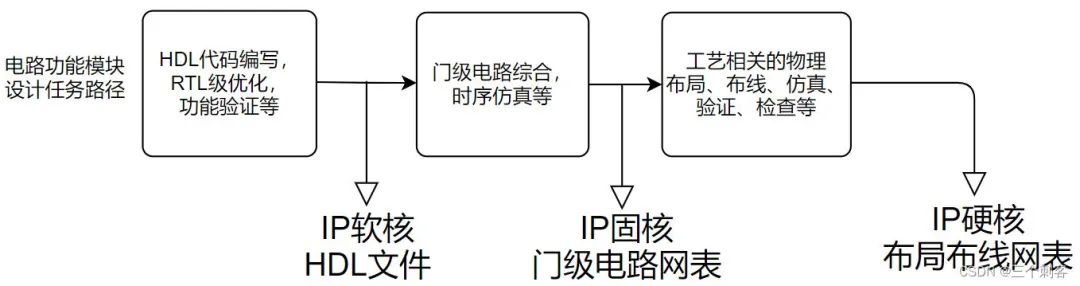

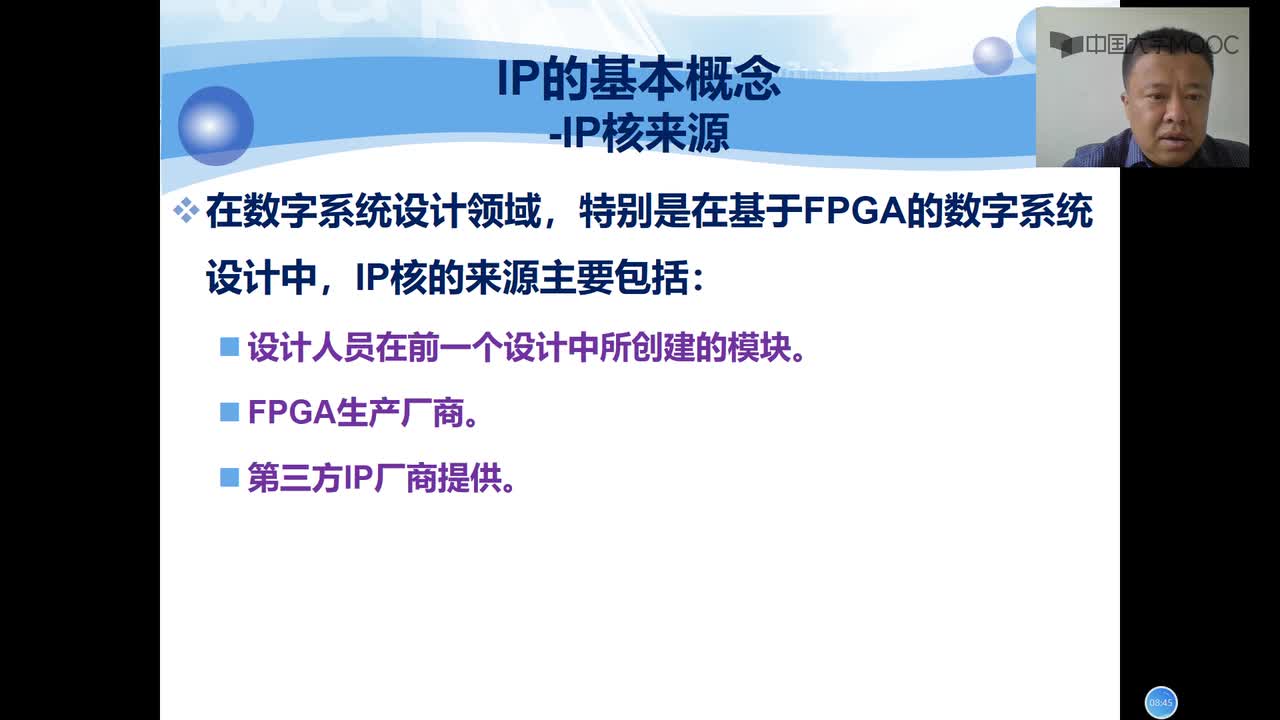

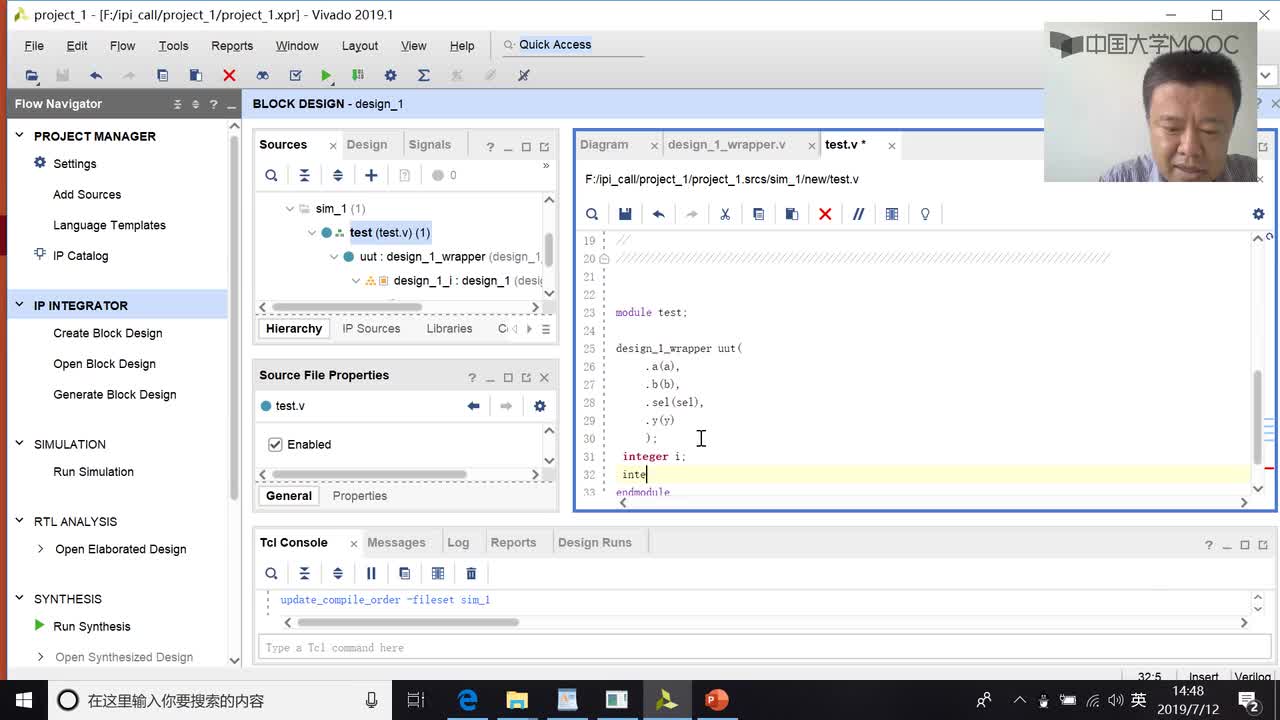

图片来自:三个刺客 IP核,(全称:Semiconductor intellectual property core,中文名全称:知识产权核);IP核是指芯片中具有独立功能的电路模块的成熟设计。 早期,芯片的集成规模较小,设计复杂度不高,芯片上所有的电路都可以由芯片设计者自主完成;随着芯片集成度呈指数级增加,复杂性急剧增大,由一家企业独立完成一款复杂芯片的设计几乎变得不可能。 聪明的芯片工程师们想到了借鉴搭积木的思路:重复使用预先设计好的成熟构件,来搭建复杂系统,化繁为简,以求一键成“芯”。

图片来自:三个刺客 IP核,(全称:Semiconductor intellectual property core,中文名全称:知识产权核);IP核是指芯片中具有独立功能的电路模块的成熟设计。 早期,芯片的集成规模较小,设计复杂度不高,芯片上所有的电路都可以由芯片设计者自主完成;随着芯片集成度呈指数级增加,复杂性急剧增大,由一家企业独立完成一款复杂芯片的设计几乎变得不可能。 聪明的芯片工程师们想到了借鉴搭积木的思路:重复使用预先设计好的成熟构件,来搭建复杂系统,化繁为简,以求一键成“芯”。

IP 核按照固化程度划分,可以分为软核、固核与硬核三类:

IP软核:是用 Verilog/VHDL等硬件描述语言描述的功能块,如逻辑描述;它可沿用 Excel 的类比,IP 软核即为该图表模板的底层开发代码。

IP 固核:是以电路元件实现的功能模块。因为有一定的功耗约束、温度条件等,用户能够设置IP软核中的相应参数,将其转换成用逻辑门和触发器达成的电路,通常以门级电路网表的形式提供给客户。IP 固核可以看作是将底层代码中图表设置为部分固定的多个参数,并生成相应简单模板。

IP 硬核:与制造工艺相关(例如 CMOS 工艺),完成了布局布线,提供电路设计的最终阶段产品—掩膜,进而进行光刻,生产芯片颗粒。简单的理解IP硬核就是IP 硬核就是完全设定好的某一Excel图表模板,能够重复使用,能实现特定功能。

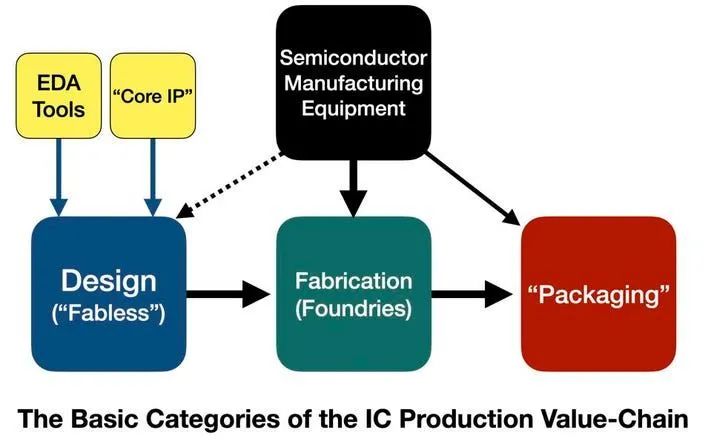

众所周知,半导体产业的发展经历了一个不断分工细化、上下游联动发展的过程;而,IP核的出现则让芯片设计和芯片代工从IDM模式中独立,成为芯片产业中的独立行业。

图片来自:半导体产业结构

图片来自:半导体产业结构

时至今日,无论是传统的芯片设计公司(Fabless)+芯片代工(FAB)模式,或是已经成为当今主流的芯片设计公司(Fabless)-材料设备-芯片代工(FAB)-封装公司-终端客户的模式中以IP核作为其核心竞争力的芯片设计公司的地位尤为凸显:

我们身边耳熟能详的电子品牌英伟达、AMD、华为海思、苹果、高通等,现如今都是纯设计公司。

给这些设计公司提供架构和IP核的,则是Arm、Synopsys、Cadence等公司;其中Arm的市场占有率更是高达40%。

对于整个半导体产业链而言:IP核的出现及有效利用,势必会助力于半导体产业未来市场的正向增长:

IP核主要用于缩短芯片上市时间以及降低芯片开发成本,ARM的IP核生态可将芯片开发成本降低50%以上。

特别是对于它们而言:IP核的出现极大的降低了研发成本和研发风险,以风险共担、利益共享的模式形成了一个个小的以处理器内核为核心的生态圈,使得低成本创新成为可能。

并且在未来模块化设计趋势、产品协议迭代以及功能集成增加的推动下,IP需求将得到持续支撑,同时Chiplet 行业趋势亦有望为IP 行业带来新增量。

又对于设计公司自身而言:在芯片设计的上游供应链中,IP是技术含量最高的的价值节点。

根据lPnest数据统计,在年均600多亿美元的全球芯片研发开支中,IP只占36亿美元,虽然占比只有5%,但从市场价值来看,IP的全球市场规模大约40亿美元,却带领着5000亿美元的半导体产业不断向前发展。

特别是相关的EDA厂商同为产业链上游玩家,其产品商业模式与IP 较为相似,且面对客户类型相同,故EDA 与IP 业务之间存在协同效应,EDA 公司切入IP 行业将具备天然优势。

综上所述,我们应该可以看出:我国未来想要走上半导体产业链的自主化道路,IP核的重要性丝毫不弱于光刻机!

图片来自:粤开证券研究所

图片来自:粤开证券研究所

国内代工厂以及芯片设计行业快速发展,芯片设计公司以及总销售额快速增长,也将推动对IP核的相应需求:

从行业下游领域来看:AI 应用的拓宽,以及汽车智能化趋势需要新的IP 对产品进行适配,这也将产生额外的IP 需求,中国是AI 应用和汽车智能化的主要市场,国内企业有望借力下游领域快速发展,迎来发展良机。

同时,国内半导体行业的蓬勃发展带动了设计服务和芯片定制化行业发展,而设计服务等有业务又有望驱动国产IP 需求,部分国内IP 公司采用设计服务和IP 授权双轮驱动的发展战略。

当然,国产IP 发展离不开半导体产业生态的支持,近年来国内代工厂崛起,有望培育和带动国产IP 生态链的发展。

特别是对于被国内半导体产业链寄予厚望的Chiplet技术而言:国内IP核的自主研发无外乎是为Chiplet技术在拓宽“捷径”。

从这个意义上来说,Chiplet就是一个新的IP重用模式;未来,以Chiplet模式集成的芯片会是一个“超级”异构系统,可以带来更多的灵活性和新的机会。

与传统芯片设计方式相比,Chiplet具有迭代周期快,成本低,良率高等一系列优越特性。随着Chiplet技术的兴起,有望使芯片设计进一步简化为IP核堆积木式的组合,半导体制造链生态链可能会重构。

或许,在未来在国产化IP核加持下的Chiplet生态,可能带来的一场新的半导体产业革命:

以计算芯片为例:Chiplet主要涉及计算、内存和IO接口,IO接口相对独立,计算最难和上层算法解耦,内存可以部分解耦;最终Chiplet会像搭乐高积木一样,通过取舍提高客户的迭代速度。

这将导致:一个Chiplet生态的第三方公司,直接从客户需求出发,“化繁为简”直接从设计到封装都可以直接帮客户定义。

编辑:黄飞

电子发烧友App

电子发烧友App

评论