作为芯片行业从业者,估计很多人最怕听到的就是一些话是:芯片“可靠性”出问题了。对于5G射频芯片,评估基本性能都已经非常复杂,出了“可靠性”问题更是会让人胆战心惊。

如果“可靠性”评估不彻底,器件在终端使用中出现失效,则会影响产品功能,严重时可能造成不可挽回的惨痛后果。

但如果对“可靠性”的评估不科学,层层加码、过度苛责,又会严重影响项目进度,使成本、时间急剧上升。

为了科学的解释和评估电子元器件的可靠性,伴随着1947年半导体晶体管的发明和大规模应用,逐渐兴起了一个学科:可靠性工程。

可靠性工程是提高元器件在整个生命周期内可靠性的一门工程技术学科,涉及设计、分析、试验等各个产品开发过程。可靠性工程于1950年前后在美国兴起,伴随着半导体技术的进步,已经发展了70年。本文借可靠性工程的相关理念和方法,和大家就芯片的可靠性设计与评估理念做一个讨论。

可靠性工程中的几个重要理念

失效时间:性能退化是基本物理规律

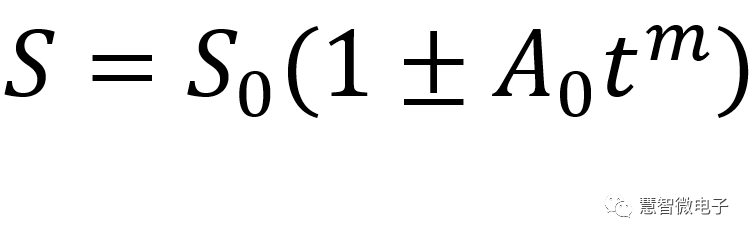

正如人有生老病死,自然界中物体的特性也会逐渐退化。这也符合热力学第二定律,熵增定律的表现:孤立不可逆系统的熵(无序程度),会随着时间增加而增加。 既然每个期间都会性能退化,那器件可以使用的时间究竟是多少呢?于是,失效时间(Timeto Failure,TF)的概念就被引入了进来。 在可靠性工程中,认为器件参数S是与时间t相关的函数。性能参数S与初始性能S0、时间t的关系,可以用级数的方式表示出来(m为幂律指数):

通过以上公式可以看到,参数S会随时间变化而变化,变大与变小受正负号控制,变化的幅度受A0控制。 当器件参数S随时间变化而减小时,假设可以在不同时间将器件参数均采集出来,就可以得到以下器件参数S随时间变化的曲线:

图:器件参数S随时间变化而减小

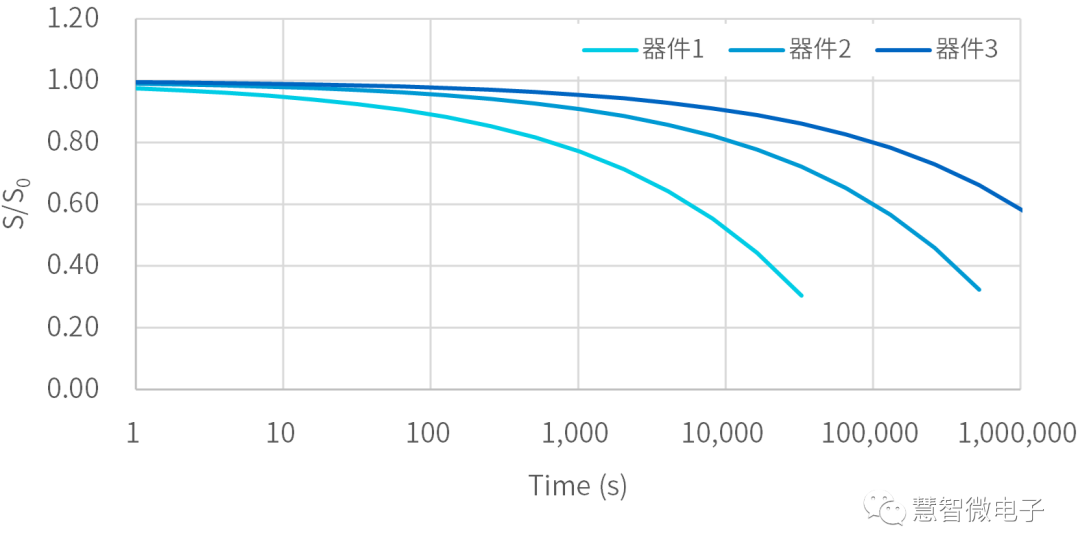

得到以上参数后,如果将S变化原有值的80%作为临界值,就可以得到不同器件失效时对应的时间。这个时间就定位为失效时间(Time to Failure,TF)。

图:器件失效时间(TF)的定义

加速退化:可控时间内测试出器件寿命

如前节所述,器件性能的退化是随时间演进而发生的。对于消费类产品来说,一般生命周期长达数年。在产品推出来之前,先做完整个生命周期的可靠性验证是不现实的,更不用说一些工业级、车规级的芯片需要10年以上的可靠性寿命。 于是,加速退化的概念就被引入进来。 加速退化(Accelerated Degradation)是指通过提高器件测试条件的应力、或者升高湿度,来加快器件退化的过程。其目的是在不改变失效发生物理机理情况下,缩短失效测试的周期。

加速因子:确定加速的速度

加速测试确实可大大减少可靠性测试所需要的时间,但究竟可以加速到多快呢?加速需要采用的测试条件应力、温度与加速时间之间又是什么关系?这里就有了加速因子的概念。

加速因子(Accelerated Factor)是加速测试理论中的重要概念,是指在加速应力条件下快速采集器件失效时间数据,并将这些数据外推到器件正常使用环境,得到正常使用下的失效时间。 需要说明的是,采用加速模型进行加速老化实验时,一定要确保两点:

加速必须是均匀的

不能改变失效的物理机制

第一点中,加速均匀性的要求是加速模型计算中的需求。第二点“不能改变失效物理机制”同样需要注意,需要确保不因为参数应力过大,而出现其他失效问题(如瞬间失效烧毁等)。 设计合理的加速测试环境需要对器件的失效机理有着深入的分析。在集成电路产品中,典型的失效机理包含[2]:

电迁移

应力迁移

腐蚀

热循环疲劳

时间相关介电击穿

热载流子注入

离子键断裂

加速测试方法需要根据以上失效机理进行合适设计。

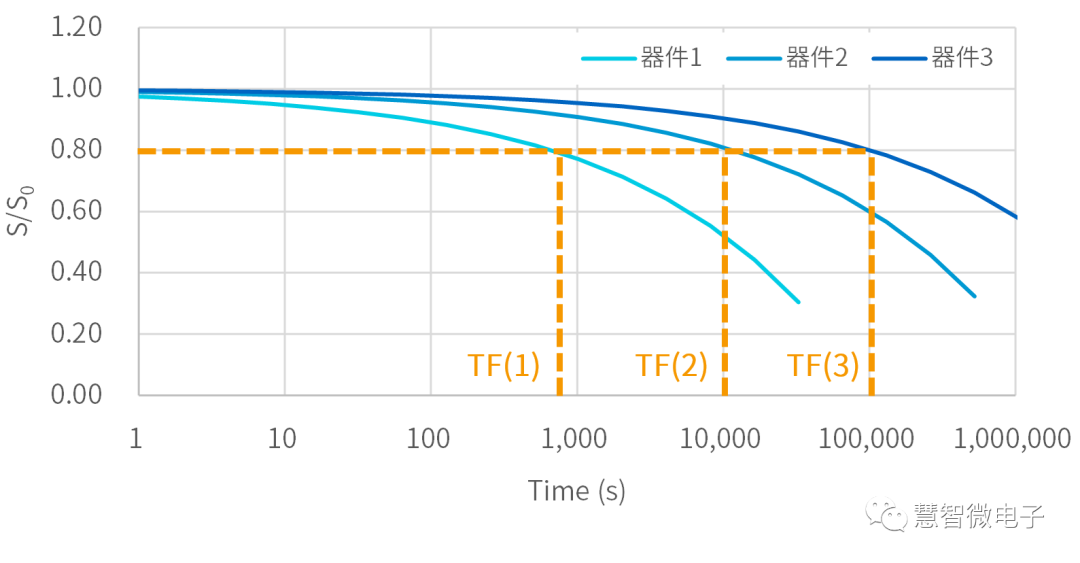

常见的加速退化方法

加速因子与加速时间有对应关系是较为容易理解的,但要精准推导出二者的数学联系就较为复杂了。 于是,行业组织这时就发挥出了较大的作用。 1958年,由半导体器件制造厂商、设计厂商以及终端应用厂商等,共同成立了行业标准制定组织JEDEC(Joint Electron Device EngineeringCouncil,联合电子器件委员会),用于制定统一的产业标准制定。 根据器件的老化机理,JEDEC定义了系列的加速测试方法。常见的加速测试方法如下。

图:常见的加速测试方法

JEDEC所定义的加速测试方法已成为电子器件的标准测试方法。在实际产品交付中,需要将以上可靠性报告,伴随产品一起向客户交付。

浴盆曲线模型:将失效分时期看待

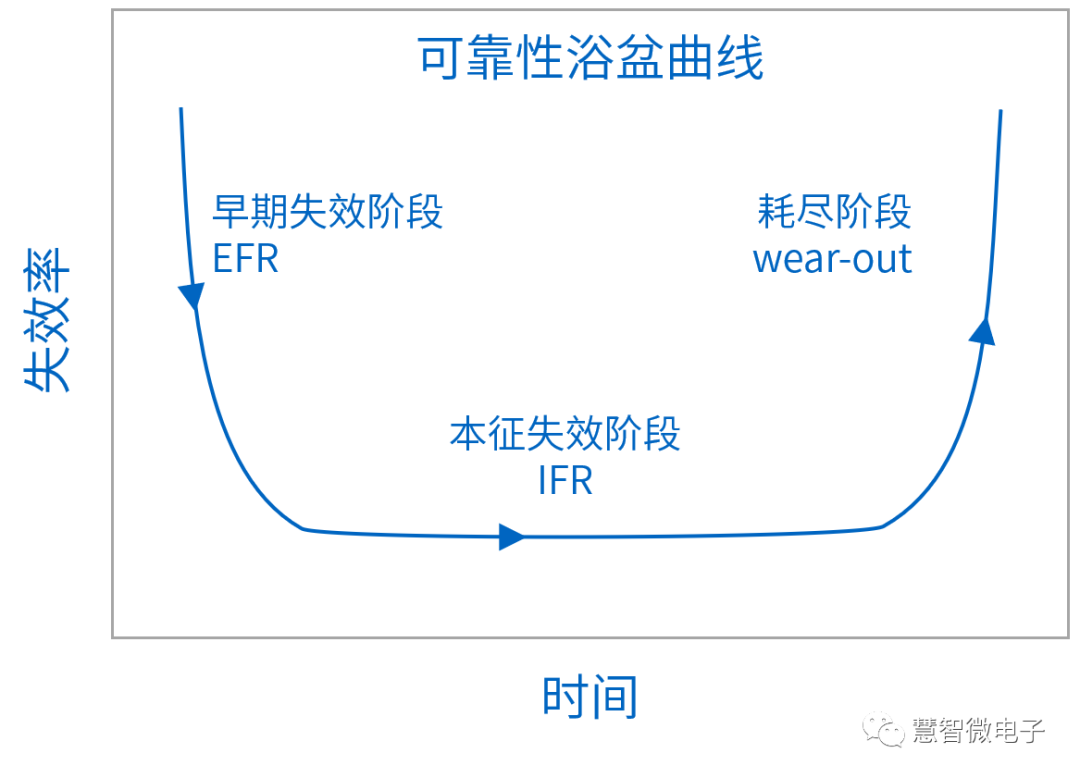

为了理解不同时期内器件失效发生的物理机理,可靠性工程中引入著名的“浴盆曲线”概念。 浴盆曲线(Bathtub Curve)认为一般器件失效有三个明显不同的阶段:

早夭期(Early Failure Rate,EFR):在器件早期使用阶段发生,失效率较高。这个时期主要的失效原因是器件生产时的严重缺陷造成;

本征失效期(Intrinsic FailureRate,IFR):这个阶段是由于器件内部材料内部存在微小缺陷造成的;

耗尽期(Wear-out):这个阶段器件的性能已经退化,达到使用的末期。此时失效由于器件的正常退化造成。

图:可靠性浴盆曲线

可靠性浴盆曲线反应了失效的一般规律,甚至可以用生物的生命周期来类比:一般新生儿在出生的24小时内,需要医生格外关注,如果新生儿有一些出生时的缺陷,则在这个时期很容易出现生命危险;而经过一年之后一直到70岁左右,这个时期内死亡率较低并且趋于平缓;而到70岁之后,人类的器官开始出现消耗殆尽的现象。 对于集成电路来说,早夭期(EFR)可能会延续一年的时间。为了剔除存在缺陷的产品,使之不至于流向客户造成高的失效率,集成电路会采用让产品试运行一段时间,来清除有先天缺陷产品,这个清除的过程,被称为Burn-in(老化)。 将器件做长达一年的Burn-in是不现实的。所以,一般会用到前一节提到的“加速退化”的方法,提升器件工作时的电压或其他工作条件的应力,使失效时间缩短到几小时、几分钟,甚至几秒钟。与加速退化的分析类似,具体所加应力大小与对应时间的关系,需要根据器件的失效各类来确定。 Burn-in是一种对产出产品进行100%筛选的非破坏性实验,目的是将早夭产品剔除。由于实验对应芯片工作的时长是早期失效阶段(比如一年正常工作时间),所以并没有使器件进入耗尽期而发生性能的退化失效,也不会明显减少器件使用寿命(器件的寿命通常为数年)。 另外需要说明的是,Burn-in是减少早期失效的一种方式,需要在每颗产品出厂前进行全数测试。如果工艺和设计电路成熟,有数据表明器件早期失效率稳定,也可以在测试中去掉Burn-in的测试。

统计概念的引入:评估性能波动的影响

失效时间定义了器件性能随时间的变化。在大批量使用时,还会存在不同器件间性能波动的问题。

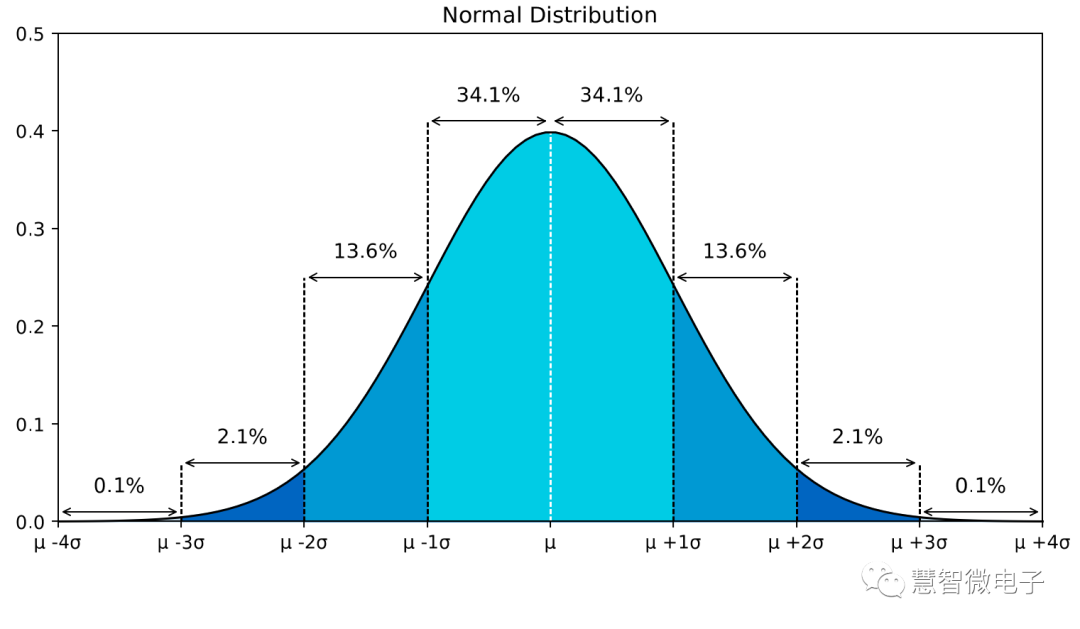

既然不同器件之间的性能是不完全一致的,那如何衡量波动和确定卡控门限(Limit)呢?于是,统计的概念就被引入了进来。 正态分布(Normal Distribution)是数学家们在18世纪所发现的一种统计规律,著名高斯在1809年对其进行了理论推导与完善,所以正态分布又被称为高斯分布。 正态分布的作用不止是揭示了一个数学现象,而是在实际工程应用中有着重要的作用。

图:正态分布及其对应区间的概率

正态分布中两个重要参数是均值和标准差。均值决定了数据的平均数,标准差决定了数据的分散程度。在正态分布中:

68%的数据在平均值1个标准差内;

95%的数据在平均值2个标准差内;

99.7%的数据在平均值3个标准差内

一旦根据统计分布得出某一变量的均值和标准差后,就可以根据高斯分布,计算出任意给定区间内的概率分布。所以,此种统计的方法可以用来计算给定上下限的良率,或者推测性能波动带来的ppm失效率。

高可靠性芯片的设计和评估

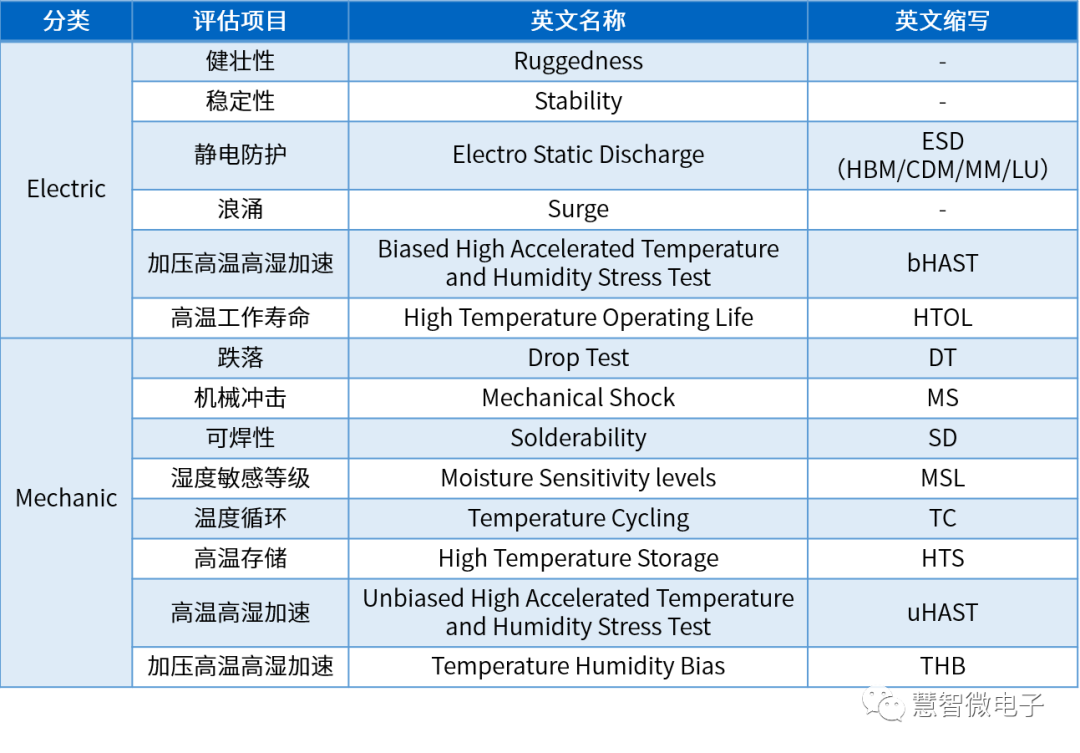

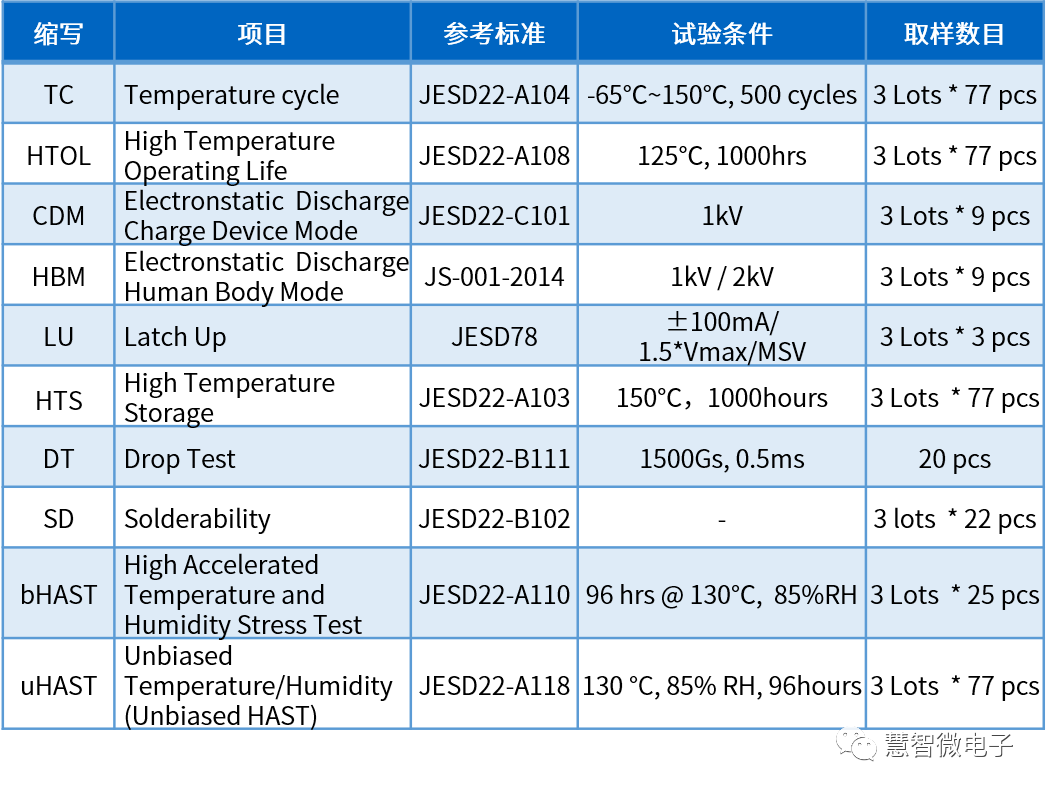

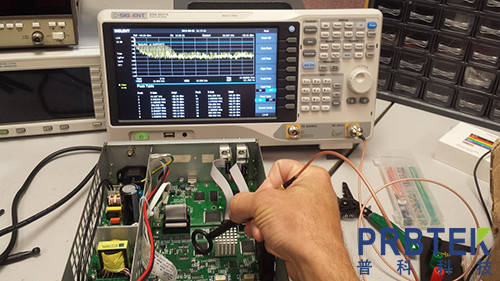

基于以上可靠性工程理念,在芯片产品开发过程中加入高可靠性设计与评估。 根据芯片是否带电测试,芯片的可靠性主要分为Electric类与Mechanic类两类。射频前端产品常见的可靠性测试内容如下。

图:常见的可靠性测试项目

以上可靠性测试项根据产品的不同需求,选择进行评估。部分测试目的相同的测试项(如THB与bHAST),可以二选一进行测试。

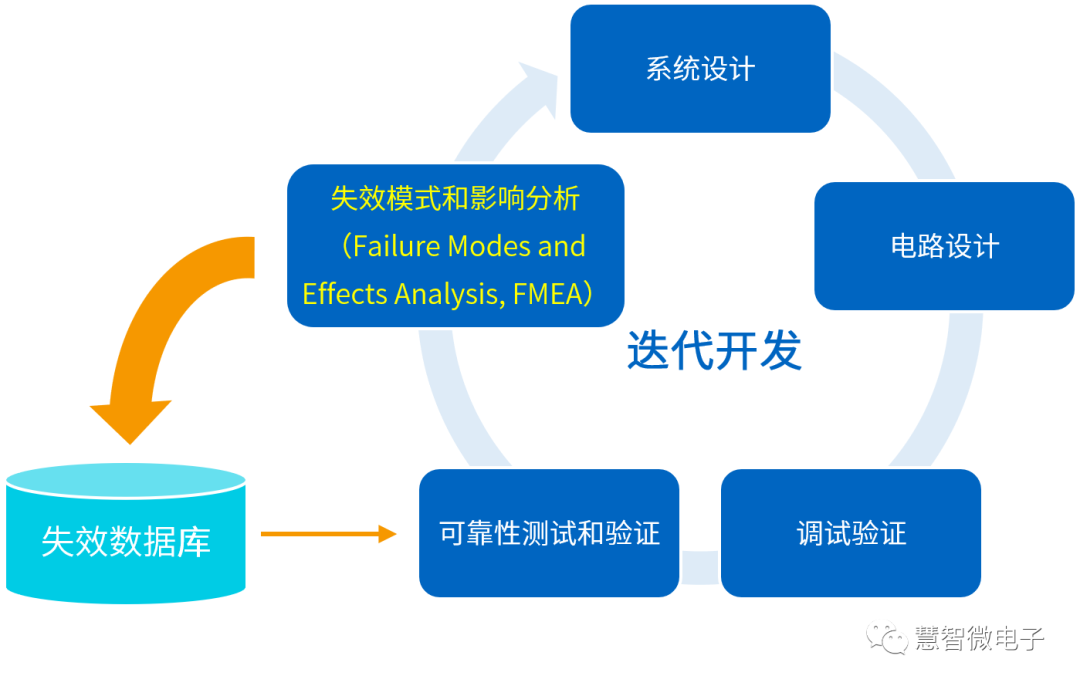

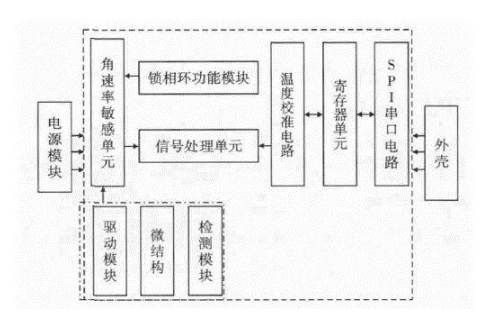

高可靠芯片的设计

“可靠性是设计出来的,不是测试出来的”是高可靠芯片设计中的重要理念。实现满足以上可靠性需求的高可靠模组芯片,必须要在设计之初就对芯片的高可靠性加以考虑。 常见的高可靠性芯片设计思路是FMEA(FailureModes and Effects Analysis)方法,下图为典型的包含FMEA的迭代开发流程。

图:包含FMEA的迭代开发流程

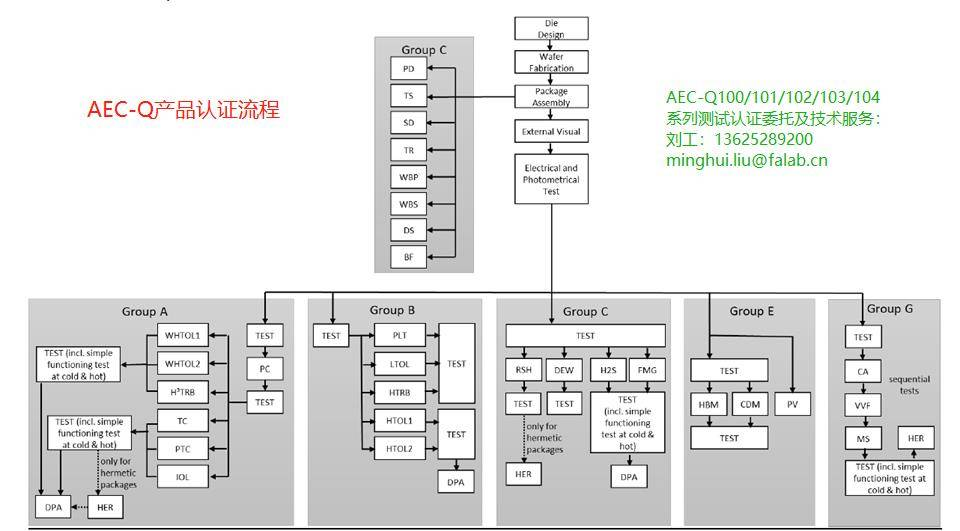

高可靠芯片的验证

芯片的可靠性验证一般遵循一定的测试标准,常见的测试标准为前一章节提到的JEDEC标准,另外还有车规产品验证的AEC-Q系列标准。 这些标准中建立起标准的测试方法。同时,在器件选取数量、判定标准上也做了明确规定。如下为JEDEC相关测试项及测试标准。高可靠的芯片设计必须完全通过以下测试。

图:JEDEC所规定的测试项及条件(部分)

总 结

高质量芯片是先进的设计能力、优质的流程管理、完整的可靠性评估带来的综合结果。开发高质量芯片,对设计企业的综合能力和开发投入提出了高的要求。

[1].章晓文等, 2015, 半导体集成电路的可靠性及评价方法

[2].姚立真,2004,可靠性物理

[3].J. W. McPherson, 2019, ReliabilityPhysics and Engineering

[4].https://www.jedec.org/

编辑:黄飞

电子发烧友App

电子发烧友App

评论