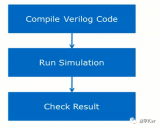

下图是一个典型的EDA仿真验证环境,其中主要的组件就是激励生成、检查和覆盖率收集。

2023-04-13 09:27:33 1440

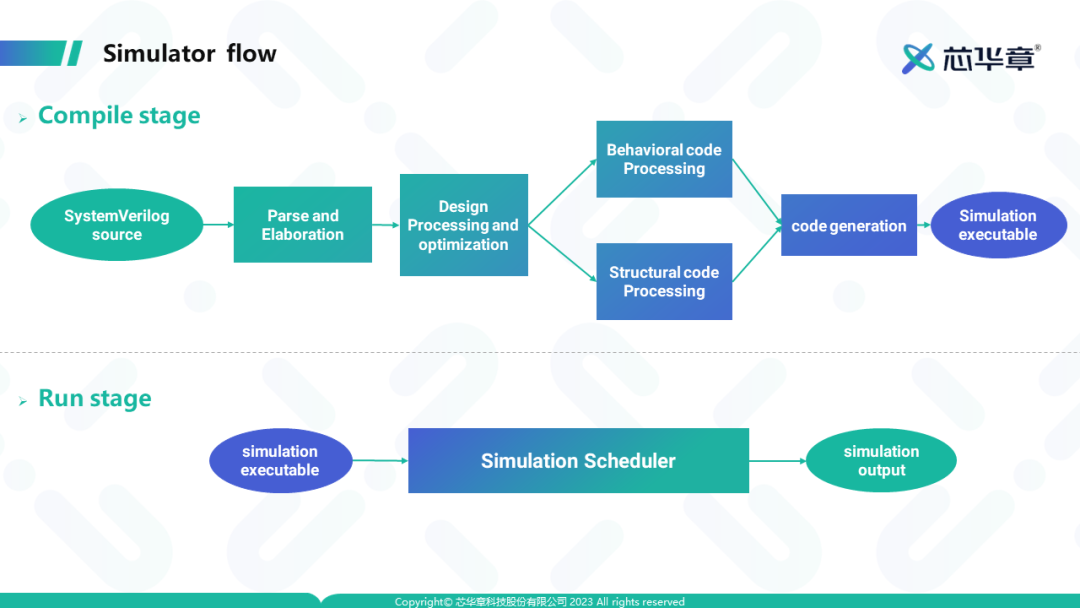

1440 VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-10-25 17:22:28 491

491

EDA仿真与虚拟仪器技术

2020-03-06 16:06:40

EDA仿真怎么回事? 没看到有仿真界面??????

2017-09-06 23:34:23

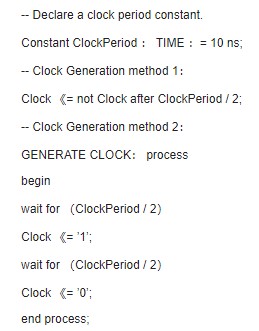

VCS是Synopsys公司的数字逻辑仿真工具,DVE是一个图形界面,便于调试RTL代码,查看波形。本视频简要介绍VCS的常用概念。 欢迎大家加入启芯SoC QQ群: 275855756。共同交流和学习SoC芯片设计技术。

2013-10-04 13:07:00

在make com编译成功后,terminal卡住了一直没有反应,这是什么情况有大佬知道吗?VCS仿真卡住,为什么无法生成verdi波形文件呢?

2021-06-21 08:14:57

VCS-verilog compiled simulator是synopsys公司的产品.其仿真速度相当快,而且支持多种调用方式;使用的步骤和modelsim类似,都要先做编译,再调用仿真.Vcs

2011-12-15 10:27:10

是把xilinx含有RAMB的仿真库添加进VCS compile,并且库中的RAMB也是有INIT的,但是vcs结果好像对INIT不敏感,即使我把INIT值改成别的,vcs也是正确的 {:10:}向各楼求助,如果vcs的确对RAMB的INIT初值不敏感,还有什么办法可以验证的,谢谢!

2015-03-05 11:22:05

本帖最后由 eehome 于 2013-1-5 10:08 编辑

Xilinx Fpga前仿真后仿真

2012-08-17 08:50:07

Xilinx Fpga前仿真后仿真

2012-08-15 18:49:38

,几次出现the design unit was not found,modelsim已经编译好xilinx的仿真文件了,不知道为什么还出现这样的错误,请大家讨论下。

2016-01-21 10:12:40

在FPGA开发过程中需要利用Modelsim对设计进行仿真,在不同阶段需要用到不同的库文件,这里把Xinlinx库文件的编译过程说一下。常用有三个库xinlixcorelib,unisims

2012-02-27 15:16:55

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

ATK-USB Blaster仿真器 BURNER 5V

2023-03-28 13:05:53

编译好,可以提高仿真效率,下面整理了Altera 和Xilinx器件需要的库,希望能方便大家使用。如何建立仿真库请查阅其他资料,

2012-08-10 18:31:02

DAP仿真器 BURNER

2023-03-28 13:06:20

设计中用到了GTP_DUAL,利用questasim仿真。Simulation时报错,说找不到GTP_DUAL_fast.v这个文件。在xilinx的安装目录下mti文件中搜索到

2016-08-30 16:04:52

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

VHDL特点是什么VHDL语言在EDA仿真中的应用

2021-04-29 06:01:15

所用Linux系统为openSUSE64位,软件为VCS2012在Linux下对verilogHDL进行功能仿真时非常必要的,下面提供两种常见方式。1.脚本方式1)建立工作文件夹pre_sim,并将

2019-07-09 08:10:24

nanosim和vcs为什么可以联合起来进行数字模拟混合仿真?nanosim和vcs混合仿真的过程是怎样的?

2021-06-18 08:28:30

分析电路结构,通过电路仿真得到准确的非连续模式S参数。这些EDA仿真软件与电磁场的数值解法密切相关的,不同的仿真软件是根据不同的数值分析方法来进行仿真的。通常,数值解法分为显示和隐示算法,隐示算法(包括

2019-07-30 07:27:53

怎样通过Makefile脚本进行编译和仿真?Makefile脚本是如何简化VCS中仿真设计的?

2021-06-18 10:03:17

请教大神,我在Linux上用vcs+verdi对demo_nice进行仿真,但是没有成功

我是用hibrd.sdk把demo_nice编译成.verilog文件的,其内容如下

另外我还对tb

2023-08-12 08:07:30

在ModelSim中添加xilinx仿真库的具体步骤

2018-09-12 14:58:15

代码如下:顶层模块代码:波特率产生模块接收模块代码:发送数据模块一、VCS仿真下面开始进行VCS仿真。VCS要使用图形化界面,必须得先编译得到vpd文件,才能用图形化界面看波形。首先是编译verilog

2022-07-18 16:18:48

先编译Xilinx的仿真库,否则就会产生无法加载simprim,unisim等库文件的错误。在许多论坛上都提到了使用compxlib命令来编译Xilinx的仿真库,如使用compxlib -s

2012-02-24 21:40:17

仿真技术去分析电路结构,通过电路仿真得到准确的非连续模式S参数。这些EDA仿真软件与电磁场的数值解法密切相关的,不同的仿真软件是根据不同的数值分析方法来进行仿真的。通常,数值解法分为显示和隐示算法,隐示

2019-06-27 07:06:05

,通过电路仿真得到准确的非连续模式S参数。这些EDA仿真软件与电磁场的数值解法密切相关的,不同的仿真软件是根据不同的数值分析方法来进行仿真的。通常,数值解法分为显示和隐示算法,隐示算法(包括所有的频域

2019-06-19 07:13:37

基于矩量法仿真的微波EDA仿真软件基于时域有限差分的微波仿真软件基于有限元的微波EDA仿真软件

2021-05-25 06:19:18

用VCS仿真没问题,用vivado仿真时添加rtl时就出现错误;

出错在rtl里断言语法上(assert property),这会导致编译不通过;该如何解决?

2023-08-16 07:47:06

VCS有哪几种调试模式?萌新求助关于VCS仿真指南

2021-04-29 06:52:26

请问VCS+HSIM混合仿真怎么提速,实在跑的太慢了

2021-06-25 07:09:49

仿真工具的使用方法,它们是Modelsim,VCS和NCsim,分别是Mentor,Synoposys和Cadence的产品。这也是XILINX提供这些工具的原型库,以及技术支持。不过如果需要仿真

2013-03-14 11:49:58

高速DAP仿真器 BURNER

2023-03-28 13:06:20

基于公共数据结构的EDA仿真波形分析技术:现有的EDA仿真工具缺乏对仿真数据的分析处理功能,影响了仿真分析的效率。本文提出一种基于公共波形数据结构的仿真波形自动分析技

2009-10-23 16:49:51 21

21 电基于公共数据结构的EDA仿真波形分析技术

摘要: 现有的EDA仿真工具缺乏对仿真数据的分析处理功能,影响了仿真分析的效率。本文提出一种基于公共波形数

2009-12-07 13:54:16 12

12 应用EDA 技术仿真电子线路分析

摘 要 介绍了电子电路仿真软件Elect ronicsWo rkbench 在EDA 中的应用, 给出了仿真实例, 并结合实例介绍了该软件对电子线路进行仿

2009-12-07 13:59:39 0

0 摘要:本文通过几个实例来介绍如何用EDA(Electronics Design Automation)软件Multisim进行三相电路特性仿真实验的方法。关键词:EDA软件;Multisim;

2010-04-13 22:23:05 121

121 应用EDA技术仿真电子线路摘要开拓了电子电路仿真软件Elect ronjcsWorkbench 4KEDA 中的应用,培出了仿真实例t井结合实例舟绍了谊软件对电子线路进行仿真的方法,给

2010-05-14 17:29:53 11

11 摘要:介绍了电子电路仿真软件Electronjcs Workbench 在EDA中的应用,培出了仿真实例,并结合实例介绍了该软件对电子线路进行仿真的方法,给出的仿真结果表明该软件应用于电子线路

2010-05-20 11:32:11 73

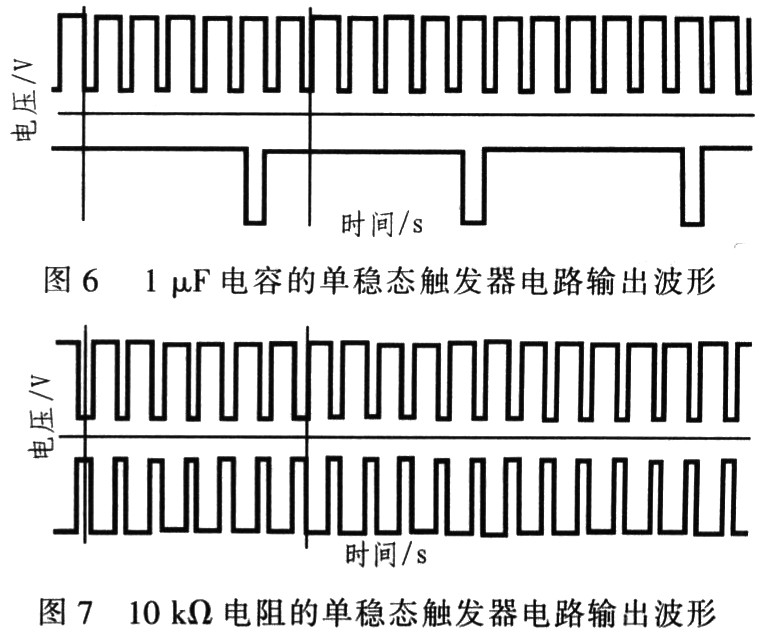

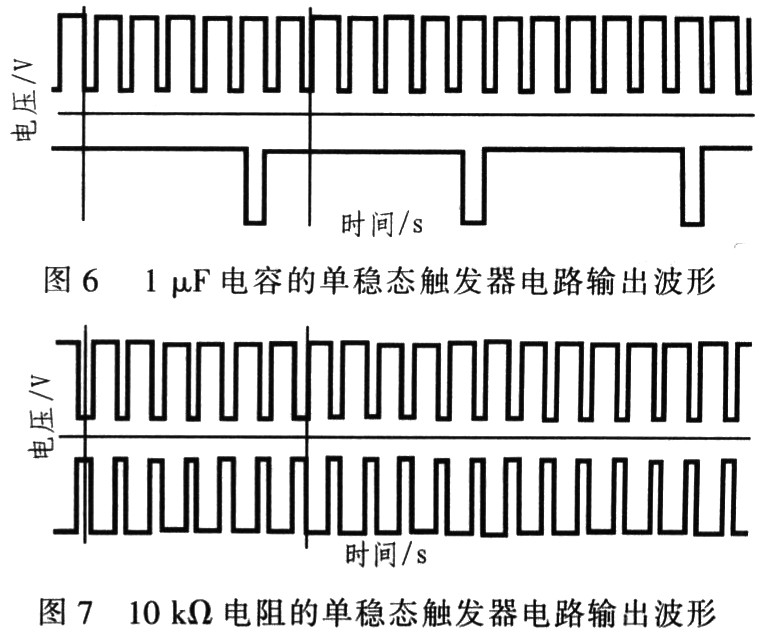

73 基于EDA技术的555单稳态触发器设计与仿真

当前电子线路已大量采用计算机辅助仿真设计,尤其是电子设计EDA仿真技术。EDA仿真软件中Electronics Workbench仿真设计分析软件

2009-10-23 08:50:05 1621

1621

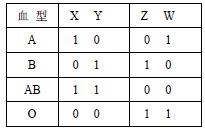

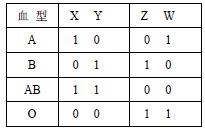

译码器及多路选择器的使用( EDA 仿真) 实验

一、实验目的1. 掌握Multisim电子电路仿真软件的使用,并能进行

2010-02-06 14:11:30 5856

5856

VCS-verilog compiled simulator是synopsys公司的产品.其仿真速度相当快,而且支持多种调用方式;使用的步骤和modelsim类似,都要先做

2010-10-09 16:59:08 5110

5110 Power Expert是一套可以支持Xilinx FPGA设计的最新设计工具,设计数字系统的工程师只要利用这套工具,便可解决仿真电路的设计问题。这个设计工具网页详列Xilinx各种不同的FPGA产品以供工程师挑

2011-03-16 14:48:58 137

137 电子发烧友网站提供《EDA_Proteus_HA_proteuse仿真软件.rar》资料免费下载

2013-01-10 13:27:10 45

45 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 SST89E516仿真芯片的仿真操作步骤.SST89E516仿真芯片的仿真操作步骤-

2015-12-28 14:25:34 0

0 我们经常使用Xilinx Ise与Modelsim联合仿真,但是经常出现一些由于库没有编译而出现的错误!下面是我总结的方法:

2017-02-11 13:43:06 1348

1348

当ISE调用ModelSim进行仿真的时候,如果在FPGA设计中使用了Xilinx提供的的IP core或者其他的原语语句,ModelSim不添加Xilinx相应的库文件的话,是无法仿真的。

2017-02-11 15:22:37 1274

1274

在我们用ModelSim仿真的时候经常是修改一点一点修改代码,这样会造成一个无奈的操作循环:修改代码--->编译代码--->仿真设置--->进入仿真页面--->添加需要观察的波形--->运行仿真

2017-02-11 15:25:07 10139

10139

allegro的PI仿真电源平面完整性的操作步骤解析

2017-03-14 15:50:06 49

49 VCS-MX的版本,可以混合编译Verilog和VHDL语言 由于在linux系统中个人用户各种权限被限制,导致很多地方无法正常使用软件之间的协调工作。 为了以防万一,在此以个人用户去实现vivado调用VCS仿真。

2018-07-05 03:30:00 10733

10733

STM32编译开发环境及仿真调试篇-----野马学习笔记

2017-10-27 09:13:44 26

26 modelsim仿真详细过程(功能仿真与时序仿真).ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括创建工程、编写源代码、编译、启动仿真器和运行仿真五个步骤。

2017-12-19 11:14:11 63886

63886

IARMSP430项目编译与JTAG仿真调试步骤。

2018-04-19 08:29:09 5

5 (1)交互式仿真方法:利用EDA工具的仿真器进行仿真,使用方便,但输入输出不便于记录规档,当输入量较多时不便于观察和比较。

2019-04-25 08:00:00 9300

9300

Xilinx针对Zynq 7000,Zynq Ultrascale + MPSoC和Microblaze的QEMU简介。

了解如何使用Xilinx的开源强大仿真平台加速您的开发。

2018-11-21 06:33:00 3325

3325 Xilinx合作伙伴和客户展示了他们如何使用Zynq仿真平台。

2019-01-03 13:14:43 4329

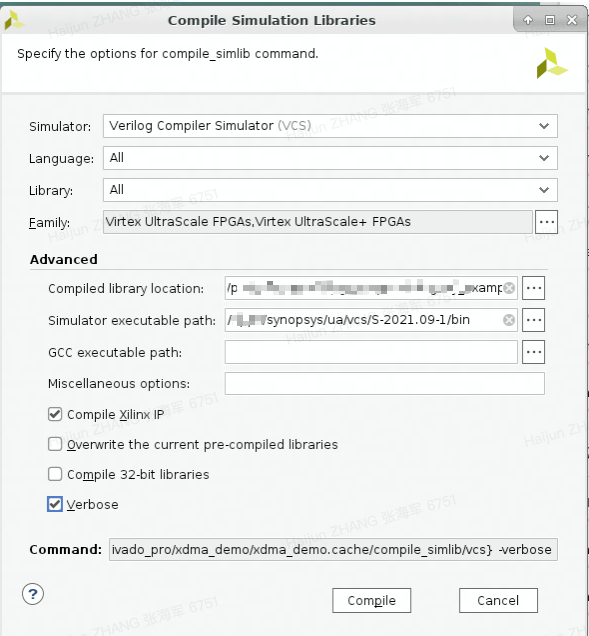

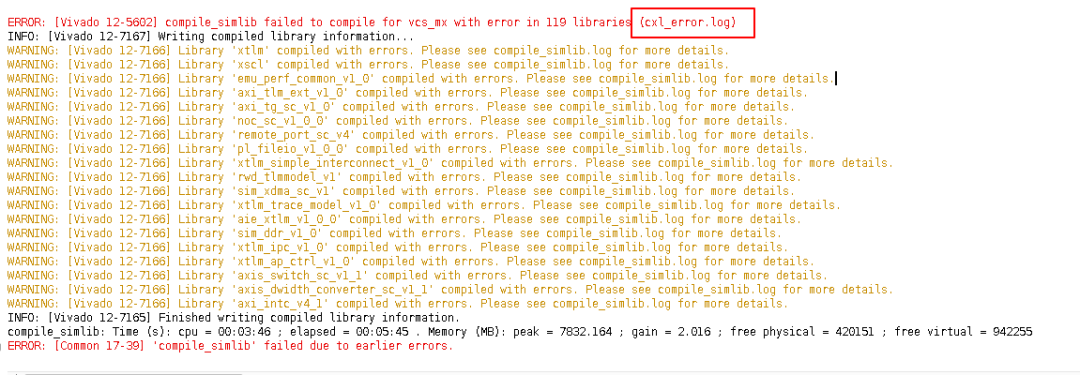

4329 了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI设计运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-29 06:59:00 4558

4558 了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI设计运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-29 06:57:00 6822

6822 ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括创建工程、编写源代码、编译、启动仿真器和运行仿真五个步骤,仿真流程如图1所示:

2018-12-29 11:35:14 9227

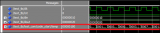

9227 若想用Verdi观察波形,需要在仿真时生成fsdb文件,而fsdb在vcs或者modelsim中的生成是通过两个系统调用$fsdbDumpfile $fsdbDumpvars来实现的。

2020-09-22 15:01:55 7809

7809 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409 stm32简单程序编译及完成51程序设计与仿真

2021-11-21 16:36:03 3

3 VCS是一个高性能、高容量的编译代码仿真器,它将高级抽象的验证技术集成到一个开放的本地平台中。它能够分析、编译和编译Verilog、VHDL、SystemVerilog和OpenVera所描述

2022-05-07 14:20:57 3907

3907 VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2022-05-23 16:04:45 7605

7605 本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。自此仿真设计一体化不是问题。

2022-08-10 09:15:17 2038

2038 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 1549

1549 电子发烧友网站提供《Anlogic器件仿真库快速编译与使用.pdf》资料免费下载

2022-09-27 11:05:41 2

2 开源RISC-V Hummingbird E203(蜂鸟E203)的仿真工具是开源的iverilog,这里利用vcs+verdi仿真工具进行仿真;

2022-11-17 10:28:36 2023

2023 Xilinx-vivado的网表形式有edf和dcp两个方式,两个方式各有不同。对于仿真来说,两者均需转换为verilog的形式进行仿真,只是使用的命令不同。

2022-12-20 10:06:39 3117

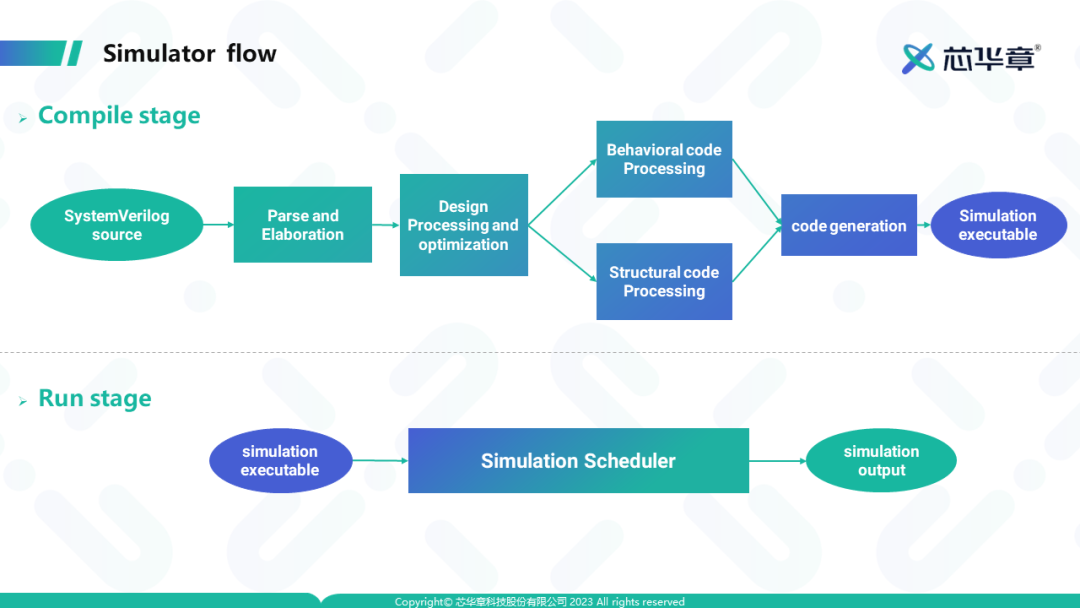

3117 几乎所有的芯片设计、芯片验证工程师,每天都在和VCS打交道,但是由于验证环境的统一化管理,一般将不同的编译仿真选项集成在一个文件里,只需要一两个人维护即可。所以大部分人比较少有机会去深入地学习VCS的仿真flow。基于此,本文将介绍VCS仿真的 两种flow ,概述这两种flow分别做了哪些事!

2023-01-10 11:20:38 2280

2280 的。可以说,EDA软件从诞生之日起,就带着强烈的仿真基因。因此,如果没有一款独立自主的数字仿真器,国产EDA实现对国外工具垄断的打破就无从谈起。 目前,行业主流的仿真器,诸如VCS,Xcelium, Questa等,都是国外EDA大厂花了数十年的时间开发、迭代而来的。这些软件内部设计极其复

2023-03-21 13:35:24 745

745

下图是一个典型的EDA仿真验证环境,其中主要的组件就是激励生成、检查和覆盖率收集。

2023-04-15 10:13:06 1231

1231 EDA技术的核心并不是仿真,仿真只是EDA技术的一个重要环节。EDA技术的核心是利用计算机辅助设计(CAD)工具,将电路设计自动化,实现从电路设计到制造的全流程自动化。仿真只是在这一流程中的重要一环,用于验证设计的正确性、可靠性和稳定性等方面。

2023-04-24 18:22:15 1875

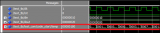

1875 我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

2023-05-08 16:00:57 4238

4238

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件内容如下:

2023-05-11 17:03:36 1268

1268

VCS是一款常见的Verilog编译工具,它提供很多编译选项来控制编译过程及其输出。本文主要介绍以下两个编译选项。

2023-05-29 14:46:39 6967

6967 VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-05-30 09:26:05 807

807

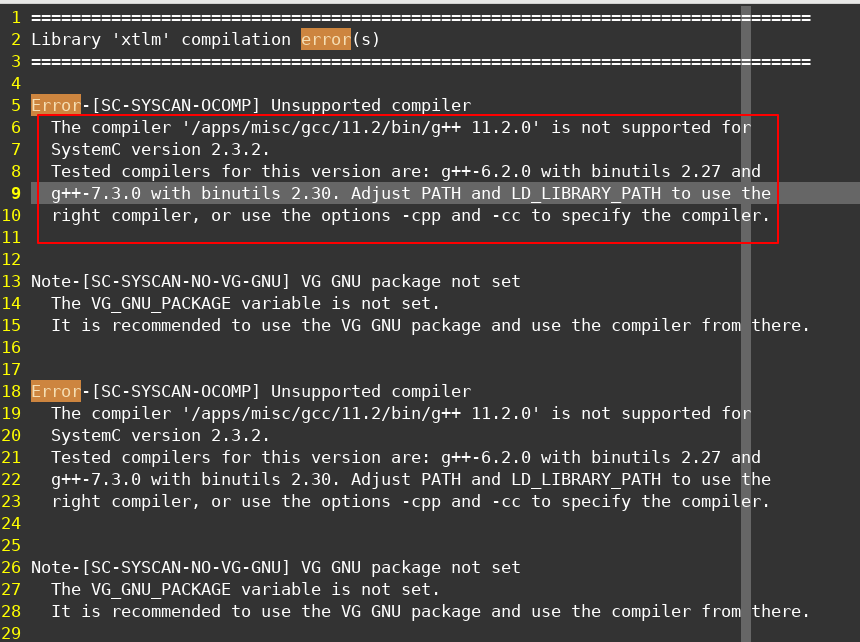

最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09:56 1597

1597

使用VCS仿真Vivado里面的IP核时,如果Vivado的IP核的仿真文件只有VHDL时,仿真将变得有些困难,VCS不能直接仿真VHDL

2023-06-06 11:15:35 1328

1328

电子发烧友网站提供《Xilinx快速仿真器:用户指南.pdf》资料免费下载

2023-09-15 14:54:25 0

0 Cadence仿真步骤

2022-12-30 09:19:47 13

13 Calibre是一种先进的电子设计自动化(EDA)工具,用于电子电路的设计和仿真。它为工程师提供了一个强大的平台,可以进行多个级别的仿真,包括电路级仿真、行为级仿真和系统级仿真。在使用Calibre

2024-01-04 17:24:59 301

301 VCS的仿真选项分编译(compile-time)选项和运行(run-time)选项。编译选项用于RTL/TB的编译,一遍是编译了就定了,不能在仿真中更改其特性,例如define等等。

2024-01-06 10:19:49 347

347

电子发烧友App

电子发烧友App

评论