数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 459

459 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-01-13 13:57:47 1830

1830

综合就是把Verilog、VHDL转换成网表的过程。综合按照是否考虑物理布局信息可分为逻辑综合和物理综合。

2023-08-09 09:51:15 638

638

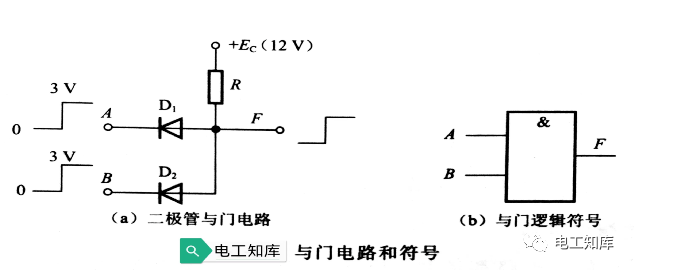

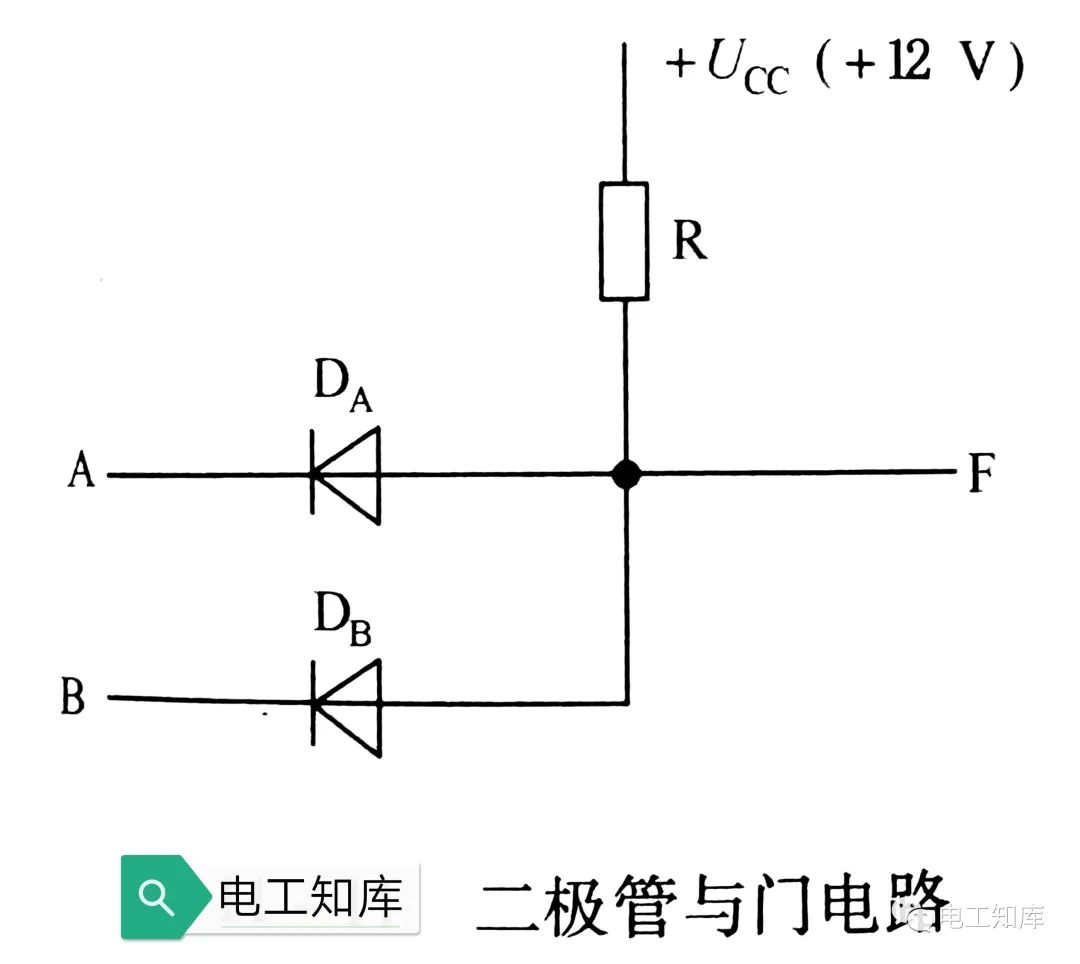

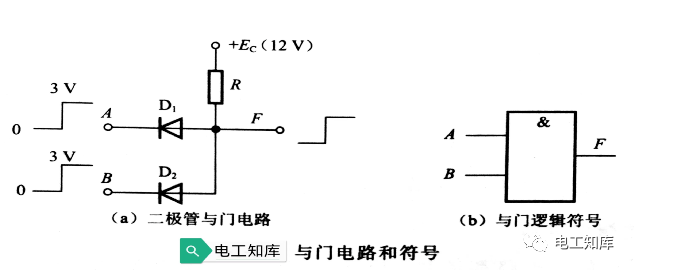

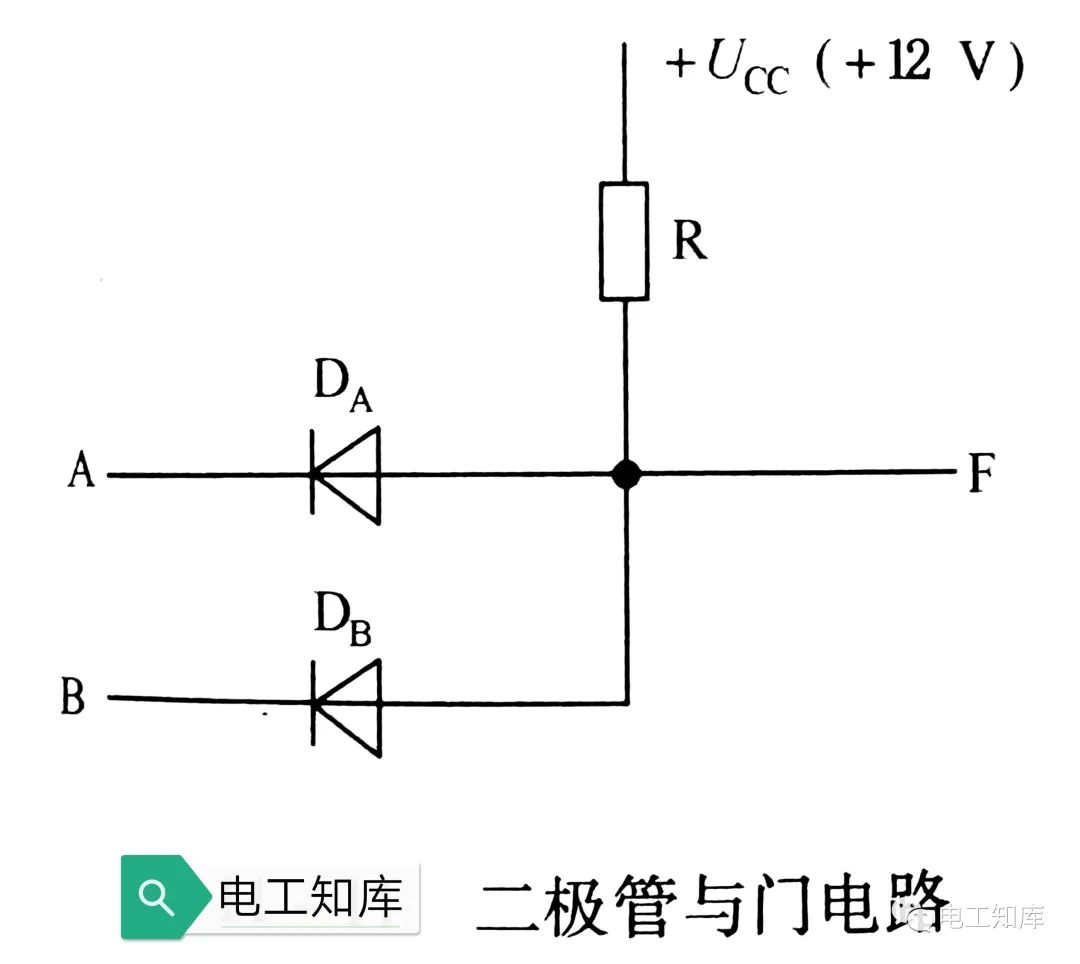

一、逻辑门电路有关概念 1、逻辑 所谓逻辑是指条件与结果之间的关系。最基本的逻辑关系是与、或、非。 2、逻辑电路 输入与输出信号之间存在一定逻辑关系的电路称为逻辑电路。 3、门 所谓门就是一种开关

2023-09-15 11:14:30 820

820

一、基本概念 1、门电路 门电路是数字电路的基本单元部件,如果把电路的输入信号看做“条件”,把输出信号看作“结果”,当“条件”具备时,“结果”就会发生。 2、逻辑门电路 门电路输入和输出之间存在一定

2023-10-10 10:15:47 1409

1409

transfer level)描述、逻辑综合(logic synthesis)三个层次,将设计内容逐步细化,最后完成整体设计,这是一种全新的设计思想与设计理念。2.fpga原理---今天,数字电子系

2013-09-02 15:19:20

工具将高层次描述转化为低层次门级描述,其中综合可分为三个层次:高层次综合(High-Level Synthesis)、逻辑综合(Logic Synthesis)和版图综合(Layout

2008-06-26 16:16:11

Transfer Level)描述、逻辑综合(Logic Synthesis)三个层次,将设计内容逐步细化,最后完成整体设计,这是一种全新的设计思想与设计理念。2.FPGA原理---今天,数字电子系

2008-06-27 10:26:34

、逻辑分割、逻辑综合及优化、逻辑布线、逻辑仿真、适配编译、逻辑映射和下载等一系列工作。目前,EDA主要辅助进行三方面的设计工作,即集成电路(IC)设计、电子电路设计和PCB设计。EDA技术已有30年的发展

2019-02-21 09:41:58

请问什么是EDA?那么FPGA是EDA的一种,为什么要有EDA这么一个总的概念?

2014-07-09 18:13:42

本帖最后由 gk320830 于 2015-3-9 22:17 编辑

逻辑函数与逻辑问题的描述 在讨论了与、或、非三种基本逻辑运算后,下面将从工程实际出发,提出逻辑命题,然后用真值表加以描述

2009-04-06 23:57:10

DC逻辑综合详解DC软件简介逻辑综合DC命令DC软件简介DC( Design Compiler )为Synopsys公司逻辑合成工具。DC得到全球60多个半导体厂商、380多个工艺库的支持。据

2021-07-29 08:07:14

可综合的语法子集1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 所谓可综合的语法,是指硬件能够实现的一些

2015-06-12 10:59:24

可综合的语法子集2本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt(1) 参数定义:parameter

2015-06-15 14:57:27

可综合的语法子集3本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt(1) 多语句定义:begin…end

2015-06-17 11:53:27

,版权所有)对于一些复杂的FPGA开发,工程师的设计习惯和代码风格将会在很大程度上影响器件的时序性能、逻辑资源的利用率以及系统的可靠性。有人可能会说,今天的EDA综合工具已经做得非常强大了,能够在很大程度

2015-06-25 09:41:55

太长)太糟糕。因此,设计者往往只要通过优化这些关键路径就可以改善时序性能。而这些关键路径所经过的逻辑门过多往往是设计者在代码编写时误导综合工具所导致的,那么,举一个简单的例子,看看两段不同的代码,关键

2015-07-02 22:17:18

可能不是那么容易理解。不过没有关系,我们会简化这个过程,从实际操作角度,以一个比较简化的顺序的方式来理解这个流程。如图1.7所示,从大的方面来看,FPGA开发流程不过是三个阶段,第一个阶段是概念阶段

2015-03-31 09:27:38

原则HDL代码综合后电路质量的好坏主要取决于三个方面:RTL实现是否合理、对厂家器件特点的理解和对综合器掌握的程度。参考[url=]10[/url]中有比较全面的讨论。4.1.1 关于

2020-05-15 07:00:00

`所谓综合,就是将HDL语言、原理图等设计输入翻译成由与、或、非门和RAM、触发器等基本逻辑单元的逻辑连接(网表),并根据目标和要求(约束条件)优化所生成的逻辑连接,生成EDF文件。完成了输入、仿真

2012-02-24 10:44:57

对进行时序路径、工作环境、设计规则等进行约束完成之后,DC就可以进行综合、优化时序了,DC的优化步骤将在下面进行讲解。然而,当普通模式下不能进行优化的,就需要我们进行编写脚本来改进DC的优化来达到

2021-07-30 06:18:54

使用的更多信息,请参阅(UG901)Vivado设计工具用户指南:Synthesis(综合)。 分析日志文件中的信息图4是通过重定时提升逻辑水平的一个例子,该电路结构中有一个关键的路径分为三个逻辑层

2019-03-14 12:32:05

就比较好的解决了这个问题,我们可以将这些功能加到FPGA设计当中。其中待测设计就是我们整个的逻辑设计模块,在线逻辑分析仪也同样是在FPGA设计中。通过一个或多个探针来采集希望观察的信号。然后通过JTAG接口

2023-04-17 16:33:55

=BA+BD+BC 代人规则可以扩展所有基本定律的应用范围。2.反演规则3.对偶规则三、逻辑函数的代数变换与化简法1.逻辑函数的变换 例:求同或函数的非函数。 解: 这个函数称为异或函数,它表示当两个输入变量

2009-04-07 10:54:26

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,了解详情。

2014-07-03 16:45:35

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:52:39

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:55:20

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:57:13

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,了解详情。

2014-07-03 16:41:33

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:09:45

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:11:09

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:12:57

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:13:38

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:53:35

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:54:14

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-02 16:05:11

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:55:08

git的三个核心概念(工作区,版本库stage,版本库master)

2020-12-24 07:17:22

。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上

2012-10-20 08:10:13

1,在一个verilog程序里,如果循环是一个循环次数不可定的循环,那么它能被综合工具综合吗2,如果程序里有always @(clock)里面又嵌套了@(clock)这样的控制事件,这个能被综合吗

2015-02-03 15:29:11

,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞

2012-02-27 15:01:27

,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task(当task中程序是组合逻辑时就可以被综合

2015-01-05 19:42:44

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯群275855756了解详情。

2014-05-07 20:28:59

)和CAE(计算机辅助工程)的概念发展而来的。EDA技术是以计算机为工具,根据硬件描述语言HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简

2019-07-30 06:20:05

DC软件怎么样?什么是逻辑综合?

2021-11-02 06:41:35

,也就不会出现在sof的网表文件中。用于综合目的的代码,EDA会将它综合成为一个电路,当然需要动用其综合目的的一系列算法资源和步骤,时间也比较长。而编写用于综合目的的代码,需要按照可综合原则编写HDL

2018-02-26 15:32:30

综合是将我们的设计转化为FPGA可以读懂的配置文件的第一个步骤。本文努力从0基础开始向大家说明综合的基本知识和高级技巧。话说所有的功能都有它应用的环境。在了解某个按钮选项有某个功能的时候,我们更应该

2018-08-08 10:31:27

可编程逻辑设计技术展望3.可编程逻辑器件硬件上的四大发展趋势4.EDA软件设计方法及发展趋势5.FPGA的设计流程6.FPGA的常用开发工具7.FPGA的基本结构8.主流低成本FPGA

2018-09-19 11:34:03

quartus ii 13.0版本,我设计好了几个模块但是不同的project,在不同的文件夹下,我怎么才能将他们放到一起进行逻辑综合呢?求解答!

2016-05-02 22:19:02

功能仿真:可以验证代码的逻辑性,不加任何的时延信息。仿真工具为modelsim(组合逻辑和时序逻辑都可以功能仿真),modelsim不能综合。在modelsim中添加相应的激励信号,调用

2016-08-23 16:57:06

;// 逻辑与||// 逻辑或赋值符号:= 和 <=。阻塞和非阻塞赋值,在具体设计中是很有讲究的,我们会在具体实例中掌握他们的不同用法。可综合的语法是verilog可用语法里很小的一个子集,硬件

2017-12-19 21:36:24

可综合的VerilogHDL设计实例在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编写、Top-Down设计方法、还学习了可综合风格的有限状态机

2009-11-23 16:01:33

移位加法实现串行加法器。设两个无符号数A=a-tart...ao和B=b.-,b,^...bo,两者相加产生的和SUM=S-lS-:...So,其工作原理如图1所示,由三个移位寄存器和一个加法器

2018-11-20 10:39:39

个好的综合网表同时也可以提高后端物理实现的质量和效率。中科芯云微电子科技有限公司(青岛EDA中心)联合Synopsys、青岛集成电路人才创新培养联盟、青岛微电子创新中心将举办“Design

2021-06-23 06:59:32

工业4.0愿望和网络安全含义实现网络安全工业4.0的三个步骤通过硬件安全性实现互联工厂

2021-02-19 06:50:19

实验目的掌握常用组合逻辑电路的 EDA 设计方法;熟练掌握基于 QuartusII 集成开发环境的组合逻辑电路设计流程;加深对 VerilogHDL 语言的理解;熟练掌握 DE2-115 开发板

2022-01-12 06:35:59

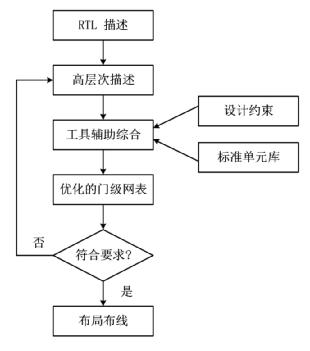

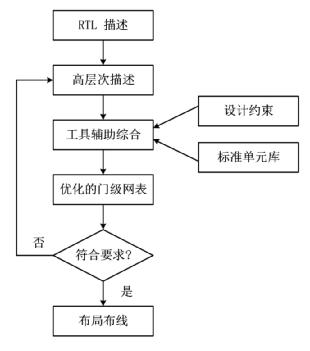

、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。即实现 在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。数字电路的逻辑综合包括三个步骤:综合=转化+映射+逻辑优化,具体的流程如下图所示;转换阶段:综合工具将 HDL.

2021-11-17 07:08:49

手工综合RTL级代码的理论依据和实用方法时序逻辑综合的实现方法

2021-04-08 06:06:35

浅谈IC设计中逻辑综合引言在IC设计流程中,逻辑综合是后端设计中很重要的一个环节。综合就是指使用综合工具,根据芯片制造商提供的基本电路单元库,将硬件描述语言描述的RTL 级电路转换为电路网表的过程

2013-05-16 20:02:50

感觉自从使用纯非阻塞赋值实现各种接口后,综合快了很多,而且资源占用也少了

2020-06-11 10:22:35

分析、整体与模块的仿真分析三个步骤,使硬件实现了闹钟的显示以及整点报时等功能,其中整点报时采用整体复位、按键选择演奏方式、循环演奏以及数码管显示乐谱的功能。系统能自动从头开始循环播放,也可随时起停、按键

2015-12-14 21:38:41

下图揭示了高层次综合工作的基本流程,以及它于传统的RTL综合流程的对比。接下来将对行为描述,行为综合,分析与优化三个主要子流程详细描述。 1、行为描述 当我们把HLS技术的起点立为一种

2021-01-06 17:52:14

如何保证RTL设计与综合后网表的一致性文章简介:在超大规模数字集成电路的设计中,我们使用逻辑综合工具来完成从RTL设计到门级网表的转化。我们希望它综合出的门级网表

2009-01-23 23:10:52 19

19 Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 设计编译器(Design Compiler)和设计分析器(Design Analyzer) Design Compiler(DC) 是Synopsys逻辑综合工具的命令行接口

2009-11-19 13:32:16 57

57 介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。关键词:电子设计自动化 可编程逻辑

2010-07-18 10:38:50 22

22 介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词 电子设计自动化 可编程逻辑

2009-06-16 08:55:30 395

395

摘 要:介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词:电

2009-06-20 12:06:06 579

579

芯片综合的过程:芯片的规格说明,芯片设计的划分,预布局,RTL 逻辑单元的综合,各逻辑单元的集成,测试,布局规划,布局布线,最终验证等步骤。设计流程与思想概述:一个设计

2011-12-29 16:28:35 25

25 本文简单探讨了verilog HDL设计中的可综合性问题,适合HDL初学者阅读 用组合逻辑实现的电路和用时序逻辑实现的 电路要分配到不同的进程中。 不要使用枚举类型的属性。 Integer应加范围

2012-01-17 11:17:03 0

0 逻辑综合带来了数字设计行业的革命,有效地提高了生产率,减少了设计周期时间。在手动转换设计的年代,设计过程受到诸多限制,结更容易带来人为的错误。而一个小小的错误就导

2012-06-25 15:21:14 44

44 第1章-EDA设计导论 第2章-可编程逻辑器件设计方法 第3章-VHDL语言基础 第4章-数字逻辑单元设计 第5章-VHDL高级设计技术 第6章-基于HDL和原理图的设计输入 第7章-设计综合和行为仿真 第8章

2012-09-18 11:35:36 550

550 基于FPGA的EDA综合实验系统设计_赵刚

2017-03-19 11:38:26 2

2 组合逻辑电路的设计与分析过程相反,本文小编主要跟大家介绍一下关于组合逻辑电路的设计步骤,顺便回顾一下组合逻辑电路的分析方法。

2018-01-30 16:46:31 119435

119435

FPGA技术概念

CPLD (Complex Programmable Logic Device)FPGA (Field Programmable Gate Array)

EDA技术 密度逻辑

2019-03-29 16:53:55 7

7 本文档的主要内容详细介绍的是ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明包括了:1、逻辑综合基本概念 a) Synopsys综合工具及相关工具 b) 逻辑综合

2019-10-23 08:00:00 5

5 将组合逻辑电路的设计的实例引入到EDA中,进一步将电子设计自动化EDA(Electronic Design Automation)应用于数字电子技术教学中,而Multisim9软件是一个专门用于电子线路仿真与设计的EDA工具软件,为该课程的教学和学习打下一个良好的基础。

2020-01-21 16:46:00 2502

2502

组合逻辑设计法适合于设计开关量控制程序,它是对控制任务进行逻辑分析和综合,将元件的通、断电状态视为以触点通、断状态为逻辑变量的逻辑函数,对经过化简的逻辑函数,利用PLC逻辑指令可顺利地设计出满足要求且较为简练的程序。这种方法设计思路清晰,所编写的程序易于优化。

2020-05-22 08:49:00 3840

3840 随着可编程逻辑器件和EDA技术的出现,使数字系统功能实现及系统的设计方法发生了革命性的变化,因此改革和整合传统的教学内容,将EDA技术引人到“数字逻辑”课程的教学中是十分必要的。

2020-10-02 17:31:00 1362

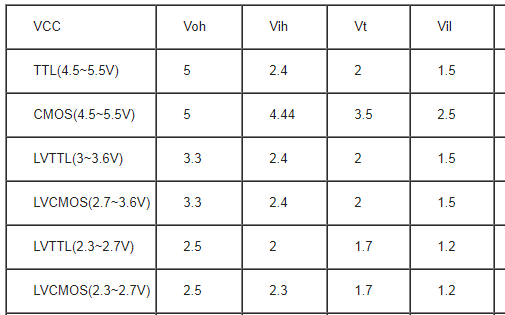

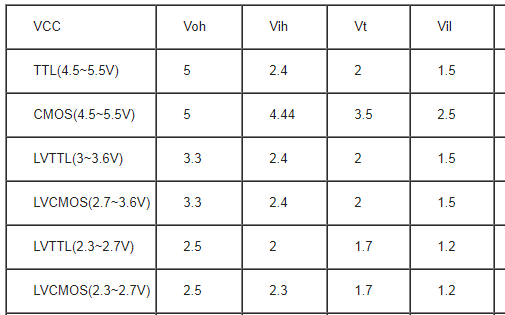

1362 本篇为逻辑电平系列文章中的第一篇,主要介绍逻辑电平相关的一些基本概念。后续将会介绍常见的单端逻辑电平(针对CMOS的闩锁效应进行详细介绍)、差分逻辑电平、单端逻辑电平的互连、差分逻辑电平的互连、一些

2021-01-02 09:45:00 22570

22570

在一套标准的布线系统中,为现代建筑的系统集成提供了物理介质。那综合布线系统设计步骤你清楚吗?科兰小编为您介绍。

2022-06-24 15:22:06 2345

2345 逻辑综合(Logic Synth.)过程需要约束(Stat. Wire Model)以产生规定条件下的电路。具体电路设计完成后,需进行门级仿真(Gate-Lev.Sim),以检查电路设计是否出现失误。

2022-08-12 15:06:43 4149

4149 逻辑综合操作(Compile design),根据芯片的复杂程度,逻辑综合操作的时间可能是几秒,也可能是半个月。如果设计环境和约束设置不当,逻辑综合操作的时间会被延长。

2022-08-12 15:10:21 3396

3396 执行算法逻辑(加、减、乘、除及复杂的组合运算)优化。例如,乘法器有多种实现方式, 相应地会产生多种时序、功耗及面积,如何根据目标设定选出最合适的结构将对最后的综合结果有重大影响。

2022-08-24 14:51:13 967

967 Quarus Ⅱ工具提供四种手段分析逻辑综合结果,包括:RTL Viewer、Technology Viewer、PowerPlay Power Analyzer Tool、State Machine Viewer。

2022-08-25 10:53:03 913

913 利用工具将RTL代码转化为门级网表的过程称为逻辑综合。综合一个设计的过程,从读取RTL代码开始,通过时序约束关系,映射产生一个门级网表。

2022-11-28 16:02:11 1822

1822 综合,就是在标准单元库和特定的设计约束基础上,把数字设计的高层次描述转换为优化的门级网表的过程。标准单元库对应工艺库,可以包含简单的与门、非门等基本逻辑门单元,也可以包含特殊的宏单元,例如乘法器、特殊的时钟触发器等。设计约束一般包括时序、负载、面积、功耗等方面的约束。

2023-03-30 11:45:49 556

556

综合布线是目前智能楼宇办公等最常见的布线方式,对于建筑来说这是一个比较重要的环节,施工完成后一定要进行细致的测试,这样才能保证成功率,于是科兰小编为大家介绍一次啊综合布线完成施工后的三个必要测试

2023-05-18 11:00:48 566

566 在一套标准的布线系统中,为现代建筑的系统集成提供了物理介质。那综合布线系统设计步骤你清楚吗?科兰小编为您介绍。 综合布线系统设计步骤: 1、先确定用户方的需求。 2、根据需求确定综合布线是要做6个区(工作区、水平区、垂

2023-06-08 10:07:01 588

588 EDA(Electronic Design Automation,电子设计自动化)综合是指在集成电路设计过程中将高级描述语言(HDL)代码转换为逻辑网表的过程。

2023-06-26 14:05:00 1108

1108 综合就是将HDL语言转化成与,非,或门等等基本逻辑单元组成的门级连接。因此,可综合语句就是能够通过EDA工具自动转化成硬件逻辑的语句。

2023-06-28 10:39:46 784

784 Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 逻辑综合是将RTL描述的电路转换成门级描述的电路,将HDL语言描述的电路转换为性能、面积和时序等因素约束下的门级电路网表。

2023-09-15 15:22:52 1914

1914

电子发烧友App

电子发烧友App

评论