低功耗芯片设计是本世纪以来最重要的新兴设计方法。可以说没有低功耗设计,就没有今天的智能手机,移动设备,物联网,及高性能计算等产业。随着芯片图形尺寸越来越小,低功耗设计在现在及未来的芯片中会起到越来越重要的作用。低功耗技术也贯穿整个SOC设计的流程,可以预见的是低功耗设计也将越来越重要,所以深入理解低功耗技术是我们芯片设计进阶的必经之路。

1. 低功耗设计的目的

1.1 低功耗设计技术的产生

回顾芯片设计发展的三个阶段,我们可以发现,不同的技术是为了解决特定问题而产生的:

第一个为解决设计复杂度的阶段: 80年代开发的逻辑综合工具极大得提高了设计效率;

第二个为提高设计规模和频率的阶段: 90年代IP复用让大规模SOC能快速推出市场,同时时钟频率从几十MHz提高到了GHz。芯片设计也是围绕着时钟频率与时序进行,例如像时序驱动的逻辑综合及布局布线等。

第三个为低功耗设计阶段 。 进入二十一世纪后,人们逐渐认识到单纯靠增加时钟频率再也不能提高性能了。 相反的,功耗的增加带来了一系列问题。例如芯片温度增高引起的散热及电路性能下降,电源及信号噪声管理等。本世纪初以来移动设备特别是手机的兴起更是引发了低功耗芯片设计的浪潮。

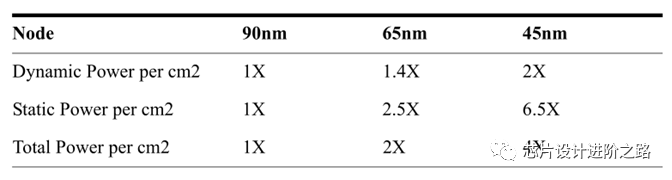

如果不加入低功耗技术,那么功耗发展的趋势大概如下表所示(可能不是很准确,只是给大家一个直观的印象):

可以看到,总功耗大概是翻倍的增加。英特尔曾在1999年给出了其处理器功率密度随着时间的变化如下图所示。

可以看到,按照当时的发展趋势(摩尔定律),晶体管的尺寸逐年缩小,芯片上的功率密度将很快达到甚至超过核反应堆甚至火箭喷口的功率密度,这是一个不可控的状态。因此,当时的业界共识是35纳米就是工艺的极限了。

但是事实上,现在的工艺水平已经到了7nm;5nm甚至3nm已经在开发中了。这里面低功耗设计功不可没,可以说低功耗设计在给摩尔定律续命,也成就了现在半导体的繁荣。

1.2 低功耗设计的目的

功耗(Power)和能量(Energy)是两个完全不同的概念,但是生活中很多人会把他们混淆起来。我们作为芯片工程师,一定不能犯这种低级错误,否则就贻笑大方了。

功耗是一个瞬时的概念,而能量是一个时间内的消耗。

能量=功耗*时间

概念可以自己去查。用一个简单的图表示如下:

稍微分析一下就可以知道,比如手机,能量越大(也就是电池越大),使用时间越长。同时如果功率越小,就显得越不耗电,使用时间就越长。

所以低功耗时间的最直接的目的就是:

这个是大家最直观的感受。比如手机,现在“充电五分钟,通话两小时”已经是标配了。如果是“充电两小时,通话五分钟”那场景不忍直视了。

还有,电动汽车,现在的电池容量和续航里程已经是直接的竞争指标了。

记得最深刻的是,当年高通骁龙820就是功耗没做好,输给了麒麟920,给了华为麒麟崛起的机会。现在华为手机电池耐用已经深入人心了。可以看到,低功耗技术直接决定商业竞争的成败,这是“几千亿的大生意”啊(手动狗头)!

- 提高设备的可靠性

随着设备消耗能量,会产生热量。功耗越大,产生热量越快。如果不能及时散热,那么设备温度就会升高。温度升高可能导致设备不能正常工作甚至损坏。所以有些芯片会在温度升高时候,把频率降低,本来能跑2GHz的CPU,温度高了就只能跑1G,这个以前在用手机玩游戏的时候体验比较明显。

- 降低成本

功耗越大,产生热量越快,对封装,散热系统等要求越高。比如,低功耗的只需要塑料封装就能保证正常功能,高功耗的就可能需要陶瓷封装,成本自然就高很多。再比如,低功耗的可能自然散热就能保证正常功能,高功耗的可能需要水冷,加铜片等等,这些都会导致成本上升。

成本的高低直接决定商业的成败,可能你能做出功能很强的产品,但是如果做出来没人买的起,或者同等功能下,别的公司成品低很多,那也是一个失败的产品。

低功耗对芯片的影响还有很多方面。可以说现在低功耗技术在芯片设计中已经是不可缺少,并且贯穿芯片设计的前后端整个流程。了解低功耗技术对芯片设计也是极其重要的。

2. 功耗的组成

低功耗技术就是一系列的降低功耗的技术。

在了解低功耗技术之前,我们必须先了解功耗的构成。

一个SOC芯片的功耗由两部分组成:动态功耗和静态功耗。

动态功耗是设备运行时或者说信号改变时所消耗的功耗;

静态功耗是设备上电但是信号没有改变时所消耗的功耗;

这里要注意的是:在设备运行时,也需要消耗静态功耗的,因为设备运行时也是上电状态。功耗分类把静态功耗单独拿出来,只是为了理论分析方便。

2.1 动态功耗

动态功耗可以分为:

1.翻转功耗(有的地方称为开关功耗,但是笔者认为这个名字不准确,因为开关包含的功耗很多,其实是从英文switching power翻译过来,从switching可以看到,名称想表现是动作。所以称为翻转功耗比较准确)

- 短路功耗(或者称为内部功耗,英文是internal power)

2.1.1 翻转功耗(switching power)

Switching power 是一个门电路对输出电容进行充电和放电需要的功耗。简单的说就是一个门电路输出从0变到1和从1变到0所需要消耗的功耗。

Switching power 是动态功耗最主要的组成部分。

下面是一个CMOS非门(反相器)的门电路,输出接了一个输出电容:

清晰一点的符号图如下:

每次传输的能量消耗为:

CL是输出的电容大小;Vdd是供电电压。这样我们可以计算出传输的功耗为:

f是传输的频率;Ptrans是输出翻转的概率;fclock是时钟频率。

这里用fclock*Ptrans=f是合理的,因为时钟就是输出是否改变的参考,乘以概率,就是翻转的频率。

如果我们定义:

即把电容乘以翻转概率定义为有效电容,那么我们可以得到经常见到的计算公式如下:

推导过程其实很简单,但是这个最终的结果却十分重要。

- Switching power 和电压,翻转率,负载电容有关;

- Switching power和数据无关,也就传输的数据不会影响翻转功耗,但是数据的翻转率会影响翻转功耗;

- Switching power和传输的大小也无关

由这个公式我们很容易得到如果想减少功耗,那么方法就是:

- 降低电压;

- 降低翻转率;

- 减少负载电容

当然,这些方法的前提永远是 芯片的功能要满足要求 。功率再低,功能不满足的芯片和板砖有什么区别,起码板砖还能拍人。

芯片的功能要满足要求这个基础就决定了这些方法有一些限制,比如不可能把电压降到0,不可能让信号永远不翻转,不可能电容减少到0。这些都是前提。

2.1.2 内部功耗(internal power)

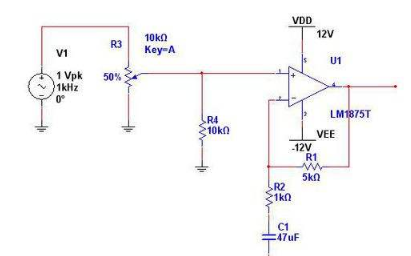

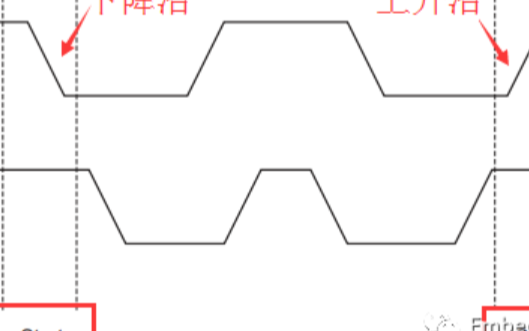

内部功耗又可以称为短路功耗,因为主要原因是由于短路造成的。短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流,如下面的反相器电路图所示:

加上短路功耗后,总的动态功耗如下:

后面的部分就是短路功耗。tsc是短路电流持续的时间,Ipeak是总的短路电流(包含了内部电容充电的电流)

由于传输中短路持续的时间特别短,短路功耗相比翻转功耗来说小很多。所以一般情况下会忽略短路功耗,把翻转功耗就当作动态功耗,那么动态功耗的简化公式就是:

但是值得注意的是,有的情况下,还是要考虑短路功耗,比如如何处理门控模块的悬空的输出的时候。

2.2 静态功耗

静态功耗是由于漏电流引起的,在CMOS 门中,漏电流主要来自4个源头:

- 亚阈值漏电流(Sub-thresholdLeakage, ISUB): 亚阈值泄漏电流是晶体管应当截止时流过的电流.

- 栅极漏电流(GateLeakage, Igate): 由于栅极氧化物隧穿和热载流子注入,从栅极直接通过氧化物流到衬底的电流。

- 栅极感应漏电流(GateInduced Drain Leakage, IGIDL): 结泄漏电流发生在源或漏扩散区处在与衬底不同电位的情况下。结泄漏电流与其他泄漏电流相比时通常都很小。

- 反向偏置结泄漏(ReverseBias Junction Leakage ,IREV):由少数载流子漂移和在耗尽区产生电子/空穴对引起。

MOS管的结构图如下:

漏电流组成如下图所示:

2.2.1亚阈值漏电流(Sub-thresholdLeakage)

亚阈值漏电流(Sub-thresholdLeakage)发生在CMOS gate没有完全关断时。一个比较好的计算公式如下:

W/L是晶体管的尺寸,Vth是热相关常量;Cox/Vth/W/L都是工艺相关,不可以调整。VGS就是VDD;

VT 是阈值电压 ;可以看到,阈值电压越高,漏电功耗就越低。但是阈值电压越高,对应的翻转速度就会越慢,延时就会越大,性能就越差。

- 可以通过调整VDD/VT来降低漏电流,从而减少漏电功耗。

- 增加VT会带来性能损失,只能在满足功能需求前提下增加VT;

- ISUB只和VDD/VT有关,和信号翻转这些都没关系。这是一个工艺强相关的电流,RTL设计对其无影响。

亚阈值泄漏电流随温度呈指数增长(Vth)。这大大增加了设计低功率系统的复杂性。即使在室温下的泄漏是可以接受的,在最坏的情况下,温度会超过芯片的设计目标。

2.2.2栅极漏电流(Gate Leakage)

栅极泄漏电流发生在一个电压加到栅上时(例如当门导通时)载流子遂穿通过薄栅介质的情况下。

泄漏电流与介质厚度有极强的关系。工艺中通过选择合适厚度的介质将栅泄漏电流限制到一个可接受的水平上。泄漏电流还取决于栅极电压。通过使晶体管堆叠起来并使截止晶体管靠近电源/地线可以使栅泄漏电流减小。

在以往的技术节点中,漏电电流一直以亚阈值漏电为主。但是从90nm开始,门极漏电几乎是亚阈值漏电的1/3。在某些情况下,在65nm工艺下,它可以等于亚阈值泄漏。低于65nm,high-k介电材料必须进行保持门级泄漏电流检查,这似乎是唯一有效减少门泄漏电流的方法。

其他两种流电流占比比较小,所以一般不做分析。有时会把静态功耗统一为一个公式:

Ipeak为泄露电流,减少静态功耗的方法就是减小VDD和Ipeak。

2.3 不同结构的功耗组成

SOC中不同结构的对功耗的消耗是不一样的。有几个功耗大户如下:

- 时钟树功耗:时钟树的功耗通常占整个SOC功耗的40%左右,这是因为时钟是一直在翻转的信号,所以动态功耗特别大。所以门控时钟技术就特别重要。

- CPU: CPU是SOC主控制器,工作时CPU一般都必须要打开,随着CPU频率越来越高,功耗也越来越大。所以现在的多核,大小核就比较流行,不同场景下用不同功耗的CPU核;

- GPU: GPU是并行处理单元,由于其算力主要来自多个模块并行计算,为了正常工作,通常需要很多模块同时运算,功耗也很大,所以很多SOC都不带GPU或者默认关掉;

- 存储器:DDR这些存储器作为SOC主存也需要时刻使用,也是功耗消耗的大户。

SOC还有很大其他模块,但是时钟树,CPU/GPU, 存储器占了绝大部分的功耗。在AI芯片的时代,CCN IP也是功耗的主要来源,和GPU比较类似。

后记

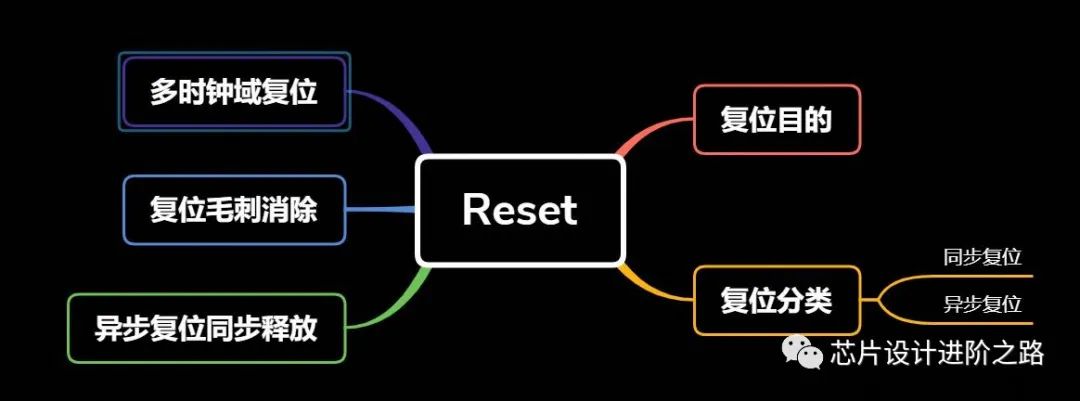

为了方便理解和总结,本文的思维导图如下:

低功耗技术是SOC芯片设计必须掌握的技术,不是之一。因为我们正处在低功耗芯片设计的时代。如果你不懂低功耗技术,那么可能你就很难理解整个芯片设计中各种做法的原因,甚至很难听懂别人讨论时的“行话”,这些才是最致命的,可能会让人觉得你还没“入行”。

版权声明:

本文作者:烓围玮未。主要从事ISP/MIPI/SOC/车规芯片设计

首发于知乎专栏:芯片设计进阶之路

转发无需授权,请保留这段声明。

电子发烧友App

电子发烧友App

评论