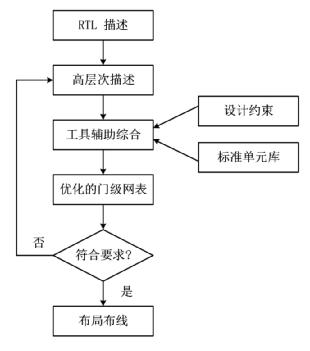

综合就是把Verilog、VHDL转换成网表的过程。综合按照是否考虑物理布局信息可分为逻辑综合和物理综合。

2023-08-09 09:51:15 638

638

描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件,这样的设计方法被称为高层次的电子设计方法。下面介绍与EDA基本特征有关的几个概念。

2019-10-08 14:25:32

系统进行方案设计和功能划分,由硬件描述语言完成系统行为级设计,利用先进的开发工具自动完成逻辑编译、化简、分割、综合、优化、布局布线(PAR,Place And Route)、仿真及特定目标芯片的适配

2008-06-26 16:16:11

、逻辑分割、逻辑综合及优化、逻辑布线、逻辑仿真、适配编译、逻辑映射和下载等一系列工作。目前,EDA主要辅助进行三方面的设计工作,即集成电路(IC)设计、电子电路设计和PCB设计。EDA技术已有30年的发展

2019-02-21 09:41:58

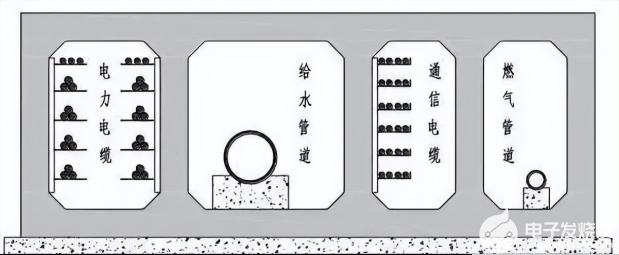

所谓综合布线系统是指按照标准的、统一的和简单的结构化方式编制和布置各种建筑物(或建筑群)内各种系统的通信线路,包括网络系统、电话系统、电源系统和照明系统等。因此,综合布线系统是一种标准通用的信息传输

2018-03-13 17:40:51

综合布线系统(Premises Distributed System,简称PDS)是一种集成化通用传输系统,在楼宇和园区范围内,利用双绞线或光缆来传输信息,可以连接电话、计算机、会议电视和监视电视等设备的结构化信息传输系统。

2020-03-19 09:00:45

综合布线系统凭借尖端的技术与智能化设计,具有无与伦比的优越性。那么谁知道综合布线系统中的屏蔽技术具体有哪些解决方案吗?

2019-08-06 06:28:23

谁来解释一下什么是综合布线系统?

2020-01-03 15:10:25

ADC&OLED综合应用是什么?

2022-02-09 07:31:49

用上华的0.6u数字库。DC综合后的报告是Total cell area: 1273.000000请问大侠这是什么意思。单位是um*2 的话面积好像太小了

2015-03-10 14:50:21

用上华的0.6u数字库。DC综合后的报告是Total cell area: 1273.000000请问大侠这是什么意思。单位是um*2 的话面积好像太小了。

2015-03-09 15:06:39

DC逻辑综合详解DC软件简介逻辑综合DC命令DC软件简介DC( Design Compiler )为Synopsys公司逻辑合成工具。DC得到全球60多个半导体厂商、380多个工艺库的支持。据

2021-07-29 08:07:14

可综合的语法子集2本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt(1) 参数定义:parameter

2015-06-15 14:57:27

可综合的语法子集3本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt(1) 多语句定义:begin…end

2015-06-17 11:53:27

apex20ke_atoms.v编译到其中。2:在图形界面中的Load Design对话框中装入仿真设计时,在Verilog 标签下指定预编译库的完整路径。(见下图)逻辑综合目前可用的FPGA综合工具

2020-05-15 07:00:00

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:17:54

之前在ISE上综合过,没报错,综合成功,当我用Synplify Pro重新建立工程,添加相同的.v文件,综合时,居然报错了。不知为什么,求知道的解答一下吧!报的错误如下图:[p=30,2,left]

2015-10-19 22:09:17

时序要求。理论部分以逻辑综合为主,不涉及物理库信息。在实战部分,我们将在DC的拓扑模式下进行。(本文主要参考虞希清的《专用集成电路设...

2021-07-30 06:18:54

ZNL-IR03工业机器人综合实训平台是什么?ZNL-IR03工业机器人综合实训平台有哪些特点?ZNL-IR03工业机器人综合实训平台有哪些技术参数?

2021-08-16 07:16:23

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,了解详情。

2014-07-03 16:45:35

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:52:39

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:55:20

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:57:13

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,了解详情。

2014-07-03 16:41:33

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:09:45

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:11:09

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:12:57

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-09 16:13:38

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:53:35

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:54:14

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-02 16:05:11

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯QQ群:275855756,了解详情。

2014-03-23 20:55:08

reg [7:0] mem [6:0]; reg [6:0] mem_adr; reg [7:0] mem_do;mem_do=mem[mem_adr];请问 这样使用 寄存器 能够综合吗?有什么优缺点呢

2015-10-28 18:36:19

,tri等,integer常用语for语句中(reg,wire时最常用的,一般tri和integer不用)☆ 参数定义:parameter☆ 运算操作符:各种逻辑操作符、移位操作符、算术操作符大多时可综合

2012-10-20 08:10:13

1,在一个verilog程序里,如果循环是一个循环次数不可定的循环,那么它能被综合工具综合吗2,如果程序里有always @(clock)里面又嵌套了@(clock)这样的控制事件,这个能被综合吗

2015-02-03 15:29:11

时,有的简单的initial也可以综合,不知道为什么)2、events event在同步test bench时更有用,不能综合。3、real 不支持real数据类型的综合。4、time 不支持time

2012-02-27 15:01:27

,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task(当task中程序是组合逻辑时就可以被综合

2015-01-05 19:42:44

verilog的仿真和综合有什么区别,请具体一点?

2018-06-06 22:41:18

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。启芯SoC年度培训计划,可加入启芯群275855756了解详情。

2014-05-07 20:28:59

)和CAE(计算机辅助工程)的概念发展而来的。EDA技术是以计算机为工具,根据硬件描述语言HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简

2019-07-30 06:20:05

DC软件怎么样?什么是逻辑综合?

2021-11-02 06:41:35

,也就不会出现在sof的网表文件中。用于综合目的的代码,EDA会将它综合成为一个电路,当然需要动用其综合目的的一系列算法资源和步骤,时间也比较长。而编写用于综合目的的代码,需要按照可综合原则编写HDL

2018-02-26 15:32:30

综合是将我们的设计转化为FPGA可以读懂的配置文件的第一个步骤。本文努力从0基础开始向大家说明综合的基本知识和高级技巧。话说所有的功能都有它应用的环境。在了解某个按钮选项有某个功能的时候,我们更应该

2018-08-08 10:31:27

互感器特性综合测试仪的主要应用是什么?使用互感器特性综合测试仪有哪些注意事项?

2021-08-31 07:51:43

功能仿真:可以验证代码的逻辑性,不加任何的时延信息。仿真工具为modelsim(组合逻辑和时序逻辑都可以功能仿真),modelsim不能综合。在modelsim中添加相应的激励信号,调用

2016-08-23 16:57:06

可综合的VerilogHDL设计实例在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编写、Top-Down设计方法、还学习了可综合风格的有限状态机

2009-11-23 16:01:33

随着设计复杂性增加,传统的综合方法面临越来越大的挑战。为此,Synplicity公司开发了同时适用于FPGA或 ASIC设计的多点综合技术,它集成了“自上而下”与“自下而上”综合方法的优势,能提供高结果质量和高生产率,同时削减存储器需求和运行时间。

2019-10-17 06:29:53

个好的综合网表同时也可以提高后端物理实现的质量和效率。中科芯云微电子科技有限公司(青岛EDA中心)联合Synopsys、青岛集成电路人才创新培养联盟、青岛微电子创新中心将举办“Design

2021-06-23 06:59:32

DC的综合优化阶段包括哪几部分?如何使用compile命令使DC进行综合优化设计呢?

2021-11-03 06:16:04

综合测试实验的 那个界面怎么做的 是有工具直接生成吗大神们指点一下 谢谢!!!

2019-11-05 04:35:39

有谁来解答一下如何去消除综合与时序导致的差异吗?

2021-04-30 06:20:15

怎么借助物理综合提高FPGA设计效能?

2021-05-07 06:21:18

用HDL编写的程序,怎么用modelsim或是quartus查看综合后形成的电路,即HDL所描述的电路。初学者,望关照!

2013-03-13 14:54:19

一个是自己写的ram,用寄存器阵列写的,例如:reg [31:0] ram [1024];还有一个是ip核生成的,这两个在综合的时候有什么区别?

2016-01-06 17:03:27

在循环中嵌入定时语句,比如"always @ posedge clk" 能不能被综合呢,为什么书上的说可以,但是在quatus里面却提示不能,是不是不同的综合工具对这种综合的支持还不一样

2015-02-02 19:39:40

有谁来阐述一下机械装调技术综合实训装置有哪些特点吗?

2021-07-11 07:13:28

步进伺服控制综合实训平台是什么?步进伺服控制综合实训平台有哪些功能?

2021-09-26 06:59:33

手工综合RTL级代码的理论依据和实用方法时序逻辑综合的实现方法

2021-04-08 06:06:35

设置约束条件来优化设计,以达到设计要求的。(二)可选择的逻辑综合方案在优化电路时用户可以有两种方案,一种是自底向上的综合方案,一种是自顶向下的综合方案。2.1 自顶向下的综合方案(top-down)在

2013-05-16 20:02:50

物理综合与优化的优点有哪些物理综合与优化流程看了就知道物理综合与优化示例

2021-04-08 06:18:15

电机综合保护器的工作原理是经典的电机星三角启动方式主要是保护热继电器。采用电机综合保护器来实现对大型电机的保护,可以减少大电线的断点,从而减少发热点和故障点,且价格便宜。

2019-11-01 09:02:13

感觉自从使用纯非阻塞赋值实现各种接口后,综合快了很多,而且资源占用也少了

2020-06-11 10:22:35

自助银行联网综合智能视频监控系统的要点是什么?自助银行联网综合智能视频监控系统有什么功能?

2021-06-03 06:58:53

西诺S2315综合治疗机常用功能设置方法是什么?西诺S2315综合治疗机常见故障有哪些?

2021-11-15 07:43:21

请教原子哥有综合实验代码的详解讲解吗?万分感激!

2019-07-18 00:39:30

各位大神(包括原子哥):你们好,小弟最近想开发一个小项目,但是不知道界面是用什么怎么开发的?以前以为综合测试的界面的UCGUI开发的。就去搞了几天的UCGUI,可是今天发现MINI版综合测试的界面

2019-04-14 22:17:15

物理综合与优化的优点是什么?物理综合与优化有哪些流程?物理综合与优化有哪些示例?为什么要通过物理综合与优化去提升设计性能?如何通过物理综合与优化去提升设计性能?

2021-04-14 06:52:32

高层次综合技术原理浅析

2021-02-01 06:04:00

如何保证RTL设计与综合后网表的一致性文章简介:在超大规模数字集成电路的设计中,我们使用逻辑综合工具来完成从RTL设计到门级网表的转化。我们希望它综合出的门级网表

2009-01-23 23:10:52 19

19 Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 设计编译器(Design Compiler)和设计分析器(Design Analyzer) Design Compiler(DC) 是Synopsys逻辑综合工具的命令行接口

2009-11-19 13:32:16 57

57 介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。关键词:电子设计自动化 可编程逻辑

2010-07-18 10:38:50 22

22 介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词 电子设计自动化 可编程逻辑

2009-06-16 08:55:30 395

395

摘 要:介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词:电

2009-06-20 12:06:06 579

579

Synplify /Synplify Pro简介 综合工具在FPGA的设计中非常重要,类似于C语言的编译器将C语言翻译成机器能执行的代码,综合工具将HDL描述的语句转换为EDA工具可以识别的格式(EDF格式),对

2011-03-30 10:15:27 163

163 芯片综合的过程:芯片的规格说明,芯片设计的划分,预布局,RTL 逻辑单元的综合,各逻辑单元的集成,测试,布局规划,布局布线,最终验证等步骤。设计流程与思想概述:一个设计

2011-12-29 16:28:35 25

25 本文简单探讨了verilog HDL设计中的可综合性问题,适合HDL初学者阅读 用组合逻辑实现的电路和用时序逻辑实现的 电路要分配到不同的进程中。 不要使用枚举类型的属性。 Integer应加范围

2012-01-17 11:17:03 0

0 逻辑综合带来了数字设计行业的革命,有效地提高了生产率,减少了设计周期时间。在手动转换设计的年代,设计过程受到诸多限制,结更容易带来人为的错误。而一个小小的错误就导

2012-06-25 15:21:14 44

44 第1章-EDA设计导论 第2章-可编程逻辑器件设计方法 第3章-VHDL语言基础 第4章-数字逻辑单元设计 第5章-VHDL高级设计技术 第6章-基于HDL和原理图的设计输入 第7章-设计综合和行为仿真 第8章

2012-09-18 11:35:36 550

550 基于FPGA的EDA综合实验系统设计_赵刚

2017-03-19 11:38:26 2

2 本文档的主要内容详细介绍的是ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明包括了:1、逻辑综合基本概念 a) Synopsys综合工具及相关工具 b) 逻辑综合

2019-10-23 08:00:00 5

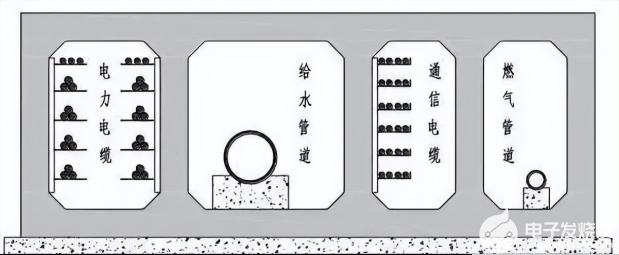

5 综合管廊(日本称“共同沟”、中国台湾称“共同管道”),就是地下城市管道综合走廊,即在城市地下建造一个隧道空间,将电力、通信,燃气、供热、给排水等各种工程管线集于一体,设有专门的检修口、吊装口和监测

2022-06-27 10:27:32 1361

1361

逻辑综合(Logic Synth.)过程需要约束(Stat. Wire Model)以产生规定条件下的电路。具体电路设计完成后,需进行门级仿真(Gate-Lev.Sim),以检查电路设计是否出现失误。

2022-08-12 15:06:43 4149

4149 逻辑综合操作(Compile design),根据芯片的复杂程度,逻辑综合操作的时间可能是几秒,也可能是半个月。如果设计环境和约束设置不当,逻辑综合操作的时间会被延长。

2022-08-12 15:10:21 3396

3396 执行算法逻辑(加、减、乘、除及复杂的组合运算)优化。例如,乘法器有多种实现方式, 相应地会产生多种时序、功耗及面积,如何根据目标设定选出最合适的结构将对最后的综合结果有重大影响。

2022-08-24 14:51:13 967

967 随着互联网的普及,综合布线技术越来越广泛,在布线中,配线架也成为大家比较常见的设备,为了满足各类需求,越来越多类型涌现出来,下面,科兰通讯小编为大家分享综合布线中配线架常用的类型。

2022-09-21 10:19:38 4833

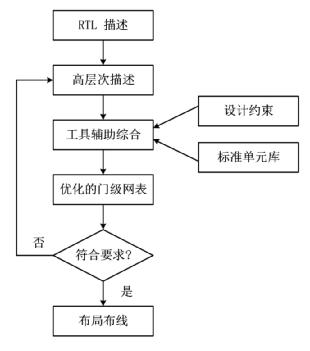

4833 利用工具将RTL代码转化为门级网表的过程称为逻辑综合。综合一个设计的过程,从读取RTL代码开始,通过时序约束关系,映射产生一个门级网表。

2022-11-28 16:02:11 1822

1822 综合,就是在标准单元库和特定的设计约束基础上,把数字设计的高层次描述转换为优化的门级网表的过程。标准单元库对应工艺库,可以包含简单的与门、非门等基本逻辑门单元,也可以包含特殊的宏单元,例如乘法器、特殊的时钟触发器等。设计约束一般包括时序、负载、面积、功耗等方面的约束。

2023-03-30 11:45:49 556

556

is What Statements) 根据综合理论的发展和HDL语言的发展,西方理论界提出综合友好的概念,即EDA的工程师,必须知道代码的综合意义。与西方科学技术体系的“形式

2023-05-11 20:17:26 321

321 逻辑综合是电子设计自动化(EDA)中的一个重要步骤,用于将高级语言或硬件描述语言(HDL)表示的电路描述转换为门级电路的过程。

2023-06-19 17:06:01 1936

1936 综合就是将HDL语言转化成与,非,或门等等基本逻辑单元组成的门级连接。因此,可综合语句就是能够通过EDA工具自动转化成硬件逻辑的语句。

2023-06-28 10:39:46 784

784 随着互联网的普及,综合布线技术越来越广泛,在布线中,配线架也成为大家比较常见的设备,为了满足各类需求,越来越多类型涌现出来,下面,科兰通讯小编为大家分享综合布线中配线架常用的类型。 综合布线中配线架

2023-08-29 10:17:36 636

636 逻辑综合是将RTL描述的电路转换成门级描述的电路,将HDL语言描述的电路转换为性能、面积和时序等因素约束下的门级电路网表。

2023-09-15 15:22:52 1914

1914

电子发烧友App

电子发烧友App

评论