时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1283

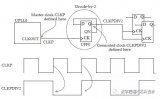

1283 时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3点。

2023-03-16 09:17:22 1433

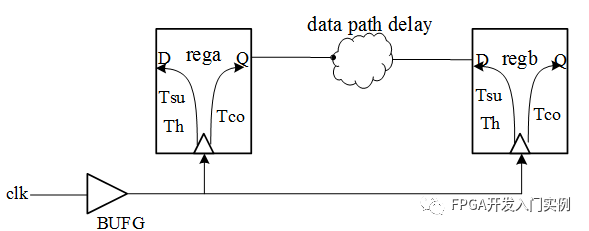

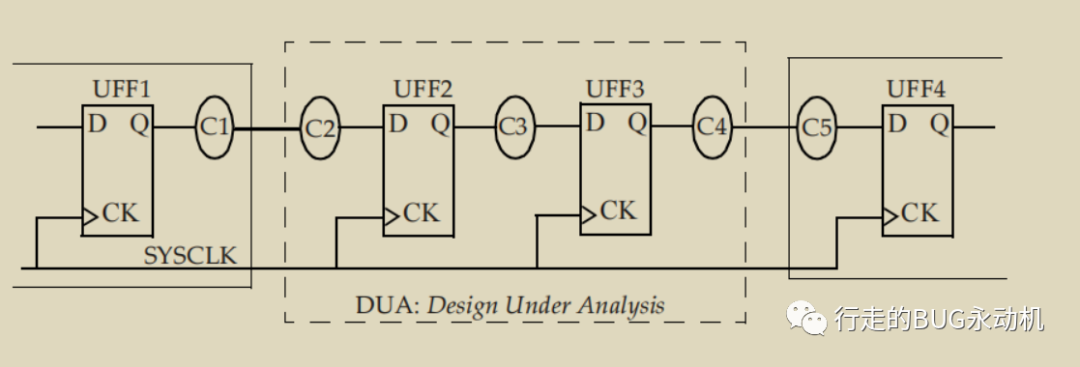

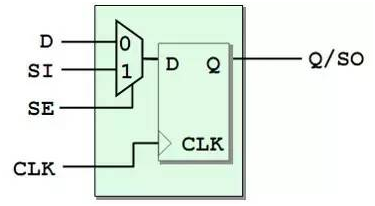

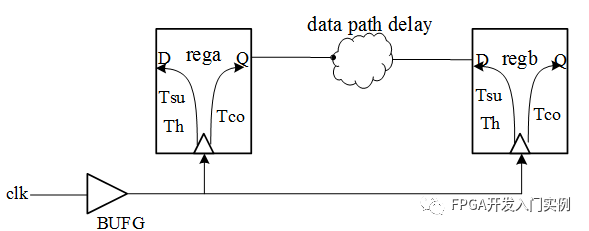

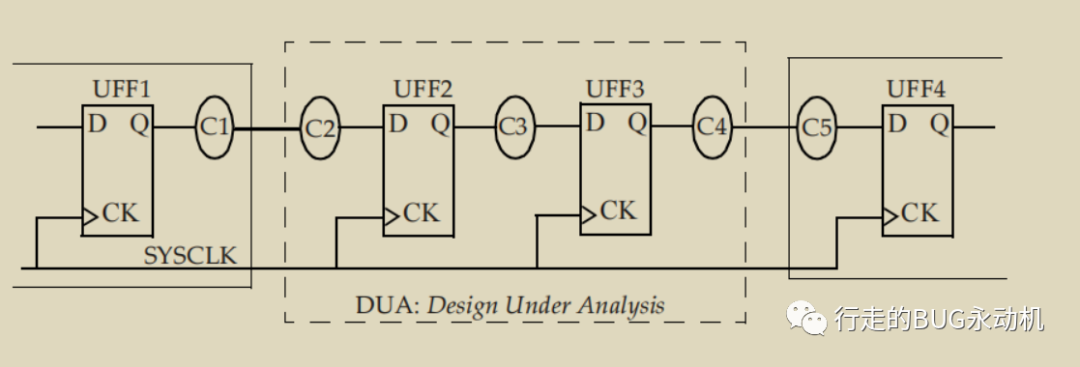

1433 下图是一个经典时序分析模型,无论寄存器A与寄存器B是否在同一个芯片中,下列概念均适用。

2023-07-03 15:37:08 656

656

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。 电路中的建立时间和保持时间其实跟生活中的红绿灯很像

2022-11-15 15:19:27

今天我们要介绍的概念是fanin,扇入。是指单个逻辑门的输入的数量;如下图为一个fanin为3 的与门;需要注意的是,在STA中,我们不允许出现多个输出单元同时驱动一个输入pin的情况,...

2021-07-29 06:34:09

在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序

2020-08-16 07:25:02

FPGA中几个基本的重要的时序分析参数介绍(fmax\tsu\th\tco\tpd)今天无聊,翻开书偶看到介绍时序部分的东西,觉得其中几个参数缩写所代表的含义应该记住,故写如下文章……FPGA中

2012-04-09 09:41:41

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

: 所设计系统的稳定情况下的最高时钟频率所设计系统的稳定情况下的最高时钟频率,他是时序分析中最重要的指标,综合表现所设计时序的性能首先介绍最小时钟周期TclkTclk = 寄存器的时钟输出延时Tco

2018-07-03 02:11:23

: 所设计系统的稳定情况下的最高时钟频率所设计系统的稳定情况下的最高时钟频率,他是时序分析中最重要的指标,综合表现所设计时序的性能首先介绍最小时钟周期TclkTclk = 寄存器的时钟输出延时Tco

2018-07-09 09:16:13

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

LED电源最重要的要求是什么,谁能解答一下,谢谢各位

2016-06-20 22:08:28

startup.s启动文件的启动代码最重要的工作是什么?

2021-11-29 07:00:45

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

QE有关的几个重要概念5、感光过程6、读取过程7、Sensor动态范围8、Sensor时序9、Noise in Sensor10、Crosstalk对 noise的影响1、Cmos sensor stack (以手机相机为例) ...

2021-09-15 07:08:17

人生最重要的文章

2012-07-28 17:22:11

——俞敏洪在2011寻访“大学生自强之星”活动启动仪式上的讲话 人一辈子要活下去,什么对我们最重要?人一辈子想要活好,什么东西最重要? 有人说自由最重要,有人说梦想最重要

2012-07-16 17:19:44

MPEG-2标准简介以及数字电视功能分析关于传输流以及传输流中几个重要概念信道解复用器是什么原理?

2021-04-21 06:53:22

而做的修补工作,如填充一些dummy单元等。 上面7个步骤是Astro设计的基本流程,下面针对设计中的时序偏斜对第5部分时钟树综合进行重点分析。 时钟树综合是时序优化处理中最重要的一步。时钟树综合

2012-11-09 19:04:35

OCV介绍及实现方法 如何使用AOCV做STA分析

2021-02-01 07:54:49

的设计师们也开始更多地关注时序因素。本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。本文介绍了时间抖动(jitter)的概念及其分析方法

2019-06-04 07:16:09

示波器衡量指标中至关重要但常被忽略的两个概念是什么?

2021-05-12 06:49:05

请问你觉得一生中什么对你最重要?

2012-11-18 21:31:26

静态时序分析(Static Timing Analysis,STA)是流程成功的关键环节,验证设计在时序上的正确性。STA过程中设计环境和时序约束的设定、时序结果的分析和问题解决都需要设计工程师具有

2020-09-01 16:51:01

静态时序分析STA是什么?静态时序分析STA的优点以及缺点分别有哪些呢?

2021-11-02 07:51:00

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 Ambit BuildGates在高速ASIC设计中的STA应用概论在复杂的深亚微米超大规模集成电路设计中,如何尽快地满足静态时序分析(Static Timing Analysis)是众多的设计公司需要面对的棘

2010-06-18 16:35:31 15

15 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

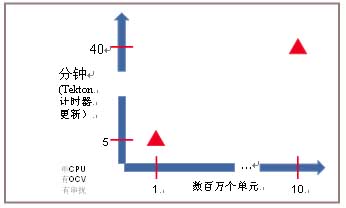

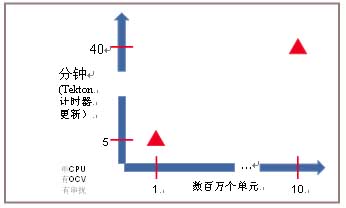

作为下一代STA工具,Tekton提供了突破性的单CPU多模/多角性分析性能,能够在几分钟内为上千万单元级的电路提供时序更新。同时,它还完全支持串扰分析和AOCV分析,并且内嵌

2010-12-14 11:54:14 2468

2468

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

时序分析基本概念介绍——STA概述,动态时序分析,主要是通过输入向量作为激励,来验证整个设计的时序功能。动态时序分析的精确与否取决于输入激励的覆盖率,它最大的缺点就是速度非常慢,通常百万门的设计想全部覆盖测试的话,时间就是按月来计算了。

2017-12-14 17:01:32 27851

27851

时序分析基本概念介绍——时序库Lib。用于描述物理单元的时序和功耗信息的重要库文件。lib库是最基本的时序库,通常文件很大,分为两个部分。

2017-12-15 17:11:43 10427

10427

时序分析基本概念介绍——Timing Arc

2018-01-02 09:29:04 23486

23486

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

2018-04-03 15:56:16 10

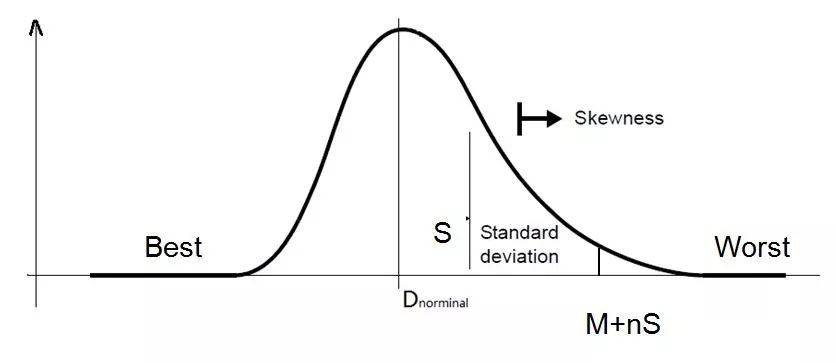

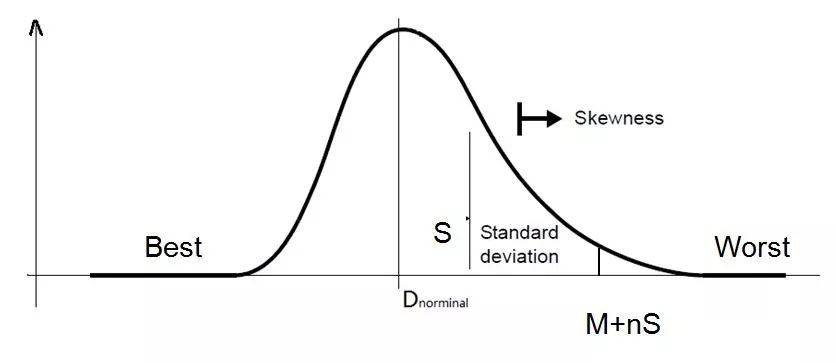

10 但实际芯片的PVT永远不会落在一个点上,而是一个范围;比如说有时序关系的几个cell,可能这几个cell的PVT是1.18V,20℃,工艺0.98。而那个cell的PVT是1.21V,35℃,工艺1.01。这些cell的PVT都不在那个点上,怎么去分析呢?这时候就需要OCV了。

2018-06-25 14:19:13 36173

36173

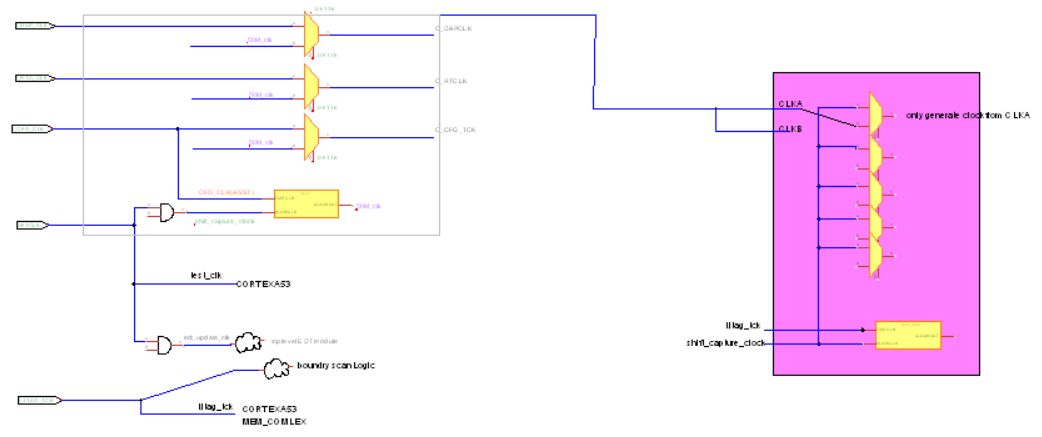

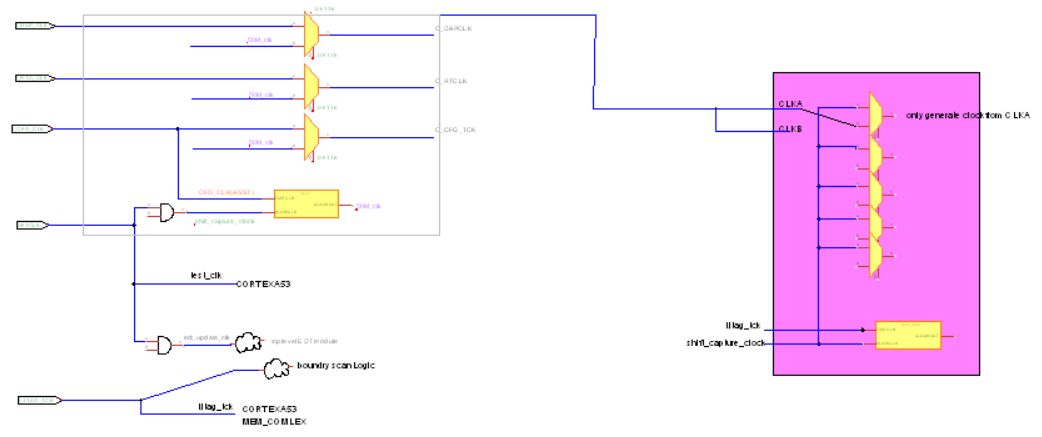

今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念。

2018-09-24 08:12:00 7990

7990

今天我们要介绍的时序分析概念是ETM。全称extracted timing model。这是在层次化设计中必须要使用的一个时序模型文件。由block owner产生,在顶层设计使用。

2018-09-24 19:30:00 16300

16300

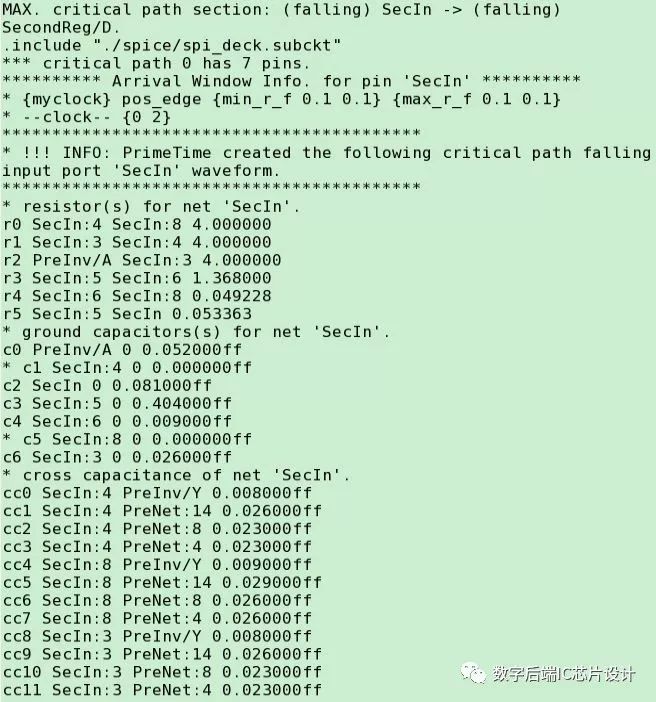

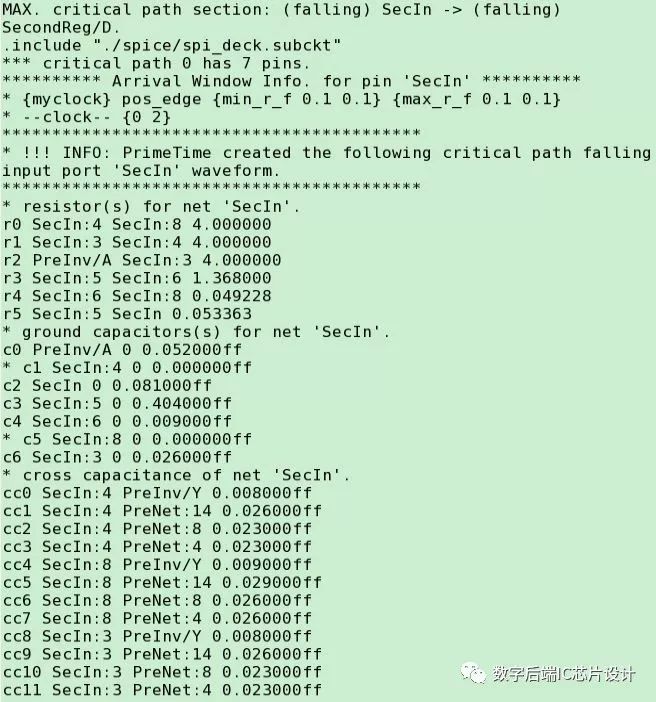

平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。我们平时使用PT做得是gate level的时序分析,如果想做transistor level的时序分析,那可以采用HSPICE做电路仿真。

2018-09-23 16:52:00 6170

6170 时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 5787

5787

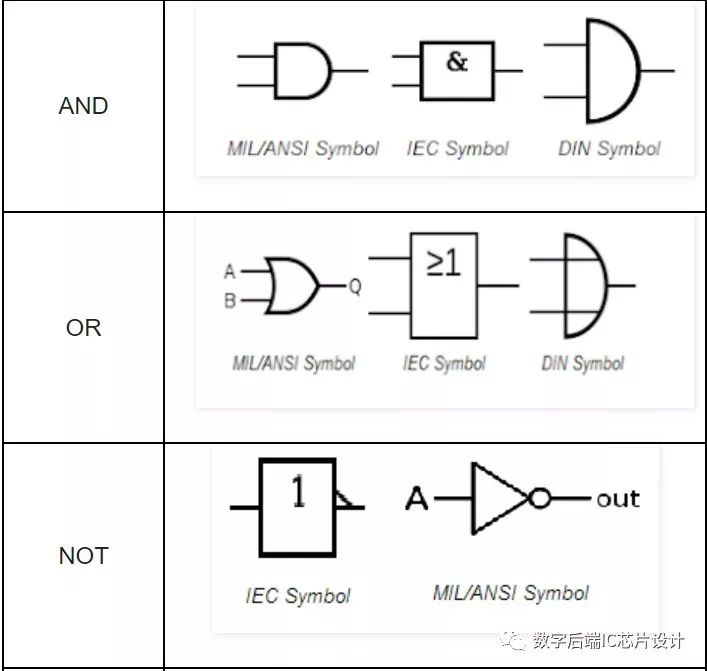

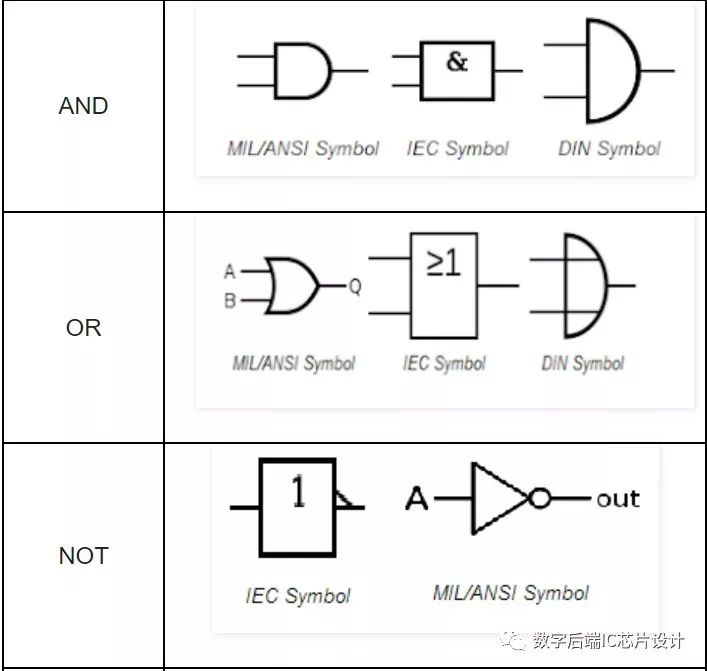

今天我们要介绍的时序分析概念是Combinational logic. 中文名组合逻辑单元。这是逻辑单元的基本组成器件。比如我们常见的and, or, not, nand,nor等门电路。

2019-05-14 17:27:07 5391

5391

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:02:00 4100

4100

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 1894

1894

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

2019-09-01 10:45:27 2942

2942

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。本文将力求以简单叙述及图例说明的方式,对STA的基础概念

2021-01-14 16:04:02 3

3 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 15

15 一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33:10 4768

4768

今天我们要介绍的时序分析基本概念是collection。代表的是一个集合,类似指针。在数字后端工具中,我们可以通过命令get_*来寻找想要的Object。这些get_*命令返回的就是collection。不同类型的object对应不同的get命令。

2021-11-26 10:30:18 3272

3272 今天我们要介绍的概念是fanin,扇入。是指单个逻辑门的输入的数量;如下图为一个fanin为3 的与门;需要注意的是,在STA中,我们不允许出现多个输出单元同时驱动一个输入pin的情况,也就

2021-11-26 10:27:35 4824

4824

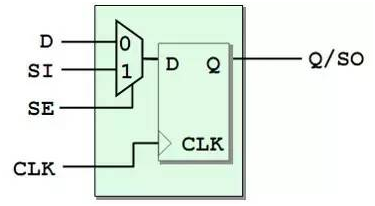

今天要介绍的时序分析概念是fanout。中文名是扇出。指的是指定pin或者port的输出端口数。 合理的选择fanout的数目对设计来说是非常重要的,fanout过大与过小都会对设计带来不利因素

2021-11-26 10:31:41 11753

11753

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45:13 1809

1809 前言 在上篇文章里《时序分析基本概念(一)——建立时间》,我们向大家介绍了建立时间的基本概念和计算方法。

2022-10-09 11:59:45 2696

2696 STA的准备工作包括:设定时钟、指定IO时序特性、指定false path和multicycle path

2023-05-26 17:20:40 718

718

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 372

372

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

静态时序分析(Static Timing Analysis, 以下统一简称 **STA** )是验证数字集成电路时序是否合格的一种方法,其中需要进行大量的数字计算,需要依靠工具进行,但是我们必须了解其中的原理。

2023-06-27 11:43:22 523

523

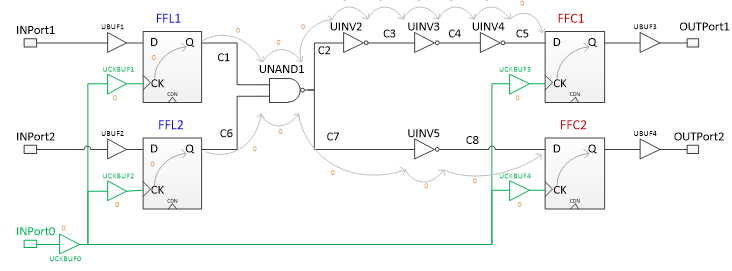

向量和动态仿真 。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。 时序路径 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最

2023-06-28 09:38:57 714

714

今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

2023-07-03 14:30:34 667

667

今天我们要介绍的时序概念是设计约束文件 **SDC** . 全称 ***Synopsys design constraints*** . SDC是一个设计中至关重要的一个文件。

2023-07-03 14:51:21 3874

3874

今天我们要介绍的时序分析概念是 **min pulse width** ,全称为最小脉冲宽度检查。这也是一种非常重要的timing arc check,经常用在时序器件或者memory上面。

2023-07-03 14:54:11 1198

1198

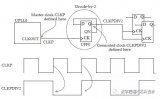

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。

2023-07-03 15:06:03 1484

1484

今天我们介绍的时序分析概念是 **SOCV** 。也被叫作POCV,全称为 **Statistic OCV** . 这是一种比AOCV更加先进的分析模式。

2023-07-03 15:19:00 1347

1347

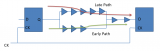

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们会给data path,clock path上设定单一的timing derate值。

2023-07-03 16:29:05 1164

1164

今天我们要介绍的时序分析概念是 **Operating Condition** 。也就是我们经常说的PVT环境,分别代表fabrication process variations(工艺变化参数), power supply voltage(电压)和temperature(温度)。

2023-07-04 10:57:12 1897

1897

本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 528

528

今天要介绍的时序分析基本概念是Latency, 时钟传播延迟。主要指从Clock源到时序组件Clock输入端的延迟时间。

2023-07-04 15:37:08 1313

1313

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角分析模式。这是在先进工艺下必须要使用的一种时序分析模式。

2023-07-04 15:40:13 1461

1461

今天要介绍的时序分析基本概念是skew,我们称为偏差。

2023-07-05 10:29:37 2120

2120

今天要介绍的时序分析基本概念是Slew,信号转换时间,也被称为transition time。

2023-07-05 14:50:53 1530

1530

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

静态时序分析(STA)是用来分析数字电路是否满足时序目标的技术手段之一。比如,检查CPU电路是否达到1GHz的目标频率。

2023-07-05 15:01:48 801

801

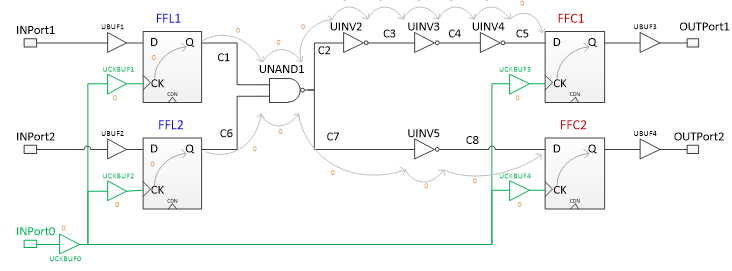

今天我们要介绍的时序分析概念是spice deck。平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。

2023-07-05 15:45:10 586

586

今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念。

2023-07-06 10:34:18 1234

1234

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1397

1397

本文将介绍低功耗系统在降低功耗的同时保持精度所涉及的时序因素和解决方案,以满足测量和监控应用的要求。

2023-07-11 16:14:54 374

374

今天我们要介绍的时序分析概念是Critical Path。全称是关键路径。

2023-07-07 11:27:17 663

663

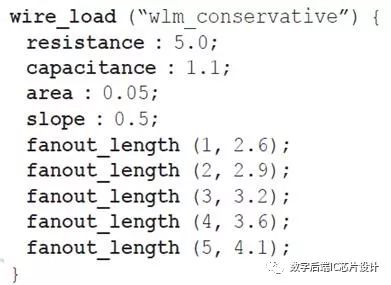

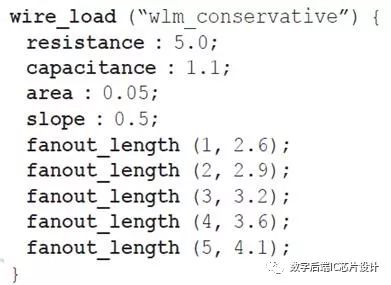

今天我们要介绍的时序分析基本概念是wire load model. 中文名称是线负载模型。是综合阶段用于估算互连线电阻电容的模型。

2023-07-07 14:17:11 541

541

今天我们介绍的时序分析基本概念是Virtual Clock,中文名称是虚拟时钟。

2023-07-07 16:52:55 744

744

今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

2023-07-07 17:15:00 1644

1644

今天我们要介绍的时序分析命令是uncertainty,简称时钟不确定性。

2023-07-07 17:23:46 1796

1796

今天我们要介绍的时序分析基本概念是ILM, 全称Interface Logic Model。是一种block的结构模型。

2023-07-07 17:26:32 2137

2137

今天我们要介绍的时序分析概念是Combinational logic. 中文名组合逻辑单元。这是逻辑单元的基本组成器件。

2023-07-10 14:31:26 475

475

今天要介绍的时序基本概念是Mode(模式). 这是Multiple Scenario环境下Sign off的一个重要概念。芯片的设计模式包括最基本的功能function模式,以及各种各样相关的测试模式。

2023-07-10 17:21:38 1718

1718

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

2023-08-08 10:31:44 525

525

STA同步热分析仪是将热重分析仪TG与差示扫描量热仪DSC或差热分析仪DTA结合一体,在同一次测量中利用同一个样品,可同时得到质量变化和吸放热变化等信息,大大提高了实验的效率,因此,被广泛应用在很多

2023-08-15 10:54:38 318

318

电子发烧友App

电子发烧友App

评论