作者为 刘于苇副主分析师。

要支持3DIC、Chiplet的Die-to-Die互联和异构集成,需要什么样的IP和EDA工具支持?物联网边缘计算成为趋势,需要什么样的处理器?地缘政治环境下,RISC-V开源架构的生态要如何继续发展?随着人工智能、机器学习技术的发展,本土EDA和IP企业如何借势突破,加速融入集成电路产业链和价值链?

随着全球集成电路行业整体的景气度的提升,IC设计市场也保持着快速发展的趋势。随着先进工艺节点不断演进,晶体管尺寸在不断逼近物理极限;而以ChatGPT为代表的语言大模型对芯片算力的要求不断上涨,也在刺激着AI芯片用Chiplet等更先进的封装来突破摩尔定律,实现更优PPA。

于是后摩尔时代对处于IC设计上游的EDA和IP,提出了更高的要求。要支持3DIC、Chiplet的Die-to-Die互联和异构集成,需要什么样的IP和EDA工具支持?物联网边缘计算成为趋势,需要什么样的处理器?地缘政治环境下,RISC-V开源架构的生态要如何继续发展?随着人工智能、机器学习技术的发展,本土EDA和IP企业如何借势突破,加速融入集成电路产业链和价值链?

带着这些业界难题,ASPENCORE在日前举办的国际集成电路展览会暨研讨会(IIC Shenzhen 2023)上,同期举办了一场“EDA/IP与IC设计论坛”,邀请到来自Cadence、安谋科技、Imagination、芯和半导体、奎芯科技、灿芯半导体、芯来科技等业内先进企业的嘉宾,就上述问题展开讨论,出谋划策,共同助推产业创新发展。

适用大模型AI芯片的接口IP

近年来AI技术的发展十分迅猛,以ChatGPT为代表的生成式AI应用,无论是逻辑还是语言各方面都达到甚至超过了很多人类的认知水平。对于AI的发展,有人恐慌,有人则认为这是科技发展的客观规律。Cadence技术支持总监 李志勇认为,应该用更积极的态度拥抱AI,利用好这个工具去做一些重复性的工作,效果比人工来的更好,在一些复杂的场景下,使用AI可以协助人类提高生产率。

当前,AI芯片需求不断增长。过去数据中心最常用的是GPU,但随着语言大模型对算力需求各方面的增长,业界开始倾向使用针对某类应用的专用ASIC。据Bloomberg统计,未来10年专用ASIC的CAGR将达到33%,这个产业也将从37亿美金增长到641亿美金。

李志勇详细介绍了AI应用于Cloud、Edge、Endpoints等不同领域时,对于GDDR6、DDR5、HBM2E等内存IP的不同需求。例如DDR适合服务器等对大容量有要求的应用;LPDDR主要用于移动设备、ADAS等对功耗要求更高的应用;GDDR主要满足带宽、成本、可靠性的要求;而对于更高容量的要求,HBM能够提供最高的带宽。

另外AI芯片对PCIe、CXL、高速以太网和Chiplet Die-to-Die接口IP也有很大需求。 从Cadence的角度来看,一颗AI SoC就是一个智能系统,把这个智能系统放在终端产品里,要达到更好的用户体验、优化应用负载,兼容各种应用和平台,之间很多是互相矛盾的,但是需要尽量达到最好。

面向IoT,需要什么样的处理器?

随着IoT领域对设备算力的需求越来越高,当我们考虑未来的IoT芯片形态应该怎样发展时,算力是非常重要的点。但同时也要注意,IoT设备算力的提高,并不能以芯片的面积、功耗线性增加为代价。

“未来我们在具体的算力分割上,Arm希望一些颗粒度比较小的计算,可以用处理器上的矢量扩展(Helium tecnology)来实现;颗粒度比较大的计算场景,可以用一些专门的AIPU来计算。” 安谋科技产品总监 陈江杉 围绕万物互联时代对处理器的要求,介绍了安谋科技最新面相IoT的新一代处理器星辰STAR-MC2。

低功耗CPU需要考虑的基础原则是面向微控制器市场,所以星辰STAR-MC2在具体指令级选择上采用了Cortex-M系列。在低功耗设计方面,面积和功耗受限的情况下,CPU的中断、调试模块都可以跟处理器做进一步的集成。

“无论是软件还是生态系统,Arm不仅开放了完整的总线标准,也做了一些可靠的参考设计提供给芯片客户,甚至提供给这些生态的客户去开发。” 陈江杉说到。

做一款整个业界都可以遵循软件标准和通用接口开发的处理器,需要长年的积累,“设计这款处理器的初衷,也是希望跟之前的老处理器之间有一致性和延续性前提下,又进一步有技术的提高。”

基于上一代产品,安谋科技着眼于以下几个点布局新的产品形态。首先,通过新的指令级、新的扩展(包括矢量扩展),在不显著增加面积和功耗的前提下,可以增加计算密度来满足越来越高的计算需求;同时,在v8架构下引入TrustZone信息,允许设备敏感信息运行在平台上,这里面包含更强的内存管理单元,也包括一些软件栈检查的功能,更好地保证整个计算平台的信息安全;最后,国内汽车工业对基于ISO 26262或ISO 61508标准的可靠性有一定要求,所以安谋科技也做了完整的一套功能安全的设计,并且已经通过了业界最高的车规认证。

Imagination在RISC-V 上的布局

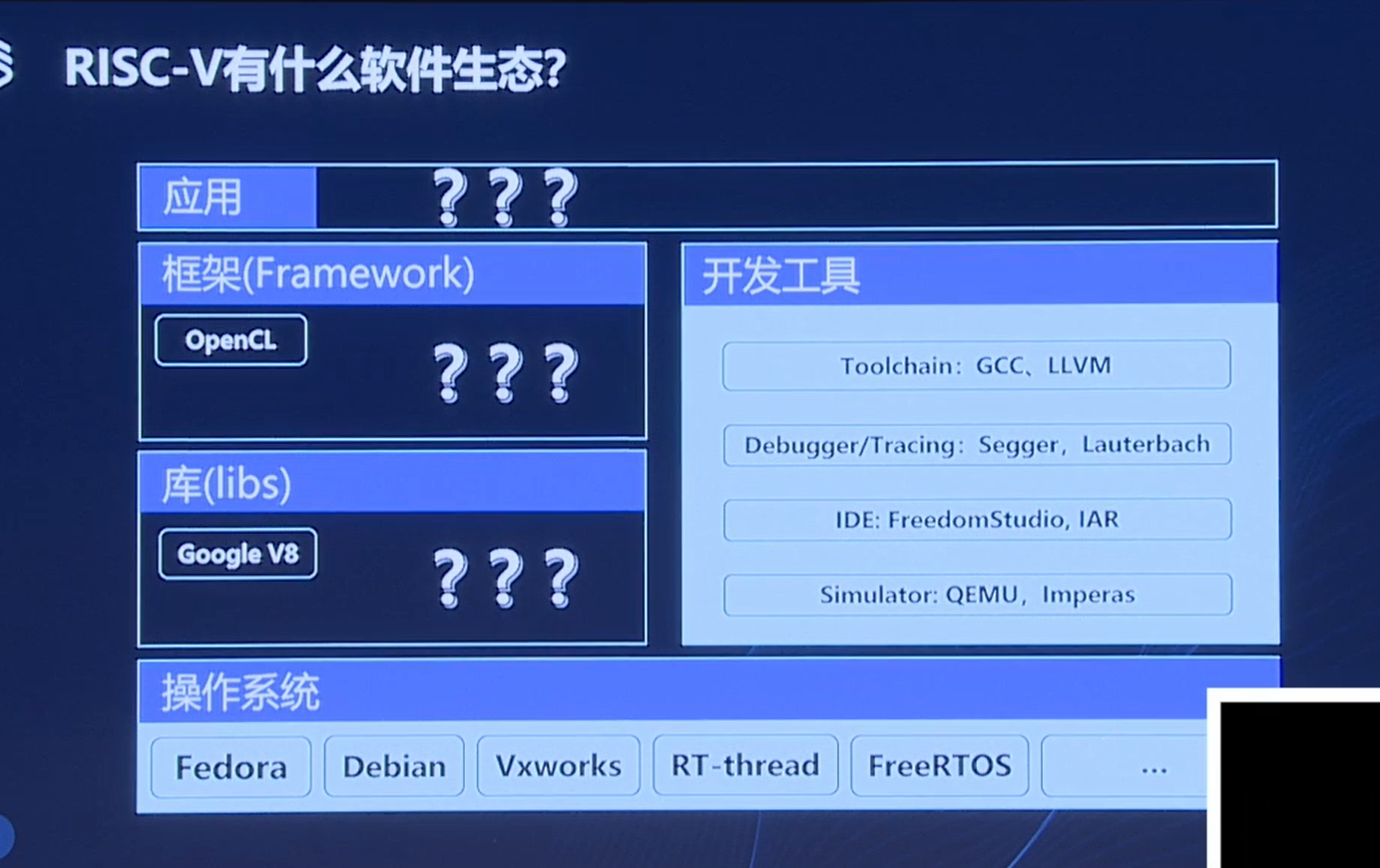

为什么现在RISC-V这么火?首先,RISC-V是一个基于开源的指令集架构,它在全球有非常多的开发者以及生态伙伴,而RISC-V国际基金会是一个总部在瑞士的中立机构,不受任何单一国家或公司控制。目前已经有非常多商业公司、研究院所和高校进入这个领域,生态上也有Linux、Android以及国产的统信、麒麟等表示支持 RISC-V。

“虽说RISC-V架构是开源可授权的,但并不是说它是免费的,各家公司之间产生竞争才会有创新。所以随着越来越多玩家加入RISC-V产业,开发者们在社区贡献自己的力量,就会推动它不断创新,这就是RISC-V的魅力。” Imagination市场及业务发展高级经理 黄音 介绍了公司在RISC-V领域的产品方向和布局。

Imagination有四大产品方向,分别是移动领域、消费电子领域、汽车领域和PC 与数据中心。说到选择RISC-V的原因,黄音表示,首先Imagination是传统的IP供应商,在IP的授权、支持、售后上有自己的优势和经验;第二,无论CPU/GPU/NPU都是复杂的IP,需要的大量经验正好是Imagination具备的;第三,Imagination之前旗下的MIPS虽然已经剥离出来,但仍然可以永久使用其的专利;第四,Imagination在售后支持上有专业的团队和多年沉淀。

黄音表示,Imagination非常早期就成为了RISC-V国际基金会的会员,也有成员在董事会、技术委员任职。“在汽车、浮点运算、安卓、功能安全、信息安全等不同的细分小组里也有人任职,这些领域专家都在为RISC-V的整个生态做贡献。”今年刚成立的RISE组织是RISC-V基金会中单独成立做软件生态的,Imagination也是创始成员之一,RISE将对RISC-V生态扩展起到非常大的作用。

EDA使能3DIC Chiplet先进封装设计

EDA处于半导体行业中最前端的环节,相当于整个生态的支点,用类似杠杆的方式支撑了后面IP、晶圆制造、封测以及电子系统应用的整个市场规模。

“最近两年Chiplet很火,也是每次行业大会讨论最多的热点议题。我将Chiplet理解为一种设计理念,其背后的支撑技术实际是先进封装能力。”芯和半导体技术市场总监 黄晓波 首先介绍Chiplet的起源和兴起的背景及驱动力,随后从Chiplet实现的关键技术展开,谈到了芯和半导体针对Chiplet设计挑战的一站式EDA解决方案,助力产业发展。

在过去50多年,摩尔定律长期牵引着整个半导体行业的发展,如今由于先进工艺制程升级变缓,研发成本高昂,无法像过去那样每18~24个月带动晶体管集成的数量翻倍,导致半导体性能提升面临瓶颈。不过好在先进封装仍在持续演进,从1970年的MCM到SiP,再到2.5D和现在的3DIC、异构集成,先进封装技术为半导体行业的突破打开了另一扇大门。

Chiplet实现的关键技术包括Die-to-Die互连、先进封装3D异构集成以及全新的设计流程和EDA工具。“芯和半导体提供一站式3DIC Chiplet EDA多物理场仿真平台,从信号完整性、电源完整性、多物理场分析及系统验证等维度支撑Chiplet设计的实现与落地,目前已经被国际领先的算力芯片设计公司选购采用,成功验证了该方案对Chiplet先进封装工艺、接口协议标准、数据格式兼容和典型互连结构的全面支持,希望与产业链上下游伙伴共建共享Chiplet发展的繁荣生态。” 黄晓波说到。

实现边缘计算Chiplet互联的关键IP

近年来大量公司涌入AI领域展开布局,虽然ChatGPT一类的大模型很火,但巨大的投入也让大部分公司望而却步,边缘AI计算是一个更大众的选择方向。据市场机构预测,到2024年,边缘AI芯片的增长速度会超过整体的芯片市场。

“不过现在AI SoC对算力的要求越来越高,设计难度也就越来越大。唯一的解决办法是通过Die-to-Die互联,把I/O部分放到旁边,再通过主Die接口访问I/O Die,实现数据之间的交互。” 奎芯科技资深产品经理 王尚元 强调,多Die也会带来一些问题,比如封装良率降低带来的成本问题,只能通过把Die做小来分摊成本,“所以现在AI算力的瓶颈就被卡在互联跟内存上。”

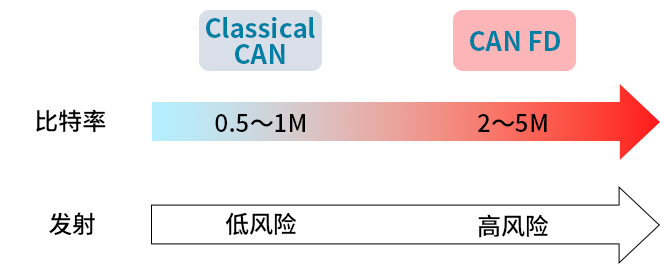

在这两个卡脖子的地方,奎芯科技作为IP厂商,在互联方面推出了PCIe,在内存接口上推出了LPDDR。王尚元首先介绍了AI芯片目前对内存的选择,无非是LPDDR4X/5X、GDDR6、HBM2E/3这几种解决方案,“从带宽、容量、功耗、颗粒成本等方面比较来看,GDDR6带宽对AI推理是最理想的,而DDR在做训练、电源管理、动态功耗的动态频点切换时不可缺少。”

据介绍,奎芯科技的LPDDR PHY具有高适配、低延时、低功耗、易扩展、高可靠5大优势。同时在做训练时,这款LPDDR PHY内部的独立Training机制可以通过不同的场景,做快速训练,并且可适配不同厂家、不同型号的颗粒。

同时为了增加互联的带宽,奎芯科技符合UCIe标准的接口IP支持Chiplet中计算和存储小芯片之间互联,还可以把I/O小芯片单独放出去,在小芯片跟I/O之间做互联。由于UCIe是开放的、支持多协议的封装内互联标准,所以在通用物理层和链接层之上支持多种协议,不需要做协议转换。

打造国产一站式IP与SoC设计服务平台

灿芯半导体主要为客户提供IP和IC设计服务,IP方面包括模拟类IP和高速接口IP,设计服务专注于ASIC和SoC设计服务平台,SoC方面主要专注在65nm以下的工艺节点,以及65nm以上的高性能模拟类IP的设计。五大块主营业务包括:1、为客户提供芯片全定制服务;2、芯片工程定制服务;3、SoC系统设计平台;4、IP定制化及整体解决方案;5、作为ASIC生态系统的重要组成部分。

灿芯半导体IP项目总监 饶青重点介绍了公司高速接口IP的主要性能和指标。 接口IPYouDDR目前经过硅验证,最高速率达到4266Mbps;YouSerdes系列最高速率可到32Gbps,支持包括PCIe、USB3.1/3.0、SATA Gen 3.0/2.0/1.0等多种协议;PCIe PHY的IP可以向下兼容到PCIe1.0,支持16 LAN,具有低延迟和小面积的特点。此外还有YouUSB 2.0 OTG PHY IP、MIPI CSI2/DSI2接口解决方案、TCAM IP以及基于45/55nm开发的16bit 1~5Msps SAR ADC等产品。

在IC设计方面,灿芯半导体的IoT平台基于55nm工艺开发,使用ARM Cortex M系列平台。而基于ARM Cortex A系列核架构开发的AP解决方案,经过了40nm和28nm的工艺流片,“我们可以为客户提供整套软件套件,缩短客户SoC产品上市的时间。” 饶青说到,同时从客户端反馈来看,越来越多的客户基于国际环境及成本考虑,想把FPGA方案转成ASIC。“基于灿芯自有的SoC设计流程经验以及IP种类的储备,可以为客户提供比较完善的FPGA转化为ASIC的国产替代方案。”

RISC-V CPU IP助力国产芯

从内核到软件的沟通桥梁就是ISA。RISC-V为什么这么重要?因为在以前,从接口到通讯都有标准接口,唯独ISA层面没有标准,因为ISA属于Intel或ARM这样的单一公司。这极大影响了整个产业的能动性和发展。

最开始Intel的X86不做架构和IP授权,仅以芯片的形式开放。随后Arm虽然开启了IP和架构授权的形式,但这两家公司仍然对指令级的发展具有决定权。“后续一些小的架构在发展的过程中逐步消亡,也证明了如果不开放生态的话,就不会收获用户。” 芯来科技战略市场副总 李珏 表示,直到2013年以后RISC-V出现,才成为一个公开化的国际标准,在大家的关注下于2018年开始正式产业化。“正如倪光南院士所说,RISC-V会与x86、ARM呈三分天下之势,我们也拭目以待。”

李珏分享了公司成立五年来利用RISC-V开放架构,做自主可控的IP生态,以及和其他的IP、芯片公司合作,把RISC-V一步步在国内落地的经验。他认为在这几年支撑芯来成长的,是这几个关键词:

第一,RISC-V的天然基因:开放。因为开放了,才有软件、硬件、集成电路公司、EDA公司来支持RISC-V。

第二,繁荣。这个繁荣是从AIoT赛道起跑的,过去的PC时代和移动互联网时代都不可能给RISC-V这个机会,直到AIoT时代,RISC-V从边缘AI、IoT设备、IoT芯片出发,才开始让大家从接受RISC-V,到在高算力AI芯片中尝试使用RISC-V。

第三,自主。从国际形势来看,有一个自主可控的、不受外国公司制约的指令集,对我们开发使用自己应用、赋能的CPU IP产业来说有极大的促进作用。

“从整个RISC-V的生态来说,芯来科技是一家中立的IP商,我们希望在产业里为大家提供更多的价值。” 李珏说到,五年来芯来推出了2369的完整系列,可以对标ARM从M0一直到A55、A53级别的各种CPU,还可以做差异化功能。拥有国际上第一个完成ISO 26262 ASIL-D产品认证的RISC-V CPU IP,也是国内第一家CPU IP公司获得ASIL D的认证。

编辑:黄飞

电子发烧友App

电子发烧友App

评论