非易失性存储器 (NVM) 在几乎所有嵌入式系统设计中都起着关键作用,但许多设计对非易失性存储器在数据写入和访问速度、数据保留、低功耗等方面的要求越来越严格。在汽车应用中更是如此,设计人员正在努力打造更先进的功能,例如高级辅助驾驶系统 (ADAS) 这类任务关键型功能。

为确保这些系统安全可靠地运行,设计人员需要深入研究先进的铁电随机存取存储器 (F-RAM),作为要求可靠性高、功耗低且比当前 NVM 解决方案速度更快的低功耗汽车级 NVM 的选择。

本文讨论 F-RAM 技术的关键特性,并介绍开发人员如何使用 Cypress Semiconductor 的两款 F-RAM 解决方案来增强 ADAS 的可靠性,关注发烧友公众号回复资料和邮箱地址可以获取电子资料一份。并以 ADAS 为代理,将 F-RAM 的使用范围扩大至其他任务关键型应用。

汽车 NVM 要求

汽车行业不断集成具有更高分辨率和更快更新速率的更先进传感器,汽车安全应用则是这种行业趋势的缩影。ADAS、电子控制单元 (ECU) 和事件数据记录仪 (EDR) 等汽车子系统的持续发展,并高度依赖于从各种传感器收集到的大量数据。任何数据丢失,甚至数据访问速度的滞缓,都有可能危及系统安全、车辆和乘客。

例如,在 ADAS 设计中,写入电可擦除可编程只读存储器 (EEPROM) 所需的时间可能会引入灾难性的延迟时间,导致旨在避免检测到的危险情况的自动操作功能反应迟缓。在 EDR 设计中,如果车辆事故引发电源故障,那么写入速度缓慢可能导致关键传感器数据丢失,致使了解事故根本原因所需的数据消于无形。

F-RAM NVM 特性

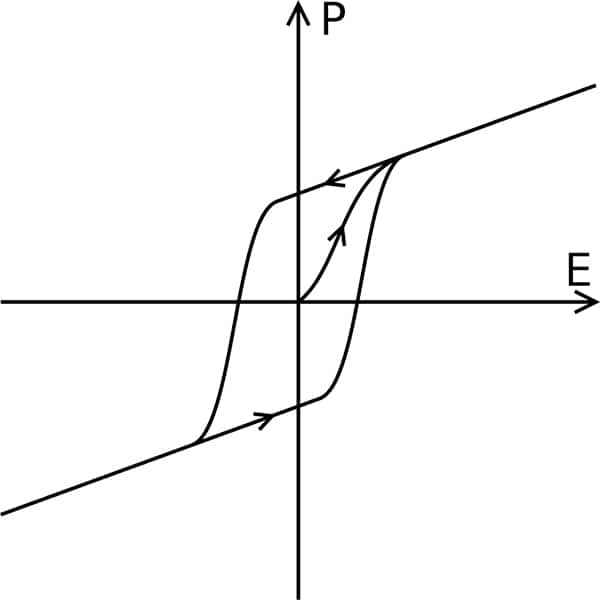

采用 F-RAM 技术构建的存储器件可以有效地替代 NVM,满足在可靠数据存储和高速访问方面日益增长的需求和性能要求。此类器件由锆钛酸铅(Pb[ZrxTi1−x]O3,简称为 PZT)制成。PZT 具有独特的性质,施加电场后,PZT 晶体中嵌入的金属空位(阳离子)依据电场方向获得两种可能极化状态(向上或向下)中的一种(图 1)。

图 1:F-RAM 技术利用了 PZT 材料在受到电场作用时表现出的两个同样稳定的能态。(图片来源:Cypress Semiconductor)

由于两者同是低能态,当移开电场时,阳离子将继续处于其最近的极化状态(图 2)。施加正或负电场时,阳离子将再次快速转变至适当的极化态,遵循与铁磁材料类似的特征磁滞回线。

图 2:PZT 材料遵循特征磁滞回线,响应施加的电场而在两个稳定的极化态之间切换。(图片来源:WikiMedia Commons/ CC-BY-SA-3.0)

F-RAM 技术的特性直接决定了采用该技术制造的 NVM 器件具有许多优点。两种 PZT 能态同样稳定,因而阳离子可数十年乃至数百年保持在其最后位置不变,使得基于 PZT 的 F-RAM NVM 器件具备前所未有的数据保留期限。此外,该技术基于阳离子位置,而不是其他 NVM 技术的电荷储存机制,因此 F-RAM 器件具备固有的辐射耐受性,不受电离辐射的单粒子翻转影响。

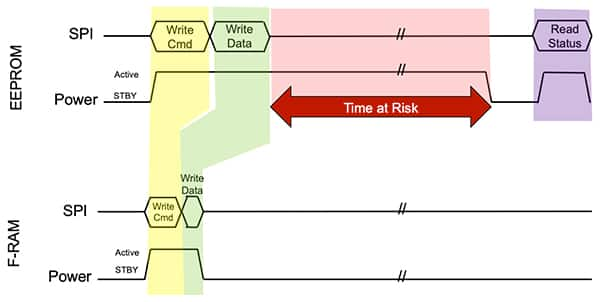

除了长期存储的优势之外,F-RAM 技术还增强了 NVM 器件的动态性能。状态转变非常迅速,并且只需很少的能量,克服了任务关键型应用中与使用 EEPROM 或闪存有关的根本限制。在相对较慢的写周期中,EEPROM 和闪存器件需要一个与数据缓冲有关的相当长“停留时间”(soak time)。写周期中的这种额外延迟会导致数据处于风险中,如果在操作完成并检查最终读取状态之前电源出现故障,数据可能会完全丢失(图 3)。

图 3:与 F-RAM 器件相比,EEPROM 或闪存写操作需要相当长的停留时间(红色突出显示部分),在此期间数据仍处于风险之中。(图片来源:Cypress Semiconductor)

为了应对 EEPROM 或闪存写周期较慢的问题,开发人员如果希望减轻电源故障的影响,就需要添加大电容或电池及适当的稳压器,使 NVM 电源电压维持足够长的时间以便完成写操作。相比之下,F-RAM(例如 Cypress Semiconductor 的 Excelon-Auto 器件)在写操作期间以总线速度工作,大大降低了关键数据丢失的可能性,而且无需在设计中使用补充电源。

汽车级 F-RAM 器件

Excelon™-Auto F-RAM 器件在功能上与串行 EEPROM 和串行闪存相似,旨在满足关键任务应用对可靠、高性能 NVM 的需求。汽车系统设计人员可以使用这些符合 AEC-Q100 标准的器件取代其他类型的存储器;有两种型号可供选择:CY15V102QN 采用 1.71 至 1.89 V 电压,CY15B102QN 采用 1.8 至 3.6 V 电压。两者都是 2 兆位 (Mb) 器件,采用 256 Kb x 8 逻辑组织结构。

在 -40°C 至 +125°C 的工作温度范围内,Excelon F-RAM 的数据保留期限远远超出其他 NVM 技术。例如,CY15x102QN 在 85°C 的温度下运行时可以保留数据大约 121 年。数据保留期限与温度成反比,如果被迫在典型发动机温度的较高一端运行(例如 95°C),则 F-RAM 的估计数据保留期限为 35 年。

在可靠性方面,F-RAM 的读/写周期耐久性为 1013,比典型 EEPROM 或闪存高出大约 7 个数量级。因此,使用此类 F-RAM 器件的开发人员不需要实施损耗均衡(将写操作分配到各扇区以解决其他 NVM 技术存在的写周期有限的问题)之类的技术。

采用 F-RAM 的简化设计

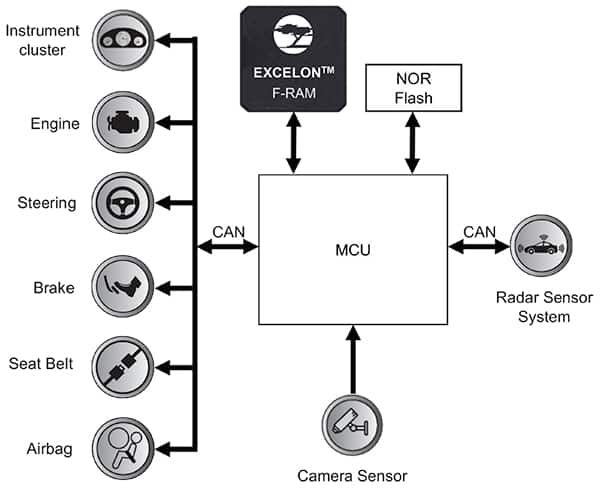

在典型设计中,开发人员可以使用此类器件直接替换或补充其他类型的 NVM 器件,例如 NOR 闪存。例如,在 ADAS 设计中,开发人员可以同时使用 NOR 闪存和 Excelon F-RAM,前者用于存储固件,后者则能可靠地处理来自许多汽车子系统(为 ADAS 应用提供输入)的多个数据流(图 4)。

图 4:汽车 ADAS 开发人员可以在基于微控制器 (MCU) 的设计中,将 Excelon F-RAM 器件(用于存储关键数据)与 NOR 闪存器件(常用于存储固件或配置数据)结合起来使用。(图片来源:Cypress Semiconductor)

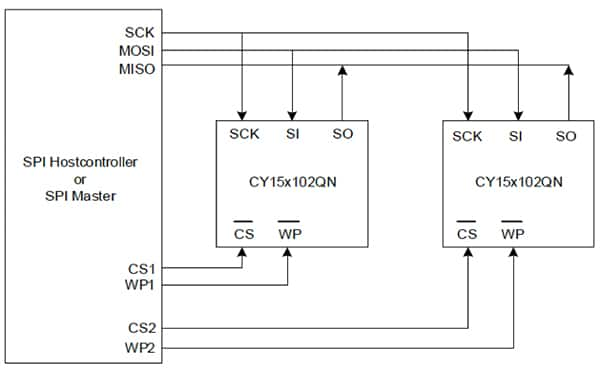

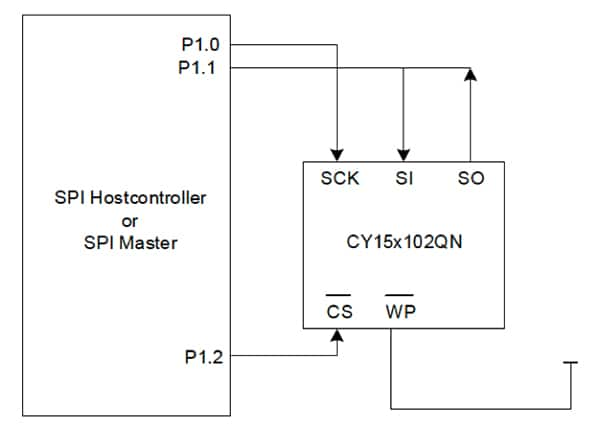

开发人员只需将 Excelon F-RAM 简单地连接到主机处理器的串行外设接口 (SPI) 总线,便可轻松将其加入设计。CY15x102QN F-RAM 设计用作 SPI 从器件,支持高达 50 兆赫兹 (MHz) 的 SPI 时钟速率。在典型硬件配置中,开发人员将 F-RAM 的串行输入 (SI) 和串行输出 (SO) 分别连接到 SPI 主控器的主输出从输入 (MOSI) 和主输入从输出 (MISO) 线。随后再连接到相应的串行时钟 (SCK) 和片选 (/CS) 线,便完成了硬件接口。开发人员可以将多个器件并用来共享主机的 SPI 总线(图 5)。

图 5:开发人员可以使用共享 SPI 总线将主机处理器与一个或多个 CY15x102QN F-RAM 连接起来。(图片来源:Cypress Semiconductor)

针对没有 SPI 功能的 MCU,CY15x102QN 器件支持一种简单的替代方案,即利用微控制器的通用 IO (GPIO) 来仿真 SPI 硬件接口,从而连接到 F-RAM。开发人员只需使用三个 GPIO 便能实现此接口,即 F-RAM 的 SI 和 SO 数据线使用同一引脚(图 6)。

图 6:针对没有原生 SPI 功能的微控制器,开发人员可以简单地使用微控制器的通用 IO 来仿真 SPI 协议,从而访问 CY15x102QN 串行 F-RAM。(图片来源:Cypress Semiconductor)

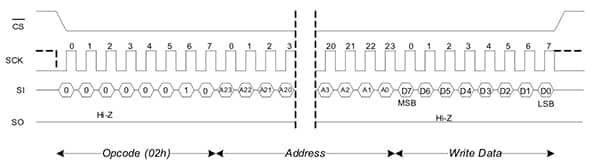

在标准 SPI 协议中,主器件通过拉低 /CS 来启动事务处理。在 /CS 变为低电平后,F-RAM 将下一个字节解释为操作码。例如,写操作对应的是 SPI 标准写操作码 (02h),加上三字节地址和一些数据字节(图 7)。

图 7:Cypress 的 CY15x102QN F-RAM 器件支持标准 SPI 操作码和协议,开发人员通过顺序发送写操作码 (02h)、地址和数据便可轻松执行零延迟写操作。(图片来源:Cypress Semiconductor)

对于 2 Mb CY15x102QN F-RAM,地址是一个三字节序列,忽略高六位。Cypress 建议将此高六位设置为零,以便将来能轻松过渡到更高容量的 F-RAM 器件。

读操作遵循相同的协议。接收到标准读操作码 (03h) 和地址后,F-RAM 器件通过 SO 顺序发送数据字节,自动递增存储器地址,同时 /CS 保持低电平,时钟信号继续产生。因此,开发人员可以执行批量读操作,只需让 /CS 保持低电平并继续发出 SCK 时钟信号,直到读取所需数量的数据字节为止。

CY15x102QN F-RAM 还支持与串行闪存兼容的快速读取功能。在快速读操作码 (0Bh) 和地址之后,SPI 主机发送一个伪字节来模拟闪存读取延时。接收到伪字节后,F-RAM 用所请求的数据作出响应。快速读取操作使用与标准读操作相同的机制,也能执行批量读操作。

写保护

除了 SPI 接口控制逻辑外,CY15x102QN F-RAM 还提供其他机制来识别器件并对 F-RAM 阵列进行写保护。

开发人员可以发出 SPI 操作码来访问 CY15x102QN 器件的只读唯一 ID 和器件 ID,获得制造商、存储器密度和零件版本等信息。开发人员还可以设置 8 字节读/写序列号寄存器,将 F-RAM 与特定系统或配置相关联。

关于 F-RAM 保护,该器件同时提供了软件和硬件机制。对于制造过程中的数据保护,有一个专用 256 字节特殊扇区可以在多达三个标准回流焊周期中保持数据完整性。对于正常工作期间的保护,器件使用写使能锁存器 (WEL) 来保护 F-RAM 阵列免于意外写入。上电时,WEL 默认清零,需要开发人员发出写使能 (WREN) 操作码 (06h) 才能执行写操作。

器件状态寄存器有一对块保护 (BP) 位 BP0 和 BP1,允许开发人员保护存储器的全部地址范围(BP1=1,BP0=1),或仅保护存储器的上半部分(BP1=1,BP0=0),或仅保护存储器的上部四分之一(BP1=0,BP0=1)。

开发人员可以使用硬件写保护引脚 (/WP) 来防止软件在正常工作期间修改 BP 位。为此,开发人员在状态寄存器中设置写保护使能 (WPEN) 位,并将 /WP 引脚置为低电平以锁定状态寄存器。

电源管理

以最高 50 MHz 时钟速率正常运行时,F-RAM 技术固有的高能效使得 CY15V102QN(VDD 1.71 至 1.89 V)的典型电流消耗仅为 5.0 毫安 (mA)。开发人员可以降低时钟频率以进一步节省功耗,CY15V102QN 在 1 MHz 时的电流消耗降至大约 0.4 mA。CY15B102QN(VDD 1.8 至 3.6 V)的电流消耗仅略高一点,50 MHz 时为 6.0 mA,1 MHz 时为 0.5 mA。

长时间不活动时,开发人员可以使用 SPI 操作码将 CY15x102QN 器件设置为如下三种低功耗模式中的一种,从而显著降低功耗:

- 待机模式,CY15V102QN 的典型电流消耗为 2.7 微安 (μA),CY15B102QN 为 3.2 μA

- 深度省电模式,CY15V102QN 为 1.1 μA,CY15B102QN 为 1.3 μA

- 休眠模式,两个器件均为 0.1 μA

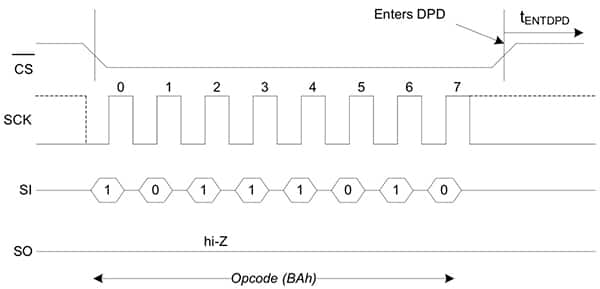

只要 SPI 主机在操作码序列结束时将 /CS 设置为高电平,CY15x102QN 器件就会自动切换到待机模式。要将器件切换到深度省电或休眠模式,SPI 主机须使用 SPI 操作码协议。具体来说,SPI 主机切换到两种最低功耗模式之一的步骤如下:首先将 /CS 设置为低电平,然后发送一个特殊操作码(深度省电为 BAh,休眠为 B9h),最后将 /CS 设置为高电平(图 8)。

图 8:CY15x102QN F-RAM 器件在操作码序列结束后自动进入待机模式,但开发人员可以使用正常 SPI 操作码程序将其置于更低功耗模式,如深度省电 (DPD) 模式。(图片来源:Cypress Semiconductor)

当 SPI 主机在发送适当的低功耗操作码后将 /CS 设置为高电平时,CY15x102QN F-RAM 在约 3 μs 内进入要求的低功耗模式。

在待机模式下,当 /CS 变为低电平时,Cypress F-RAM 会立即返回活动模式以启动下一个操作码序列。在深度省电或休眠模式下,F-RAM 在 /CS 变为低电平后也会返回活动模式,但深度省电模式有一个大约 10 μs 的短暂延迟,休眠模式的延迟时间为 450 μs。

总结

在各种各样依赖越来越多的传感器提供数据的应用中,对可靠、快速、低功耗、高性能 NVM 的需求变得越来越重要。在像汽车 ADAS 之类关键任务型应用领域,数据丢失会严重削弱旨在保护车辆及其乘客的安全机制。

使用 Cypress Semiconductor 的 F-RAM 器件,开发人员可以轻松增加能够可靠存储关键数据数十年的 NVM,而不用牺牲性能或低功耗要求。

电子发烧友App

电子发烧友App

评论