§2.5 8086的引线

本节概述

概念1:有40个引脚,其中地址线有20根,16根分时复用的数据线,还有控制线,如图2-8所示。

某些引脚上的信号,在不同时刻具有不同的意义。例如,AD15~AD0,在某些时候表示地址A15~A0,在另一些时候表示数据D15~D0。

概念2:

8086组成系统时,根据系统规模大小,有两种组态:最小组态(或称最小模式)、最大组态(或称最大模式)。若8086与小容量存储器及少量外设接口相连,就可连成最小组态。由于系统规模小,负载轻,可以直接用CPU的控制信号作为系统的控制信号。所以,8086工作于最小组态时,可用于构成一个单处理机系统,此时,由CPU提供所有总线控制信号。

若系统规模大,负载重,就要组成最大组态。此时由系统"总线控制器"根据8086的状态信号S1~S0,产生总线控制信号,这样,在最小组态时提供控制信号的引脚将被重新赋予新功能,以支持多处理器系统。

系统的组态由CPU引脚MN/MX来控制,若MN/MX接电源VCC,则系统处于最小组态;若MN/MX接地,系统处于最大组态。

本节内容

1.最小模式和最大模式的概念

2.最小组态

3.大组态

4.其它引线信号

§2.5.1 最小模式和最大模式的概念

为了尽可能适应各种各样的使用场合,在设计8086/8088CPU芯片时,使它们可以在两种模式下工作,即最小模式和最大模式。

所谓最小模式,就是在系统中只有8086或者8088一个微处理器。在这种系统中,所有的总线控制信号都直接由8086或8088产生,因此,系统中的总线控制电路被减到最少,这些特征就是最小模式名称的由来。

最大模式是相对最小模式而言的。最大模式用在中等的或者大型的8086/8088系统中。在最大模式系统中,总是包含有两个或多个微处理器,其中一个主处理器就是8086或者8088,其他的处理器称为协处理器,它们是协助主处理器工作的。

和8086/8088配合的协处理器有两个,一个是数值运算协处理器8087,一个是输入/输出协处理器8089。

8087是一种专用于数值运算的处理器,它能实现多种类型的数值操作,比如高精度的整数和浮点运算,也可以进行超越函数(如三角函数、对数函数)的计算。在通常情况下,这些运算往往通过软件方法来实现,而 8087是用硬件方法来完成这些运算的,所以,在系统中加入协处理器8087之后,会大幅度地提高系统的数值运算速度。

8089在原来上有点像带有两个DMA通道的处理器,它有一套专用于输入/输出操作的指令系统,但是,8089又和DMA控制器不同,它可以直接为输入/输出设备服务,使8086或8088不再承担这类工作。所以,在系统中增加协处理器8089后,会明显提高主处理器的效率,尤其是在输入/输出频繁的场合。

关于8086/8088到底工作在最大模式还是最小模式,这完全由硬件决定。

§2.5.2 最小组态

1、 INTA(Interrupt Acknowlege,中断响应,输出引脚24)

中断响应信号,低电平有效。8086响应外界中断请求时,执行"中断响应"周期",它由两个"总线周期"构成,在每个中断响应的总线周期 均有效。

"中断(Interrupt)"是一种操作,它使CPU中止正在执行的程序,

而转入称为"中断处理程序(Interrupt Handler)"(或称中断服务程序Interrupt Service,或称中断例程Interrupt Routine)的程序。当中断处理程序执行完后,CPU接着执行被中断的程序(相对于中断处理程序来说,被中断的程序称为主程序),如图2-9所示。

多个外部设备一般通过"中断控制器"8259向CPU提出中断请求,8259也向CPU提供"中断类型码",以标识是那一个外部设备在向CPU请求中断。CPU用中断响应信号INTA通知8259。在中断响应信号INTA的第二个周期,8259向CPU提供中断类型码,中断类型码如图2-10所示。

2、ALE(Address Latch Enable,地址锁存允许,输出引脚25)

地址锁存允许信号,高电平有效。8086的某些引脚是分时复用的,例如,AD15~AD0引脚上,在T1时刻出现地址信号A15~A0,在其他时刻,这些引脚作为他用,因此,需要把T1时刻出现的地址信号锁存起来,一般用"地址锁存器"8282/8283锁存地址信号。ALE信号的作用是,启动地址锁存器工作(在ALE下降沿,使地址信号装入地址锁存器中),地址锁存器8282和74LS373的引脚如图2-11所示。地址锁存器(如INTEL8282)工作情况:

OE:输出允许信号

OE有效时,输出DO0~DO7有效

OE无效时,输出DO0~DO7高阻

STB:选通信号

STB有效时:输出DO7~D00等于输入DI7~DI0

STB无效时:输出DO7~D00不变(无论输入DI7~DI0如何变化)

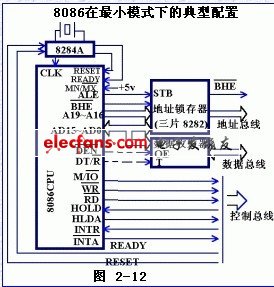

8086最小模式的典型配置如图1-12所示。

3、DEN(Data Enable,输出,三态,引脚26)

数据允许信号,低电平有效。在信号作为数据收发器8286/8287的允许传送信号时,DEN为手法器提供一个控制信号,表示CPU当前准备发送或接受一个数据。总线收发器将DEN作为输出允许信号。

DEN信号的电平输出情况如下:在每个存储器访问周期和I/O访问周期为低电平,即有效电平;在中断响应周期,也为有效电平。不过,如果是读周期或者是中断响应周期,DEN在T2状态的中间开始有效,并且一直保持到T4状态的中间;如果是写周期,DEN在T2状态的一开始就成为有效电平,并且,一直保持到T4状态的中间。在DMA方式时,DEN被浮置为高阻状态。

4、 DT/R(Data Transmit / Receiver,输出,三态,引脚27)

数据发送/接收信号,用于确定数据收发器8286/8287的数据传送方向,8286的引脚图如图2-13。

DT/R=1,发送,数据从CPU→数据总线;

DT/R=0,接收,数据从数据总线→CPU。

8286工作情况:

8286是数据收发器,可以接受或发送数据

T=1时发送,信号从A7..A0→B7..B0

T=0时接受,信号从B7..B0→A7..A0

OE=1时,允许接受或发送

OE=0时,A7..A0和B7..B0均为高阻状态

5、M/IO(Memory,Input、Output,输出,三态,引脚28)

CPU发出该信号,通知外部电路,此时是访问存储器,还是访问I/O设备。

M/IO=1(高电平),访问存储器;

M/IO=0(低电平),访问I/O设备。

一般在前一个总线周期的T4状态,M/IO就成为有效电平,然后开始一个新的总线周期。在此周期中,M/IO一直保持有效电平,直到本周期的T4状态为止。在DMA方式时,M/IO被浮置为高阻状态。在8088中,此引脚的电平状态与8086相反。

6、WR(Write,输出,三态,引脚29)

低电平有效,CPU发出该信号,表示此时进行写操作(写存储器或I/O,由 M/IO信号决定)。对任何写操作,WR只在T2、T3、TW期间有效。在DMA方式时,WR被浮置为高阻状态。

7、RD(Read,输出,三态,引脚32)

低电平有效,CPU发出该信号,表示此时进行读操作(读存储器或I/O,由M/IO信号决定),如表2-3所示。

8、HOLD(Hold Request,输入,引脚31),总线请求信号HLDA(Hold Acknolege,输出,引脚30),总线请求允许信号

在微型计算机中,所有设备均连接至总线上,能够控制总线(即控制总线上的设备)且正在控制总线的设备称为"总线主设备(Master)",被控制的设备称为"总线从设备"(Slave)。一般情况下,CPU作为总线主设备,使用总线(控制其他设备)。

当其他设备请求占用总线时,向CPU发出总线请求信号HOLD;CPU收到该信号后,如果同意,就发出一个允许信号HLDA,同时,CPU使自己的地址线、数据线及相应的控制信号线浮空,不干扰总线的工作。申请使用总线的设备在收到CPU发出的HLDA后,就可以使用总线了,在使用完总线后,撤消HOLD(使其为低电平)信号,CPU检测到HOLD消失后,撤消HLDA(使其为低电平),又恢复了对总线的控制权,时序如图2-14,2-15所示。

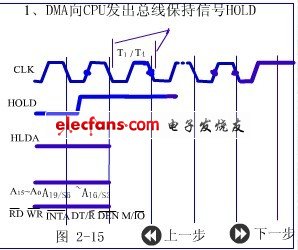

1、DMA向CPU发出总线保持信号HOLD。

2、CPU在下一个CLK周期的上升沿检测到该请求。

3、CPU在总线周期的T4或Ti状态发出HOLD(CPU仅在这两个状态才能发出HOLD)。并使AD15~AD0,A19/S6~A16/S3,INTA,RD,WR,DEN,DT/R信号浮空。同时,DMA获得对总线的控制权。

4、DMA使用完系统总线,清除HOLD信号。

5、CPU在CLK上升沿检测到HOLD已消失。

6、CPU在下降沿清除HLDA,并可重新驱动上述信号,既获得对系统总线的控制权。