第三节 读写存储器RAM

本节内容:

一、 基本存储电路

二、 RAM的结构

三、 典型RAM芯片举例

四、 RAM与CPU的连接

§5.3.1 基本存储电路

一个基本存储电路存储一位二进制信息0或1。它是存储器的核心。

1、SRAM基本存储电路

SRAM的基本存储电路的核心是MOS管构成的双稳态触发器。

MOS(场效应)管的工作特性如左图所示。

MOS管构成的双稳态触发器:

T3、T4的g、s端连在一起,vgs=0,d、s呈现高阻,该大电阻作为负载。 双稳态触发器有两个稳定状态:

① 若T1导通,A=0,使T2截止,B=1,B=1又保证T1导通。该状态表示存储信息0。(A=0)。

② 若T1截止,A=1,使T2导通,B=0,B=0又保证T1截止。该状态表示存储信息1。(A=1)。

为了将信息0/1写入或读出触发器,就需要加控制电路。加入控制电路的基本存储单元如下图:

写操作:CPU送出地址信号、数据信号D和写入信号R/W=0。地址信号分成行地址和列地址,行地址经"行选择译码"产生行选择线信号,使该基本存储电路被选中,T5、T6导通;列地址经"列选择译码"产生列选择线信号,使T7、T8导通。R/W=0,三态缓冲器A1、A3导通,A2禁止,数据信号D经A1、A3、T7、T8、T5、T6进入该基本存储电路。

如写入1,则I/O=1、I/O=0,它们使A=1、B=0,T1截止、T2导通,即数据1被写入。

如写入0,则I/O=0、I/O=0,它们使A=0、B=1,T1导通、T2截止,即数据0被写入。

在写入完成后,地址信号消失,T5、T6、T7、T8截止,双稳态电路保持写入的信息不变。或者说,写入过程相当于将输入电荷存储到T1、T2的栅极上。在写入信号和选择信号消失后,两个作为负载电阻的T3、T4和电源Vcc相连,从而可以不断地往T1、T2的栅极补充电荷(T3给T2、T4给T1补充),加上T1、T2互相控制,能够保持住所写入的数据。

读操作:CPU送出地址信号,R/W=1。T5、T6、T7、T8导通,R/W=1,三态缓冲器A2导通,A1、A3禁止,基本存储电路A点状态经T5、T7、A2送至数据线D。A=1表示D=1,A=0表示D=0。在读出后,基本存储电路的状态不发生变化,即读操作是非破坏性的。

SRAM的特点:

(1) 采用CMOS电路构成,读出/写入速度快(5~15ns)。

(2) 所用管子数目多,单个器件的容量小,如256×4,16Kb×1,64Kb×8。

(3) T1、T2总有一个处于导通状态,使得SRAM的功耗较大。

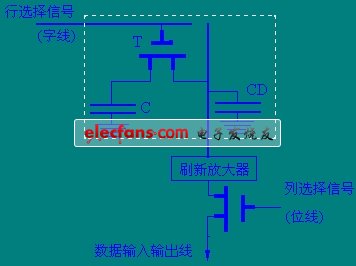

2、 DRAM基本存储电路(单管DRAM基本存储电路)

数据以电荷形式存在电容C上,当C上有电荷,表示信息1;当C上无电荷,表示信息0。

写操作时,"行选择信号"为1,Q导通,若"列选择信号"为1,该基本存储电路被选中,由"数据输入/输出线"送来的信息通过刷新放大器和Q管送入到电容C。

读操作时,"行选择信号"为高电平,使存储矩阵中该行的所有基本存储电路的Q管导通,"刷新放大器"读取对应电容C上的电压值,刷新放大器的灵敏度很高,放大倍数很大,并且能将从电容上读得的电压值折合为逻辑"0"或逻辑"1"。"列选择信号"所选中的基本存储电路输出数据。

在读出过程中,选中行上所有基本存储电路中的电容均受到打扰,为了在读出之后,仍能保存所容纳的信息,刷新放大器对这些电容上的电压值读取之后又立即进行重写。

DRAM的特点:

(1) 利用电容存储电荷的原理来存储信息的。由于电容会逐渐放电,所以,必须对DRAM中的电容不断地补充电荷,这一过程称为刷新。

(2) 典型的刷新周期为2ms,一般用专门的DRAM控制器控制刷新,其刷新过程称为刷新周期。

(3) 所用MOS管较SRAM少,芯片位密度较高,如32Kb×1,16Mb×1。

(4) 功耗较小。

§5.3.2 RAM的结构

1、 存储体

存储芯片中全部基本存储电路的集合称为"存储体"。存储体中的基本存储电路按矩阵排列,称为"存储矩阵"。 存储矩阵有N×1、N×4、N×8结构。

下图是一个4096×1的存储芯片的逻辑示意图和结构示意图。

2、 外围电路

(1) 地址译码。

4Kb×1的存储器有4096个存储单元,选择某一单元需要12根地址信号(212=4096),它们被分为行地址和列地址。

(2) I/O电路(输出驱动)。

(3) 读写控制电路。R/W。

(4) 片选信号,CE或CS。

微机存储器由多个存储芯片组成,CPU读写存储器时,必须选中一个芯片,该选择信号称为"片选信号",一般用CE或CS表示。只有被选中的芯片(CE/CS有效),才能读出或写入数据。

(5) 三态缓冲器(图中未画出)

用于连接CPU数据总线和存储器数据总线。当三态缓冲器选通时,CPU才能与存储器交换数据。否则,CPU与存储器断开。

(6) 刷新电路(图中未画出,仅DRAM存储器需要)

用于控制DRAM刷新。

3、 地址译码方法

(1) 单译码(N×8)

以32×8存储器为例。需要5根地址线(A4~A0),地址译码后,同时访问存储器中的8位。

|

NX8存储器,单个 芯片同时输入/输 出一字节地所有8 位采用单译码 |

|

|

(2) 双译码(N×1)

以1024×1存储器为例。需要10根地址线(210=1024),A4~A0地址译码后,得到32根行选择线X32~X1,选中存储矩阵的某一行;A9~A5地址译码后,得到32根列选择线Y32~Y1,选中存储矩阵的某一列。行和列均被选中的单元可以写入或读出。

三、 典型RAM芯片举例

1、 Intel 2114芯片(1Kb×4)

该芯片有1024×4=4096个基本存储单元,排列成64×64矩阵,10根地址信号线(210=1024)译码后选中芯片中的4位。

存储器中的数据经"输入/输出三态门"与数据总线相连。由片选信号CS和读写信号R/W共同控制三态门。当CS=0,R/W=0,输入三态门打开,数据总线来的数据被写入存储器。当CS=0,R/W=1,输出三态门打开,存储器中的数据输出到数据总线。

2114的读写时序如下图。

(1) 读操作

① 存储器收到地址总线上来的地址信号后,经过一定时间,片选信号CS有效(片选信号CS由地址信号译码产生)。

② 片选信号CS有效后,经过时间tCX,存储器开始输出数据。输出数据稳定后,CPU获得数据。从CS有效到数据稳定的时间是tCD。

③tOTD:恢复时间,用于存储器内部操作。从输出数据稳定至可以输入新的地址的时间

④ 地址信号消失后,数据维持的时间是tOHA。

⑤ 从存储器获得地址信号,到输出数据稳定的时间,称为"存取时间"tA。

⑥ 从存储器获得地址信号,到允许下次地址信号出现的时间,称为"读周期"tRC。 tRC=tA+tOTD。

(2)写操作

写周期是指:启动一次写操作至启动下一次写操作的时间。

tA:存取时间(写入时间),从地址有效到数据写入。

tAW:地址建立时间,从地址出现到稳定。

tW:写脉冲宽度。

tWR:写操作恢复时间,从数据写入到可以输入新地址的时间,用于存储器内部操作。

tDW:数据有效时间,从数据稳定到数据写入。

tDH:数据保持时间,写信号无效后,输入数据应保持的时间。

写周期对时序的要求是:①地址建立时间tAW(从地址输入到稳定)应尽量短,在写入信号WE有效前,地址已稳定。

②写脉冲宽度tW应满足要求。 写周期tWC=tAW+tW+tWR。

2、Intel 2164芯片(64Kb×1)

(1)、外部结构

Intel 2164 是64Kb×1 DRAM芯片,其位密度较高,选择其中某个基本存储电路需要16根地址信号,为了减少引腿数目,对于高密度DRAM,一般使行地址和列地址共用一组引腿,并设置行地址选通信号RAS和列地址选通信号CAS,在内部设置行地址寄存器和列地址寄存器。Intel 2164的引脚图及逻辑符号如下图:

|

|

先在引脚A7~A0上提供行地址RA7~RA0,并使 有效,芯片把该行地址锁存在行地址锁存器中,再在引脚A7~A0上提供列地址CA7~CA0,根据行地址RA7~RA0和列地址CA7~CA0,选中一个基本存储电路。

(2)、内部结构

该芯片的内部结构如下图,包括存储体、行地址锁存器、时钟控制电路、1/4 I/O门、数据输出缓冲器、数据输入缓冲器等部分构成。

64K存储体由4个128×128存储矩阵、4个128读出放大器、2个1/128行译码器和2个1/128列译码器构成。行地址中的RA6~RA0同时加到4个存储矩阵上,在每个存储矩阵中均选中一行,共有4×128个基本存储电路被选中,它们的信息被选通至4×128个读出放大器。列地址中的CA6~CA0也同时加到4个存储矩阵上,在每个存储矩阵中均选中一列。这样,经RA6~RA0和CA6~CA0,选中4个基本存储电路。最后,由RA7和CA7控制"1/4 I/O 门"选中其中一个基本存储电路(RA7由"8位地址缓冲器"即行地址寄存器提供,CA7实际使用经"列时钟缓冲器"的CAS代替)。

(3)、工作时序

读周期工作时序:

① 先在A7~A0引脚上提供行地址,在tASR时间后使行地址选通信号RAS有效,把行地址锁存在内部的行地址锁存器中。读周从RAS有效开始,在RAS有效后,A7~A0引脚上的行地址应至少保持tRAH时间。

② 再在A7~A0引脚上提供列地址,在tASC时间后使列地址选通信号CAS有效,在CAS有效后,A7~A0引脚上的列地址还应至少保持tCAH时间。行地址和列地址选中一个基本存储电路。

③ 读信号(WE=1)应在CAS有效前tRCS有效。

④ 在CAS有效tCAC后,数据输出线Dout开始输出数据。如果从读周期开始(RAS有效)计算,数据在tRAC后输出。为了保证数据可靠读出,RAS有效的时间tRAS应满足一定的宽度。

⑤ RAS当变高后,对存储电路中的电容进行预充电,预充电时间为tRP,因此,整个读周期的时间tRC=tRAS+tRP。

写周期工作时序:

① 行地址->RAS有效->行地址保持->列地址->CAS有效->列地址保持。行地址和列地址选中一个基本存储电路。

② 写信号(WE=0)应在CAS有效前tWCS有效。为了保证可靠写入数据,写信号的宽度至少应为tWP。

③ 数据信号CAS在有效的下降沿被写入,但数据信号应在CAS有效tDS前有效,且在CAS有效后应维持tDH。

④ 整个写周期的时间tRC=tRAS+tRP。

读-修改-写周期工作时序:

在指令中,常要对某个内存单元(8个基本存储电路)的内容读出进行修改,然后再写回这一单元。为了提高操作速度,在存储器中设计了"读-修改-写"周期。

这一周期的性质类似于读周期和写周期的组合,但它不是由两个单独的读周期和写周期结合起来的,而是在RAS和CAS同时有效的情况下,由WE信号先实现读出(①,WE=1),在修改后又实现写入(②,WE=0)。

页模式读周期工作时序:

在指令中常要求数据块操作,为了提高数据传送的速度,可采用页模式操作。即维持行地址不变(RAS不变),由连续的CAS信号对不同的列地址进行操作。每个CAS操作一个内存单元。(CAS信号的数量要受RAS信号宽度的限制)。

首先给存储器指定行地址,然后连续指定几个列地址。在每次列地址有效tASC时间后,CAS信号有效,在CAS信号有效后tCAC时间,数据被读出。

当行地址(CPU访问地址的高位)不变,几个列地址(CPU访问地址的低位)对应几个内存单元,这几个内存单元称为一"页",故这种内存操作方式称为"页模式"。如,列地址为8位,则一页等于256字节。

在页模式操作时,可实现存储器读、存储器写、读-修改-写操作。上图为页模式读操作时序。页模式操作提高了数据传送的速度,又称为"快速页模式FPM(fast page mode)"。

刷新周期工作时序:

与一般的存储器刷新方式类似,Intel 2164的刷新周期只需行地址(称为"唯刷新方式")。先在A7~A0上提供行地址,然后使 有效,选中存储体中的一行或几行,由"读出放大器"实施刷新。对于Intel 2164,存储体由4个128×128矩阵构成,每次刷新在4个128×128矩阵中均选中一行,经过128个刷新周期即可完成整个存储体的刷新。在刷新过程中,由于 始终无效,故数据不会读出至Dout线上。

四、 RAM与CPU的连接

1、 RAM芯片组的连接

以8个4096×1芯片连接成一组4KB的芯片组为例。

连接方法:

① 每一片4096×1芯片输出一位数据,8片输出数据一字节D7~D0。

② 8片的 连接在一起,同时被选中。

③ 8片的 连接在一起,同时被读/写。

④ 8片的地址线A11~A0连接在一起。

2、 4KB RAM的连接(全译码) 以8片Intel 2114(1Kb×4)构成4KB RAM为例。 每片Intel 2114需要10根地址线A9~A0,每片输出4位数据,两片构成一组,输出一字节8位数据。

每组的两片应同时被访问,因此,其地址信号A9~A0连接在一起,读/写信号也连接在一起。

用地址信号A15~A10译码输出(0~63)选择某组存储器。

| 组别 | A15~A10 | 组内地址A9~A0 | 地址范围(A15~A0) |

| 0组 | 000000 | 0000000000 ~1111111111 |

0000,0000,0000,0000(0000FH)~ |

| 1组 | 000001 |

0000,0100,0000,0000(0400H)~ 0000,0111,1111,1111(07FFH) |

|

| 2组 | 000010 |

0000,1000,0000,0000(0800H)~ 0000,1011,1111,1111(0BFFH) |

|

| 3组 | 000011 |

0000,1100,0000,0000(0C00H)~ 0000,1111,1111,1111(0FFFH) |

在这种连接方式中,全部高位地址A15~A10(A9~A0为芯片组的组内地址)均参与译码选择芯片组,称为"全译码"。其特点是,每一组的地址是唯一的。

3、 4KB RAM的连接(线译码)

"线译码"方式:单独用一根地址线选择芯片组。例如,用A10=0选0组,A11=0选1组,A12=0选2组,A13=0选3组。

线译码的特点是:

① 直接用某根地址线选择芯片组,不需要地址译码器。

② 一组芯片有多组地址。

以0组为例(A10=0选中0组)。

|

A15~A11

|

A10

|

A9~A0

|

地址范围

|

|

00000

|

0

|

0000000000~111111111

|

0000,0000,0000,0000(0000H)~ 0000,0011,1111,1111(03FFH)

|

|

00001

|

0000,1000,0000,0000(0800H)~ 0000,1011,1111,1111(0BFFH)

|

||

|

.....

|

|

||

|

11111

|

1111,1000,0000,0000(F800H)~ 1111,1011,1111,1111(FBFFH)

|