|

根据功能

|

|

只读存储器(ROM) | ||

|

随机存取存储器(RAM)(又称为读写存储器) |

|

静态(STATIC RAM,简称SRAM) |

||

| 动态RAM(Dynamic RAM,简称DRAM) | ||||

一、 RAM的电路结构与工作原理

1. RAM存储单元

存储单元是存储器的最基本存储细胞,它可以存放一位二进制数据。

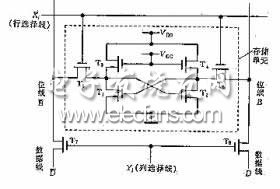

(1)静态RAM存储单元

静态RAM中存储单元的结构如5.1图。虚线框中的存储单元为六管SRAM存储单元,其中

5.1 六管静态存储单元

T1~T4构成一个基本RS触发器,用来存储1位二值数据。T5与T6为本单元控制门,由行选择线Xi控制。Xi=1使T5T 6导通,触发器与位线接通;Xi =0,T5T6截止,触发器与位线隔离。T7T8为一列存储单元公用控制门,用于控制位线与数据线的连接状态,由列选择线Yj控制。显然,Xi=Yj=1时,T5~T8都导通,触发器的输出才与数据线接通,该单元才能通过数据线传送数据。因此,存储单元能够进行读/写操作的条件:Xi=Yj=1。

静态RAM的特点是,数据由触发器记忆,只要不断电,数据就能永久保存。

(2)动态RAM存储单元

静态RAM存储单元缺点:使用管子多,功耗大,集成度受到限制。

动态RAM存储数据的原理是基于MOS管栅极电容的电荷存储效应。由于漏电流的存在,电容上存储的数据(电荷)不能长久保存,因此必须定期给电容补充电荷,以避免存储数据的丢失,这种操作称为再生或刷新。常见的动态RAM存储单元有三管和单管两种。

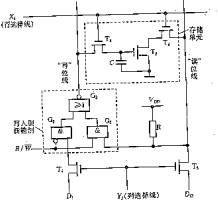

5.2 三管动态存储单元

5.2图为三管动态存储单元,存储单元是以MOS管T2及其栅极电容C为基础构成的,数据存于栅极电容C中。若电容C充有足够的电荷,使T2导通,这一状态为逻辑0,否则为逻辑1。图中除了存储单元外,还画出了该列存储单元公用的写入刷新控制电路。

图5.2中行、列选择线Xi、Yj均为高电平时,存储单元被选中;读/写控制信号  为高电平时进行读操作,低电平进行写操作;G1门输入端的小圆圈表示反相。

为高电平时进行读操作,低电平进行写操作;G1门输入端的小圆圈表示反相。

在进行读操作时,地址信号使门控管T3导通,此时若C上充有电荷且使T2导通,则读出数据为0;反之,T2截止,使“读”位线获得高电平,输出数据为1。 由图可以看出,“读”位线信号分为两路,一路经T5由Do输出,另一路经写入刷新控制电路对存储单元刷新。

进行写操作时,  为低电平(

为低电平(  ),此时G2被封锁,由于Yj为高电平,T4导通,输出数据DI经T4并由写入刷新控制电路反相,再经T1写入到电容器C中。这样,当输入数据为0时,电容充电;而输入数据为1时,电容放电。

),此时G2被封锁,由于Yj为高电平,T4导通,输出数据DI经T4并由写入刷新控制电路反相,再经T1写入到电容器C中。这样,当输入数据为0时,电容充电;而输入数据为1时,电容放电。

除了读/写操作可以进行刷新外,刷新操作也可以通过只选通行选择线来实现。例如,当行选择线Xi为高电平,且  读有效时(

读有效时(  =1),C上的数据经T2`T3到达“读”位线,然后 经写入刷新控制电路对存储单元刷新。此时Xi有效的整个一行存储单元被刷新。由于列选择线Yj无效,因此数据不被读出。

=1),C上的数据经T2`T3到达“读”位线,然后 经写入刷新控制电路对存储单元刷新。此时Xi有效的整个一行存储单元被刷新。由于列选择线Yj无效,因此数据不被读出。

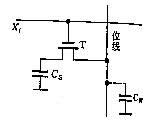

为了提高集成度,目前大容量动态RAM的存储单元普遍采用单管结构,其电路如5.3图。

5.3 单管动态存储单元

0或1数据存于电容CS中,T为门控制,通过控制T的导通与截止,可以把数据从存储单元送至位线上或者将位线上的数据写入到存储单元。

为了节省芯片面积,存储单元的电容CS不能做的很大,而位线上连接的元件较多,杂散电容Cw远大于CS。当读出数据时,电容CS上的电荷向CW转移,位线上的电压VW远小于读写操作前CS上的电压VS(即VW=VSCS/(CS+CW))。因此,需经读出放大器对信号放大。同时,由于CS上的电荷减少,存储的数据被破坏,故每次读出后,必须及时对读出单元刷新。

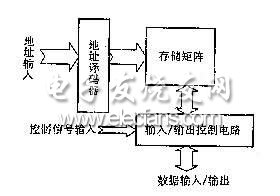

2. RAM的基本结构

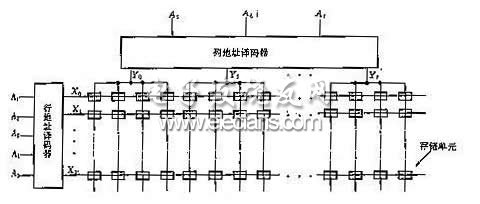

一般而言,存储器由存储矩阵、地址译码器和输入/ 输出控制电路3部分组成,其结构如图5. 4所示,由此看出进出存储器有3类信号线,即地址线、数据线和控制线。

图5. 4 RAM电路的基本结构

(1)存储矩阵

存储器由许多存储单元组成,每个存储单元存放1位二值数据。通常存储单元排列成矩阵形式。存储器以字为单位组织内部结构,1个字含有若干个存储单元。1个字中所含有的位数称为字长。在实际应用中,常以字数和字长的乘积表示存储器的容量,存储器的容量越大,意味着存储器存储得数据越多。

例如,一个容量为256´4(256个字,每字4位)的存储器,有1024个存储单元,这些存储单元可以排成32´32列的矩阵形式,如图5.5所示。图中每行有32个存储单元,每四列存储单元连接在相同的列地址译码线上,组成一个字列,由此看出每行可存储8个字,每个字列可存储32个字。每根行地址选择线选中一行,每根列地址选择线选中一个字列。因此,图示阵列有32根行地址选择线和8根列地址选择线。

图5.5 256×4RAM存储矩阵

(2)地址译码

通常RAM以字为单位进行数据的读出与写入(每次写入或读出一个字),为了区别各个不同的字,将存放同一个字的存储单元编为一组,并赋予一个号码,称为地址。不同的字单元具有不同的地址,从而在进行读写操作时,可以按照地址选择欲访问(读写操作)的单元。字单元也称为地址单元。

地址译码电路实现地址的选择。在大容量的存储器中,通常采用双译码结构,即将输入地址分为行地址和列地址两部分,分别由行、列地址译码电路译码。行、列地址译码电路的输出作为存储矩阵的行、列地址选择线,由它们共同确定欲选择的地址单元。地址单元的个数N与二进制地址码的位n满足关系式  。

。

对于图5. 5所示的存储矩阵,256个字需要8位二进制地址码(A7~A0)。地址码有多种形式。例如,可以将地址码A7~A0的低5位A4~A0作为行地址,经过5线—32线译码电路,产生32根行地址选择线;地址码的高3位A7~A5作为列译码输入,产生8根列地址选择线。只有被行地址选择线和列地址选择线同时选中的单元,才能被访问。例如,若输入地址码A7~A0为00011111时,X31和Y0输出有效电平,位于X31和Y0交叉处的字单元可以进行读出或写入操作,而其余任何字单元都不会被选中。

(3)输入/输出控制电路

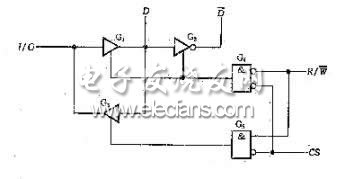

图5. 6给出了一个简单的输入/输出控制电路。在系统中为了便于控制,电路不仅有读/写控制信号  ,还有片选控制信号CS。当片选信号有效时,芯片被选中,可以进行读/写操作,否则芯片不工作。片选信号仅解决芯片是否工作的问题,而芯片的读、写操作则由读/写控制信号

,还有片选控制信号CS。当片选信号有效时,芯片被选中,可以进行读/写操作,否则芯片不工作。片选信号仅解决芯片是否工作的问题,而芯片的读、写操作则由读/写控制信号  决定。

决定。

在图5.6中,当片选信号CS=1时,G5、G4输出为0,三态门G1、G2、G3均处于高阻状态,输入/输出(I/O)端与存储器内部完全隔离,存储器禁止读/写操作,即不工作;而当CS=0时,芯片被选通,根据读/写控制信号  的高低,执行读或写操作。当

的高低,执行读或写操作。当  时,G5输出高电平,G3被打开,于是被选中的单元所存储的数据出现在I/O端,存储器执行读操作;反之,

时,G5输出高电平,G3被打开,于是被选中的单元所存储的数据出现在I/O端,存储器执行读操作;反之,  时,G4输出高电平,G1、G2被打开,此时加在I/O端的数据以互补的形式出现在内部数据上,并被存入到所选中的存储单元,存储器执行写操作。

时,G4输出高电平,G1、G2被打开,此时加在I/O端的数据以互补的形式出现在内部数据上,并被存入到所选中的存储单元,存储器执行写操作。

图5.6 输入/输出控制电路

3.RAM的操作与定时

为了保证存储器准确无误地工作,加到存储器的地址、数据和控制信号必须遵守几个时间边界条件。下面以静态RAM为例加以说明。

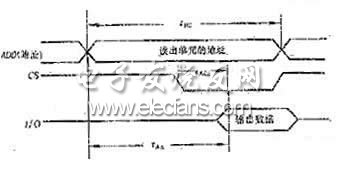

图5.7给出了读出过程的定时关系。读出过程操作如下:

图5.7 读操作时序图

(1)欲读出单元的地址加到存储器的地址输入端;

(2)加入有效的片选信号CS;

(3)在  线上加高电平,经过一段延时后,所选择单元的内容出现在I/O端。

线上加高电平,经过一段延时后,所选择单元的内容出现在I/O端。

(4)让片选信号CS无效,I/O端呈高阻状态,本次读出结束。

由于地址缓冲器、译码器及输入/输出电路存在延时,在地址信号加到存储器上之后,必须等待一段时间  ,数据才能稳定地传输到数据输出端,这锻时间称为地址存取时间。如果在RAM的地址输入端已经有稳定地址的条件下,加入片选信号有效到数据已经有稳定地址的条件下,加入片选信号,从片选信号有效到数据稳定输出,这段时间间隔记为

,数据才能稳定地传输到数据输出端,这锻时间称为地址存取时间。如果在RAM的地址输入端已经有稳定地址的条件下,加入片选信号有效到数据已经有稳定地址的条件下,加入片选信号,从片选信号有效到数据稳定输出,这段时间间隔记为  。显然在进行存储器读操作时,只有在地址和片选信号加入,且分别等待

。显然在进行存储器读操作时,只有在地址和片选信号加入,且分别等待  和

和  以后,被读单元的内容才能稳定地出现在数据输出端,这两个条件必须同时满足。图中

以后,被读单元的内容才能稳定地出现在数据输出端,这两个条件必须同时满足。图中  为读周期,它表示该芯片连续进行两次读操作必须的时间间隔。

为读周期,它表示该芯片连续进行两次读操作必须的时间间隔。

写操作的定时波形如图5.5所示。写操作过程如下:

图5.5写操作时序图

(1)将欲写入单元的地址加到存储器的地址输入端;

(2)在片选信号CS端加上有效逻辑电平,使RAM工作;

(3)将待写入的数据加到数据输入端;

(4)在  线上加入低电平,进入写工作状态;

线上加入低电平,进入写工作状态;

(5)使片选信号无效,数据输入线回到高阻状态。

由于地址改变时,新地址的稳定要经过一段时间,如果在这段时间内加入写控制信号(即  变低),可能将数据错误地写入其他单元。为了防止这种情况出现,在写控制信号有效前,地址必须稳定一段时间

变低),可能将数据错误地写入其他单元。为了防止这种情况出现,在写控制信号有效前,地址必须稳定一段时间  ,这段时间称为地址建立时间。同时,在写信号无效后,地址还要维持一段写恢复时间

,这段时间称为地址建立时间。同时,在写信号无效后,地址还要维持一段写恢复时间  。为了保证速度最慢的存储器芯片的写入,写信号有效的时间不得小于写脉冲宽度

。为了保证速度最慢的存储器芯片的写入,写信号有效的时间不得小于写脉冲宽度  。此外,对于写入的数据,应在写输入信号失效前

。此外,对于写入的数据,应在写输入信号失效前  时间内保持稳定,且在写信号失效后继续保留

时间内保持稳定,且在写信号失效后继续保留  时间。在时序图中还给出了写周期

时间。在时序图中还给出了写周期  ,它反映了连续进行两次写操作所需要的最小时间间隔。对于大多数半导体存储器来说,读周期和写周期是相等的,一般为十几到几十ns。

,它反映了连续进行两次写操作所需要的最小时间间隔。对于大多数半导体存储器来说,读周期和写周期是相等的,一般为十几到几十ns。

由于动态RAM的地址大都采用行、列地址分时送入的方法,因此,其读、写操作定时与静态RAM稍有不同。

二、RAM存储容量的扩展

在数字系统或计算机中,单个存储器芯片往往不能满足存储器的容量的要求,因此,必须把若干个存储器芯片连在一起,以扩展存储容量。扩展存储容量的方法可以通过增长字长(位数)或字数来实现。存储器的字数通常采用K,M或G为单位,其中  ,

,  ,

,

1. 字长(位数)的扩展

通常RAM芯片的字长为1位,4位,8位,16位和32位等。当实际存储器系统的字长超过RAM芯片的字长时需要对RAM实行位扩展。

位扩展可以利用芯片的并联方式实现,即将RAM的地址线、读/写控制线和片选信号对应地并联在一起,而各个芯片的数据输入/输出端作为字的各个位线。例如,用4个4K´4位RAM芯片可以扩展成4K´16位的存储系统,如图5.9所示。

图5.9 用4K*4位RAM芯片构成4K*16位的存储器系统

2. 字数的扩展

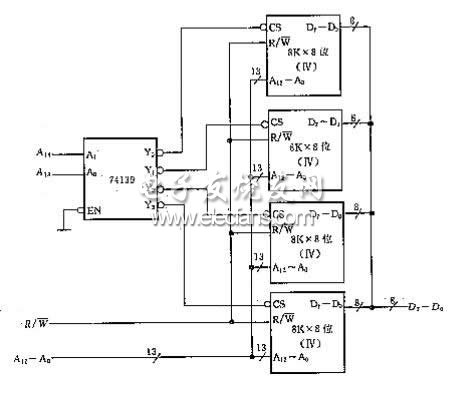

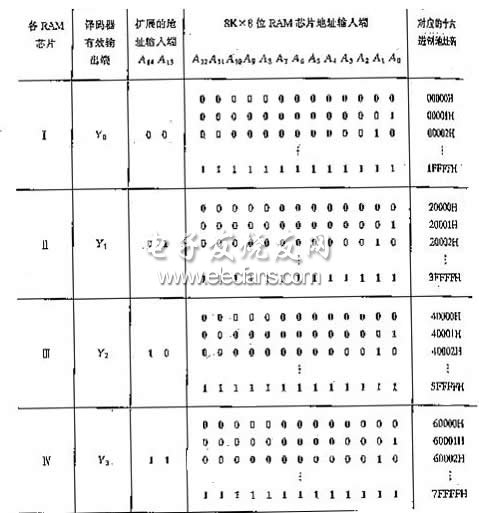

字数的扩展可以利用外加译码器,控制存储器芯片的片选输入端来实现。例如,利用2-4线译码器将4个5K´5位的RAM芯片扩展为32K´5位的存储器系统。扩展方式如图5.10。

图5.10 用8K×8位RAM芯片构成32K×8位的存储器系统

图中,存储器扩展所要增加的地址线A14、A13与译码器的74139的输入相连,译码器的输出Y0~Y3分别接至4片RAM的片选信号控制端CS,这样,当输入一个地址码(A14~A0)时,只有一片RAM被选中,从而实现了字的扩展。芯片的地址分布,如表5.1所示。

表5.1 32K*8位存储器系统的地址分配表

实际应用中,常将两种方法相互结合,以达到字和位均扩展的要求。可见,无论需要多大容量的存储器系统,均可利用容量有限的存储器芯片,通过位数和字数的扩展来构成。

三、 RAM举例

目前,市场上的RAM品种繁多,且没有一个统一的命名标准。不同厂商生产的功能相同的产品,其型号也不尽相同,例如MOTOROLA公司生产的MCM6264和NEC公司生产的uPD41256芯片例子。使用时可以查阅器件手册。