一种选择序列的并行折叠计数器

大小:0.81 MB 人气: 2018-02-04 需要积分:2

随着纳米工艺的发展和芯片尺寸的增大,芯片的集成度和设计复杂度越来越高,芯片测试的目标故障、测试数据量测试应用时间也显著增长。另一方面,昂贵的自动测试设备( Automatic Test Equipment,ATE)的通道数和带宽极其有限。因此,研究如何在保障芯片测试故障覆盖率的前提下,压缩测试数据,减少测试应用时间,降低测试成本,具有十分重要的意义。

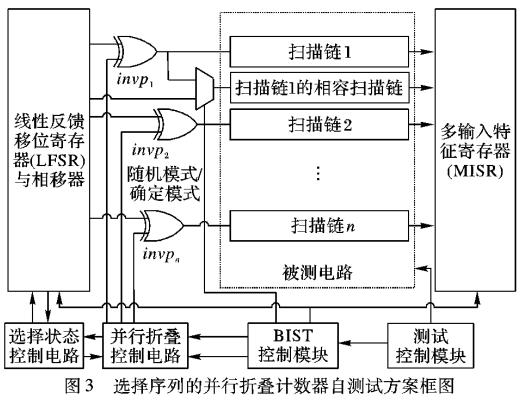

为了减少测试应用时间并保证高测试数据压缩率,提出一种选择序列的并行折叠计数器。在分析并行折叠计算理论的基础上,通过记录表示折叠索引的组序号和组内序号生成选择状态的测试序列,避免了无用和冗余的测试序列的生成。ISCAS标准电路的实验结果表明,该方案的平均测试数据压缩率为94. 48%,平均测试应用时间为类似方案的15. 31%。

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

下载地址

一种选择序列的并行折叠计数器下载

相关电子资料下载

- 10 MHz OCXO,带40 MHz频率计数器 97

- STM32G4系列芯片定时器的延时输出问题 532

- 风速继电器的应用领域 1034

- 简仪计数器/定时器模块满足严格的工业标准和安全要求 325

- TS-RadiMation测试软件如何在序列测试中发挥作用? 40

- PLC计数器的工作原理与功能 567

- 三菱PLC高速计数器的基本特点 339

- 三菱PLC计数器和数据寄存器介绍 625

- 了解反馈振荡器,看这篇文章就够了 122

- 提升效率的利器——10进制计数器的使用指南 174