本文主要是Lattice公司市场总监Shakeel Peera给大家谈面对竞争激烈的FPGA市场,Lattice公司将持续优化FPGA成本和功耗。

2012-08-14 14:12:55 783

783

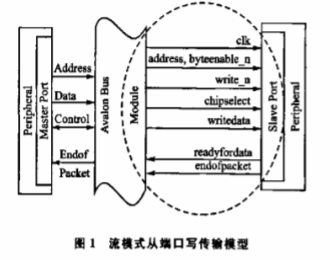

桥接技术实现多IP核集成可以显著减少芯片的研发成本;与方法二相比,改进方法不仅能够有效整合芯片内部资源,还可以降低系统功耗,提高芯片的整体性能。

2020-09-08 17:58:00 3358

3358

EDGE和3G支持,射频组件和子系统厂商再也不能将这一重担推到OEM厂商身上。相反,射频厂商现在开始承担这一责任。他们不仅需要减少组件数量并降低射频子系统的成本,还需要提供问题最少、功能强大的射频前端子系统来加快上市时间,同时实现与上一代2G子系统相同的效益。原文位置

2019-06-26 08:17:58

充电仓提供完整的电源解决方案。 IP5416 通过一个电感实现升压功能。其高集成度与丰富功能,使其在应用时仅需极少的外围器件,并有效减小整体方案的尺寸,降低 BOM 成本。 IP5416 内置一个 5V

2021-07-07 20:00:43

方案的尺寸, 降低 BOM 成本。 IP5502 只需一个电感实现充电与升压功能。可 以支持低成本电感和电容。 IP5502 的同步升压系统提供额定 1A 输出电流, 转换效率高至 91%。轻载时,可设

2022-05-04 18:29:51

耳机充电仓提供完整的电源解决方案。 IP5511 的高集成度与丰富功能,使其在应用时仅需极少的外围器件,并有效减小整体方案的尺寸,降低 BOM 成本。 IP5511 内置一个 5V 输出、同步整流的升压

2021-07-07 20:02:34

IP6805U是一款无线充电发射端控制SoC 芯片,兼容 WPC Qi v1.2最新标准 ,片内集成全桥驱动电路和 全桥功率 全桥功率 MOS ,电压 &电流两路通讯解调模块 ;方案集成度高

2019-11-29 20:39:50

集成度与丰富功能,使其在应用时仅需极少的外围器件,并有效减小整体方案的尺寸,

降低BOM 成本。

IP6816 内置一个5V 输出、同步整流的升压

DC-DC,功率管内置,提供最大300mA 输出电流

2023-05-08 19:41:56

TWS 蓝牙耳机充电仓提供完 整的电源解决方案。IP6816 的高集成度与丰富功能,使其在应用时仅需极少的外围器件,并有效减小整体方案的尺寸,降低BOM 成本。IP6816 内置一个5V 输出、同步

2019-12-28 17:06:22

IP6818 是一款集成 Qi 无线充接收、5V 升压转换器、锂电池充电管理、电池电量指示的多功能电源管理 SoC,为无线充 TWS 蓝牙耳机充电仓提供完整的电源解决方案。IP6818 的高集成

2020-10-28 18:43:15

一款新的LXI仪器可以通过PXI节省机架空间、资金和集成时间。本应用说明介绍了三者之间的相互关系,并针对谨慎使用SCPI,避免LAN延迟问题以达到优化执行时间进行了阐述。

2019-10-09 08:29:25

成本优化的太阳能

2019-09-26 08:10:45

计时接口的计时,CLKOUT,时间戳有效PCF2127AT / PCF2129AT TCXO的应用程序。 PCF212xAT是CMOS实时时钟(RTC)和日历IC,集成了温度补偿晶体(Xtal)振荡器(TCXO),基于集成的32.768 kHz音叉石英晶体,经过优化,具有极高的精度和极低的功耗

2020-03-26 09:32:34

■ 爱特梅尔(Atmel)公司 Peter Bishop集成电路应用中的四大挑战采用的晶体管数目晶体管数目会直接影响到裸片和封装尺寸、芯片成本及功耗。尽管生产工艺的不断进步使晶体管的面积越来越小,但

2019-07-25 06:14:54

驱动时序和副边同步整流器控制特性。利用自适应停滞时间补偿可进一步优化能效,从而改善负载范围内及可编程轻载模式下的效率,同时器件具有低功耗(

2018-09-26 16:04:09

模拟和数字电路于一体。 模拟阵列为工业、医疗和消费者市场上的应用提供灵活、快速的上市时间解决方案。应用实例包括安全感应、识别、感光及电池管理等工业应用,还有血糖仪、血液分析仪和传感器接口等医疗设备

2018-08-27 16:07:43

成本优化、低功耗、小尺寸

2023-03-24 15:06:22

时间,降低了制造成本。直观的逻辑合成环境包括先进的优化技术、屡获殊荣的时序分析和先进的推论技术,适用于与供应商无关的设计中,可加快产品上市时间、消除设计缺陷以及提供极佳的结果质量 (QoR)。 FPGA

2018-09-20 11:11:16

芯片对功耗的苛刻要求源于产品对功耗的要求。集成电路的迅速发展以及人们对消费类电子产品——特别是便携式(移动)电子产品——的需求日新月异,使得设计者对电池供电的系统已不能只考虑优化速度和面积,而必

2019-11-06 07:57:07

、功耗和容量都已经达到甚至超过此前专用IC或专用标准器件(ASSP)的水平。可编程硬件的可配置特点不仅具备产品差异化和快速上市等传统优点,同时当批量达不到足以支持开发专用IC成本的时候还可以加快投资回报

2019-08-13 07:48:48

LCD因具有工作电压低、功耗小、显示信息量大、寿命长、易集成、方便携带和电磁辐射污染小等优点,在显示技术中异军突起,被广泛应用于手机、PDA产品、手持式仪器仪表等便携式电子产品与设备中。 LCD

2012-08-12 12:28:42

Micronas公司近日宣布推出HAL 28xy系列霍尔效应传感器,专为对精度、灵敏度及低成本有要求的汽车和机电应用而优化。HAL 28xy是首款集成了微控制器、温度传感器、先进的片上补偿以及

2018-10-29 15:11:02

通信行业专家的解读是,设备消耗的能量与数据量或速率有关,单位时间内发出数据包的大小决定了功耗的大小。NB-IoT引入了eDRX省电技术和PSM省电模式,进一步降低功耗,延长了电池使用时间

2016-12-15 18:21:14

和错误检测功能(奇偶和CRC)。在ACD模式下,读写器模块大部分时间处于休眠状态,由3K RC定时唤醒,以极低功耗侦测 13.56MHz的射频场和射频卡,检测到场或卡自动产生中断唤醒MCU。侦测场和卡

2023-10-08 16:01:27

引言在工业系统中选择器件需要考虑多个因素,其中包括:性能、工程变更的成本、上市时间、人员的技能、重用现有IP/程序库的可能性、现场升级的成本,以及低功耗和低成本。工业市场的近期发展推动了对具有高

2019-06-24 07:29:33

方法是优化现有技术方案。许多网络流量仍然基于TCP/IP。TCP提供了可靠有序的数据包传输,大多数Web应用、电子邮件和文件传输都使用这种协议。可是,TCP的流管理算法并不先进:如果网络或接收端无法处理

2013-03-14 14:52:19

ipad2香港上市时间又“跳票” “又跳票了!”日前,坊间有传言称ipad2将于4月25日在香港上市,但至记者截稿时,港行市场上仍不见ipad2踪影,ipad2香港上市时间的再次“跳票”,也让深圳

2011-04-27 14:07:12

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

变异。需要多重物理IP平台,包括基于面积/功耗优化库、为高端性能定制优化库以及为CPU定制的优化库。 中芯国际SoC研发中心技术处长吴汉明博士:资金短缺是新工艺研发拦路虎 技术节点的发展方向离不开

2019-05-20 05:00:10

三款经过验证、已上线的全新低功耗解决方案可方便实现USB Type-C接口设计,并能减少开发时间和风险 低功耗USB Type-C接口充电器和设备的参考设计现已推出 使得消费电子和工业用户能够获益于

2019-06-17 05:00:07

的增加:尺寸、功耗、电路板、元件数和成本。设计工程师如何权衡抵抗有害脉冲和浪涌、设计复杂性以及成本等互相冲突的要求,同时尽可能加快上市以保持竞争力?您可以轻易将一组光耦合器固定到现有接收器上,但这么做

2018-10-26 11:02:30

市场上已有的解决方案,以降低开发成本。在当今对成本和功耗都非常敏感的“绿色”环境下,对于高技术企业,两种挑战都有什么影响呢?第一种挑战意味着开发全新的产品,其功能是独一无二的,具有较低的价格以及较低

2019-08-09 07:41:27

全球定位系统到音视频媒体流处理,这些应用都需要实时地执行复杂的算法,很多这些算法都需要遵从定期更新的行业标准。工程师开发这些应用面临的挑战是在单位成本、外形尺寸和功耗,以及严格的成本和开发时间约束下

2008-09-27 11:42:55

(mapCurrentClockDomain除了不包含clockDomain外无差别):指定IP代码路径SpinalHDL集成Verilator仿真器仿真接口,在对带RTL IP的代码进行仿真时,需指定

2022-06-22 14:59:25

使用生命周期和保证性能的基础上,大大精简了封装和工序,有效控制了成本。低功耗电路设计在电路设计上易飞扬也做了一系列优化动作:坚持低功耗设计导向,采用低功率电路设计,智能电源设计以及优化的低电压设计实现低功耗

2021-05-28 14:55:10

)。OCP简介基于IP核复用技术的SoC设计使芯片的设计从以硬件为中心转向以软件为中心,芯片设计不再是门级的设计,而是IP核和接口及其复用设计。IP核集成到系统所要考虑的问题包括:同步,例如全局执行

2019-06-11 05:00:07

,设计的USB协议层模块各功能达到了预期目标、整体性能良好。此IP core可以广泛应用于各种USB设备接口、通信转接器件,也可以集成在SOC中,作为系统芯片总线接口。文中设计的USB IP已成功地应用于

2018-11-21 11:30:06

和每立方厘米的能量不断增长。然而,物联网应用在成本和空间方面的限制更高,因此,物联网芯片系统 (SoC) 设计师不能仅依赖更昂贵或更大的电池来延长设备使用时间。本文介绍了设计师如何在低功耗工艺技术上使用Foundation IP(逻辑库和嵌入式存储器)来减少物联网设计的功耗。

2019-07-26 07:01:11

。与星形系统示例类似,利用Virtex-5LXT解决方案,可以提高集成度、缩短上市时间、优化系统特性、降低功耗和成本等。本文结论如今,串行背板技术已成为主流技术。随着带宽要求的与日俱增,将有越来越多

2019-04-12 07:00:11

和并行接口IP核,Xilinx还提供了更加完善的IP解决方案,以进一步缩短产品开发周期和上市时间。包括用于优化背板流量的流量管理器和允许板卡之间实现“多对多”连接功能的网状结构参考设计。此外

2019-04-16 07:00:05

逐渐减少──显然,借助更快速度以实现摩尔定律的方法不再灵验!功耗和微架构改良的限制,使单一处理器的发展前景受挫,业界的关注焦点已转向多处理器或多核芯片架构的开发潜力。

2019-08-02 06:32:24

你想不想知道在应用中如何实现低功耗Wi-Fi®?我们的SimpleLink™ Wi-Fi 器件系列提供易于使用且高效的方法来优化应用功耗,从而实现更长的产品使用寿命。请继续往下读,看看我们是如何实现

2018-09-04 14:48:22

如何使用优化的数据包软件降低网络功耗?

2021-05-25 06:45:33

(ADC)中分别使用分立的芯片。这种分立方案使得许多系统尺寸庞大、成本高昂且功耗高,如此才能获得所需的通道数量,进而发挥所需的功能。由于制造和校准过程复杂,这些系统通常也需要很长时间才能上市。

2019-09-11 11:52:03

本应用指南介绍了使用 UCC28056 优化过渡模式 PFC 设计以提高效率和待机功耗的设计决策。

2021-06-17 06:52:09

量。通过采用基于40nm的半导体最新制造工艺以及创新方法来优化这些复杂的器件,设计人员能够在单芯片中集成更多的功能。这不但降低了总功耗,而且还可以降低后续工艺节点每一相应功能的功耗。TPACK便是能够

2019-07-31 07:13:26

有什么方法可以提高片上系统级集成吗?有什么方法可以降低物料成本吗?

2021-05-14 06:20:23

任何地方的人打电话。与此类似,在医疗领域,早期所谓的“便携式”超声系统是推车式的,且在功耗较高、成本昂贵。幸运的是,超声系统近年来也得益于芯片集成和功耗调整技术的突破。

2020-05-19 06:11:27

、先进的数字信号处理(DSP)算法,而且需要节省空间和省电。而安森美半导体近期推出的LC823450超低功耗单芯片方案,集成了高分辨率的声音处理、音频应用所需的功能,并具有超低功耗、小尺寸、降低成本、加快产品上市等一系列优势。

2019-10-09 06:16:18

时间,CLKOUT,电源管理,带有接口的时间戳激活用于PCF2127AT / PCF2129AT TCXO的应用程序。 PCF212xAT是CMOS实时时钟(RTC)和日历IC,集成了温度补偿晶体

2020-03-20 07:39:10

到XC5VLX30T器件上,而中继卡接口结构则可装入到XC5VLX50T器件上。与星形系统示例类似,利用Virtex-5LXT解决方案,可以提高集成度、缩短上市时间、优化系统特性、降低功耗和成本等

2019-05-05 09:29:30

的SoC 设计使芯片的设计从以硬件为中心转向以软件为中心,芯片设计不再是门级的设计,而是IP核和接口及其复用设计。IP核集成到系统所要考虑的问题包括:同步,例如全局执行、数据交换和协议方面的同步操作

2018-12-11 11:07:21

怎么实现基于LFSR优化的BIST低功耗设计?

2021-05-13 06:21:01

为了实现超小的尺寸和更快的上市时间,手机制造商希望采用采用经过验证和测试的集成无线电模块,和小尺寸、简化的RF硬件方案,为其他高端功能节省空间。所以复杂的RF前端模拟、数字和高频电路需要达到更高

2019-09-26 08:06:32

集成和系统的验证。本文以现成的无线SoC设计(如GSM手机)中增加一个复杂的无线功能,即Bluetooth功能的实例来说明这一原理。Bluetooth实例充分体现确切地定义了硬件与软件接口模块化协议

2012-12-19 10:13:14

描述TIDA-00847 TI 设计展示了一个 4 通道直流输入二进制模块的空间和成本优化型架构,该模块在测量精度和状态指示方面进行了改进,且仅使用两个 TI 产品,简化了系统设计。基于 MCU

2018-10-26 10:14:32

CMOS 集成电路动态功耗的认知也是数字后端必须要掌握的;我们来聊一聊。动态功耗 = Switching Power +Internal PowerSwitching power 是由于芯片内

2022-06-09 18:06:15

P1014-RDB,QorIQ P1014参考设计板,用于具有信任架构的P1014低功耗通信处理器。 P1014 RDB是一款高度集成的参考设计板,可帮助缩短产品上市时间。该参考设计针对低成本网络应用(有或没有信任架构),有线和无线接入,工业和智能能源应用

2019-04-18 09:28:52

做到非常简洁,PCB上仅有一颗主控芯片,所有功能由一颗芯片实现。外围元件的减少,极大的精简了生产测试流程,有效降低开发难度和成本,便于产品的快速开发、生产和上市销售。由于IP6808高度集成的特性

2019-01-28 16:19:04

常用的设计技巧就是在数据传送的接口建立申请和应答机制。这虽然会造成芯片在时序、面积、功耗等方面的损耗,但对于加快系统芯片的上市速度大大有利。 第三,要注意积累IP和IP集成的经验。一旦成功地集成

2018-09-04 09:51:06

,为移动电源提供完整的电源解决方案。IP5219 的高集成度与丰富功能,使其在应用时仅需极少的外围器件,并有效减小整体方案的尺寸,降低 BOM 成本。 IP5219 只需一个电感实现降压与升压功能,可以

2021-12-29 18:39:33

一颗主控芯片,所有功能由一颗芯片实现。外围元件的减少,极大的精简了生产测试流程,有效降低开发难度和成本,便于产品的快速开发、生产和上市销售。由于IP6808高度集成的特性,适用于小尺寸和低成本解决方案

2018-07-23 19:48:43

以SCI接口电路为例,介绍基于FPGA器件的接口电路IP核如何去设计?

2021-04-28 06:10:23

的灵活性,以支持算法演进、各类接口和性能;3.功能全面的Lattice sensAI通过合作伙伴生态系统提供模块化硬件平台、神经网络IP核、软件工具、参考设计和定制化解决方案;Lattice sensAI

2018-05-23 15:31:04

于设计出符合要求的软 IP 核。 另外一方面,软 IP核的设计成本和设计时间一般都是大于硬 IP核。 这些是简单的可合成 IP 模块,供应商将通过给这些模块添加标签以跟踪它们,因为它们很容易被任何人窃取

2021-10-07 21:03:56

字消息、拍照、查询股票、预约,当然还能给世界上任何地方的人打电话。与此类似,在医疗领域,早期所谓的“便携式”超声系统是推车式的,且功耗较高、成本昂贵。幸运的是,超声系统近年来也得益于芯片集成和功耗调整技术

2018-10-23 14:28:19

引言随着应用的不断普及和深入,在设计嵌入式系统时,往往需要同时优化众多因素,如成本、功率、尺寸、性能、灵活性、产品上市时间、设计开发周期,以及可靠性等。Xilinx 公司推出的嵌入式处理器设计平台

2019-07-19 07:03:19

了设计成本。核心架构提高了逻辑效率,是目前密度最高的互联结构。硬核IP实现了高性能,提高了灵活性,而且缩短了设计时间。经过优化后的收发器具有同类最佳的信号完整性,减少了调试时间。仅使用两种电压轨,因此

2015-02-09 15:02:06

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

2023年1月13日,知名物理IP提供商 锐成芯微(Actt) 宣布在22nm工艺上推出双模蓝牙射频IP。近年来,随着蓝牙芯片各类应用对功耗、灵敏度、计算性能、协议支持、成本的要求越来越高,22nm

2023-02-15 17:09:56

(1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-12 06:14:26

商业领域占据了一定的市场。本文设计了一个高度集成、低功耗及低成本的微型惯性测量装置,可精确地测算出载体的航向角、俯仰角及位置等信息,为运动轨迹跟踪实验打下了基础,也可广泛地应用于民用航空、车辆控制、机器人、工业自动化、探矿、玩具等领域。

2019-07-22 07:37:12

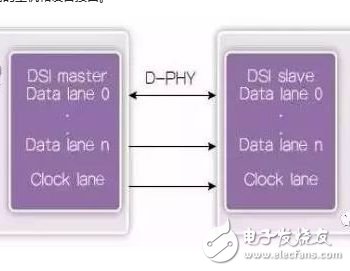

随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP 核复用的SoC 设计已成为一种重要的设计方法。在SoC 中集成的IP 核越来越多时,IP 核的互连策略和方法就成

2009-11-28 14:40:46 8

8 USB设备接口IP核的设计:讨论了用Verilog硬件描述语言来实现USB设备接口IP核的方法,并进行了FPGA的验证。简要介绍USB系统的体系结构,重点描述USB设备接口IP核的结构划分和各模块的

2010-01-08 18:15:38 22

22 用接口IP实现HDMI的便携式低功耗方案

通过使用知识产权(IP)方法,系统级芯片(SoC)设计师现在可以轻松地集成采用领先工艺技术(如90nm、65nm和40nm工艺)的HDMI接口。

2010-03-13 11:19:58 25

25 IP4777CZ38/IP4778CZ38 全集成、带有HDMI1.3接口调节功能的芯片

IP4777CZ38和IP4778CZ38在单芯片上带来先进的HDMI接口调整功能

中国,北京2008年9月5日--恩

2008-09-09 16:31:10 1028

1028 本文讨论了OCP-IP的协议与特点,设计了基于AMBA总线的OCP-IP接口,提出了一种IP自动封装的方法,为IP核的集成和管理带来极大的方便。

2011-05-19 10:07:43 10105

10105

白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

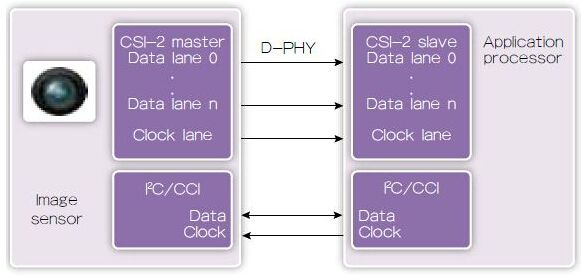

72 基于FPGA的低成本MIPI接口,专门针对视频显示器和摄像头的。设计嵌入式系统DSI和CSI-2视频接口的用户现在即可采用低成本MIPI接口

2017-02-10 16:54:11 16803

16803 采用IP核的设计方法,将外设组件互连标准(PCI)总线接口与具体功能应用集成在一个FPGA上芯片, 提高了系统的集成度。在对PCI IP核进行概述的基础上,介绍了IP核的设计方法,实现了PCI总线

2017-11-17 12:27:03 4488

4488

用户可以使用IP集成器连接IP模块创建复杂的系统设计。通过接口构建基于模块的设计,一般情况下接口包含多个总线和大量的信号线。因此,为了方便在硬件上调试那些包含大量接口的设计,就需要验证设计的接口连接。

2018-04-18 15:28:24 2978

2978

Microchip 的 RN4020 Bluetooth 低功耗模块提供了一个

高度集成的低功耗蓝牙 4.1 解决方案。高级命令接口加

速了上市时间。

2018-07-03 08:24:00 4

4 查看UltraScale器件上可用的集成100G以太网MAC和CAUI-4 IP的演示。

通过软件实现,该IP可节省高达80K的LUT和90%的功耗,简化了设计流程并缩短了产品上市时间。

2018-11-28 06:07:00 4487

4487 连接您的服务器与架顶式交换机的方式中,与采用传统光学连接相比,铜线兼具成本及功耗优化的优势。您是否对采用更具成本效益的 25G 铜线连接更感兴趣。

2019-08-01 14:49:04 2005

2005 (PLL)的系统设计所必须的模块集成到一片FPGA 上,构成一个可编程的片上系统,使所设计的电路在其规模、可靠性、体积、功耗、功能、上市周期、开发成本、产品维护以及硬件升级等多方面实现最优化。

2020-04-13 09:28:56 1137

1137

成本优化的太阳能

2021-05-12 13:58:46 2

2 在Blackfin处理器上使用.NET Micro Framework缩短上市时间和开发成本

2021-05-27 20:10:56 6

6 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-07 11:05:59 19

19 带集成缓冲器、ESD 保护和终端电阻的 VGA 接口-IP4773CZ14

2023-02-21 18:42:29 0

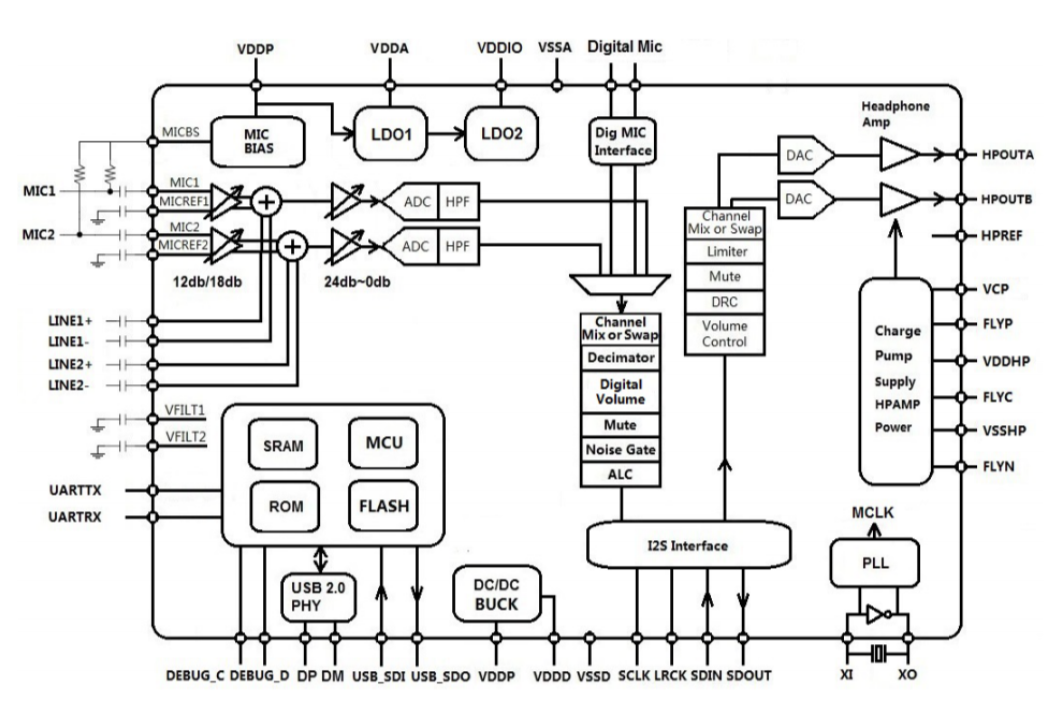

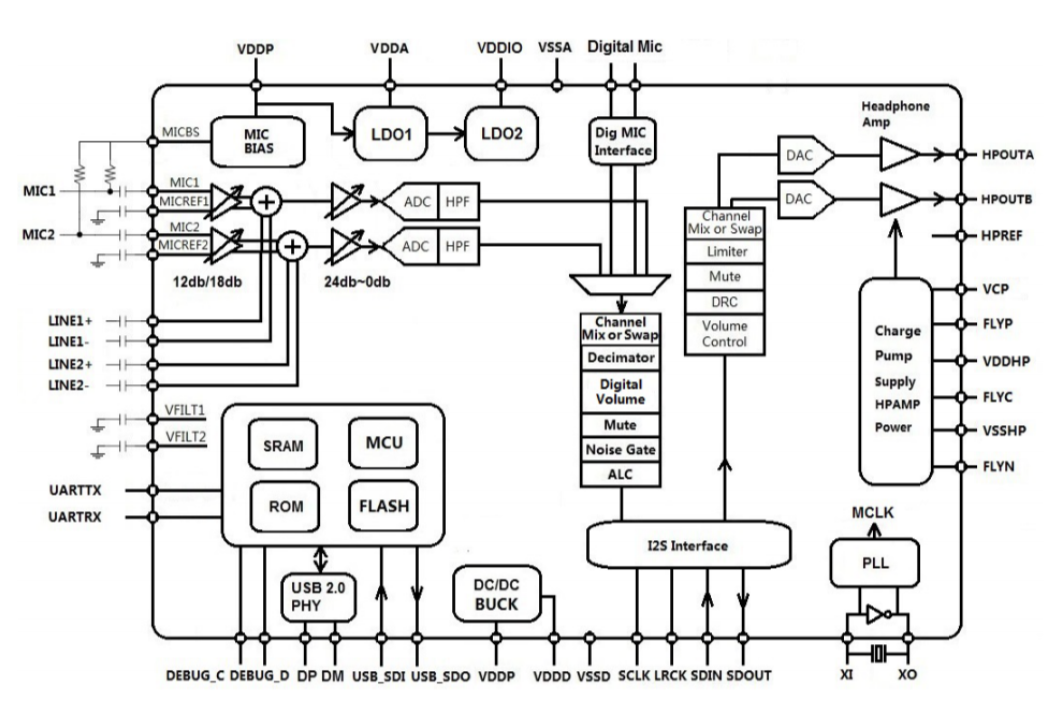

0 高度集成和低成本的USB aduio CODEC解决方案,为USB Type-C耳机应用程序优化;

无电容直接驱动Headphone,信号幅度高,功耗低;

2023-07-01 16:52:14 806

806

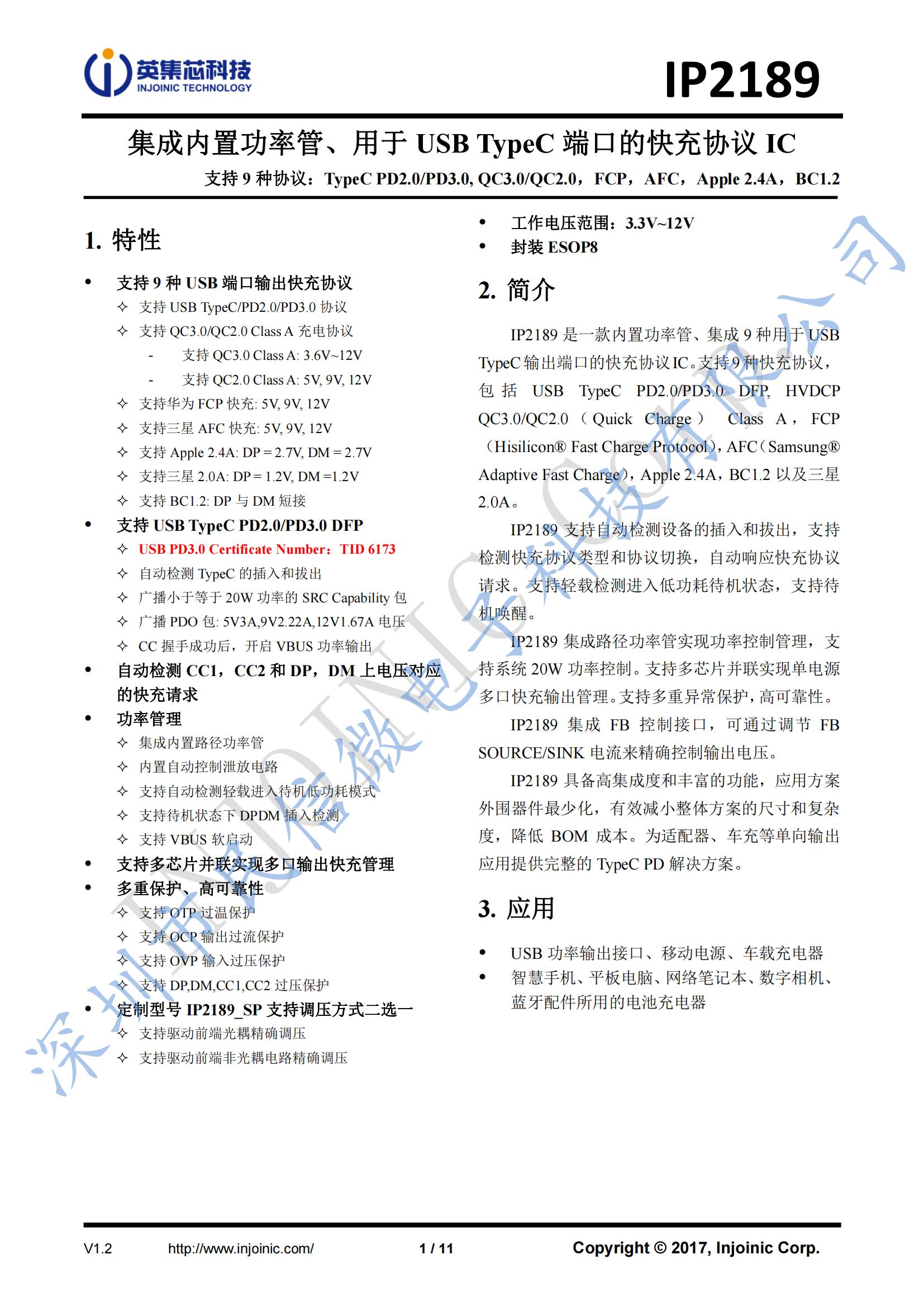

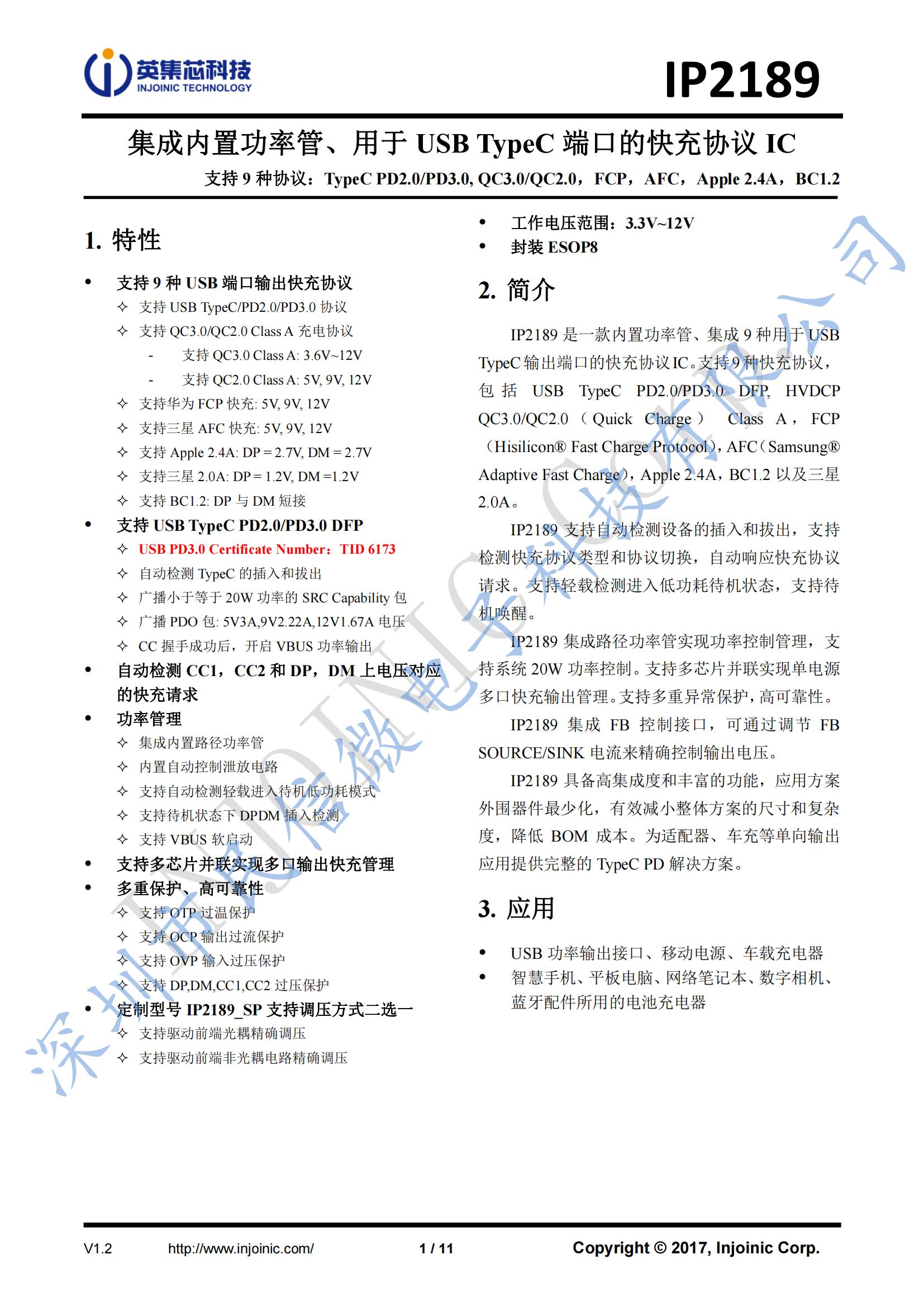

英集芯IP2189全集成旅充协议芯片,性价比最高,支持20WPD方案,自动响应快充协议请求,多重异常保护,高可靠性。

IP2189集成了FB控制接口,精确控制输出电压,有效减小方案尺寸和复杂度

2023-07-10 20:45:28 533

533

电子发烧友网站提供《Versal Premium ACAP:在灵活应变的平台上突破性集成功耗优化的网络IP.pdf》资料免费下载

2023-09-15 10:48:04 0

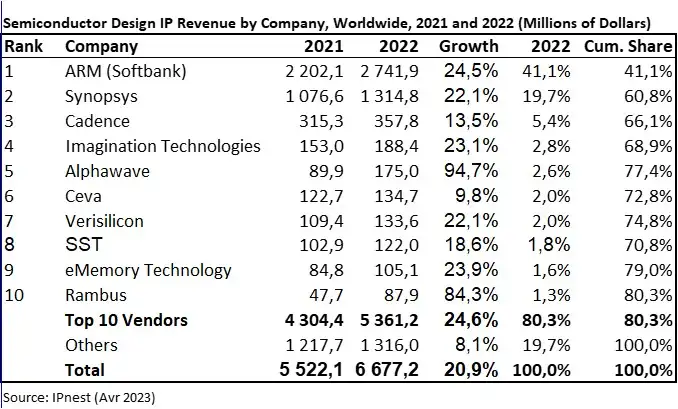

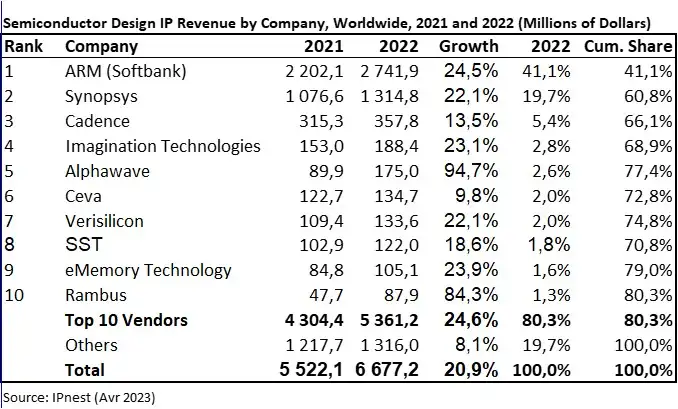

0 半导体IP通常也称作IP核(IP core),此处IP也就是指知识产权(Intellectual Property)。IP核就是一些可重复利用的、具有特定功能的集成电路模块,包含处理器IP、接口IP、物理IP、数字IP等。研究显示,近5年,接口IP的增速高于处理器IP。‘

2023-09-15 15:59:13 355

355

电子发烧友App

电子发烧友App

评论