内存控制器和PHY可支持多种DDR标准,同时降低延迟与待机功率

2012-09-26 14:08:22 1335

1335 1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 5068

5068

首先对本次工程进行简要说明:本次工程使用AXI-Full接口的IP进行DDR的读写测试。在我们的DDR读写IP中,我们把读写完成和读写错误信号关联到PL端的LED上,用于指示DDR读写IP的读写运行

2022-07-18 09:53:49 3902

3902

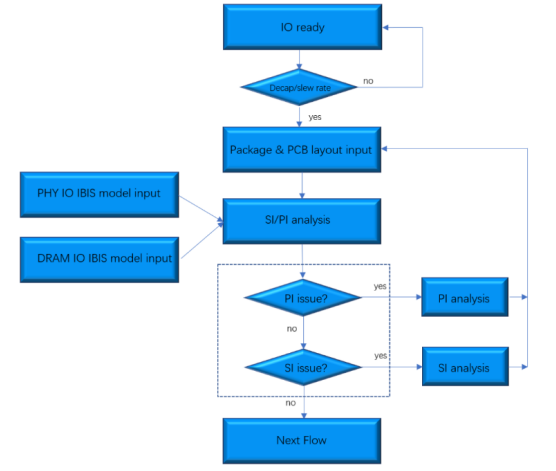

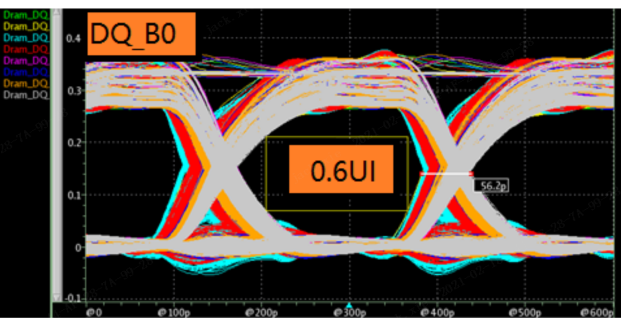

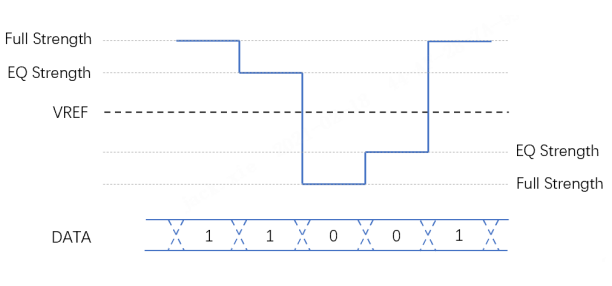

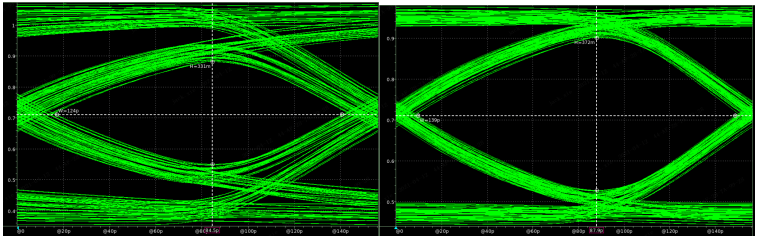

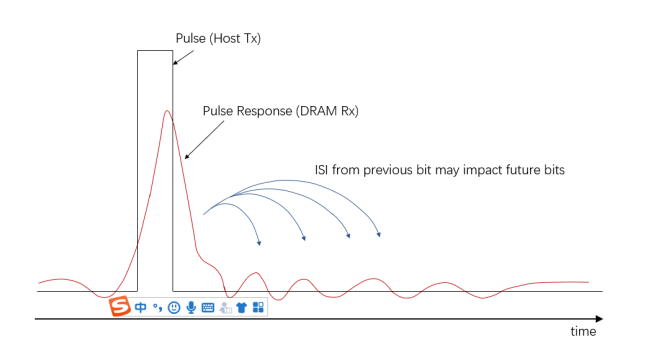

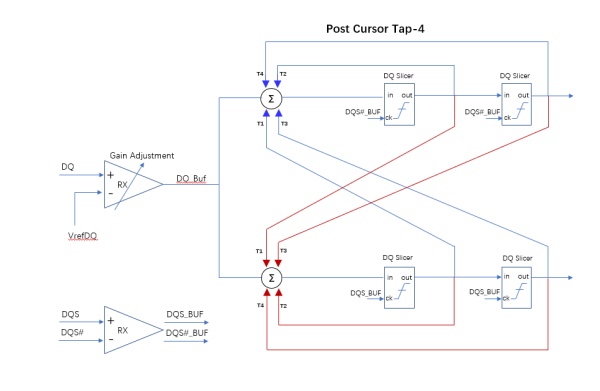

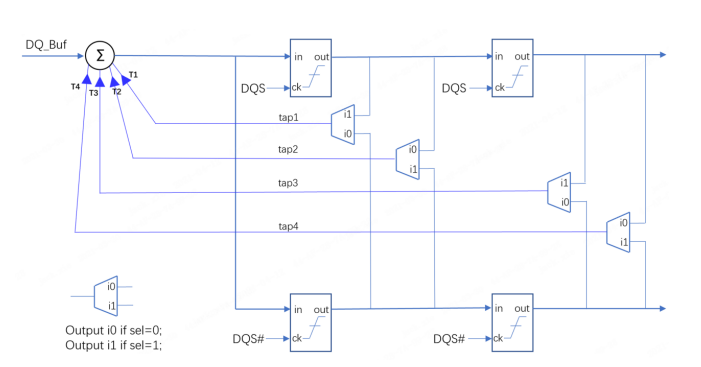

DDR接口速率越来越高,每一代产品都在挑战工艺的极限,对DDR PHY的训练要求也越来越严格。本文从新锐IP企业芯耀辉的角度,谈谈DDR PHY训练所面临的挑战,介绍芯耀辉DDR PHY训练的主要过程和优势,解释了芯耀辉如何解决DDR PHY训练中的问题。

2024-01-05 10:27:34 520

520

IP CORE DDR3 PHY ECP3 USER CONF

2023-03-30 12:01:19

SITE LICENSE IP CORE DDR3 ECP3

2023-03-30 12:02:09

IP101GR:单口PHY芯片单端口10/100 MII/RMII/TP/Fiber 快速以太网收发器(目前市场上最热门的PHY芯片,可代替市场上LAN8710A/LAN8720A/RTL8201F

2015-06-01 15:40:25

IP101GR:单口PHY芯片单端口10/100 MII/RMII/TP/Fiber 快速以太网收发器(目前市场上最热门的PHY芯片,可代替市场上LAN8710A/LAN8720A/KSZ8041等

2020-04-13 13:01:19

IP101GR是什么?IP101GR单口PHY芯片有何功能?IP101GR单口PHY芯片是如何进行通信的?

2021-11-01 06:08:26

在以太网通信中,设备之间的物理局链路均由 PHY 芯片建立。PHY 芯片内部含有一些列寄存器,用户可通过这些寄存器来配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息,如连接...

2021-07-20 07:28:49

随着设计复杂性增加,传统的综合方法面临越来越大的挑战。为此,Synplicity公司开发了同时适用于FPGA或 ASIC设计的多点综合技术,它集成了“自上而下”与“自下而上”综合方法的优势,能提供高结果质量和高生产率,同时削减存储器需求和运行时间。

2019-10-17 06:29:53

我用的是CYCLONEIII的芯片,定制DDR2 IP核,之后直接用SINALTAP进行信号抓取,发现无法读写的原因是local_init_done 一直为低,就像XILINX里

2013-04-27 09:46:54

IP MODULE COREU1PHY

2023-03-22 19:59:23

本次发布 Gowin DDR Memory Interface IP 参考设计及 IP CoreGenerator 支持调用 Gowin DDR Memory Interface IP 。Gowin

2022-10-08 07:17:32

本次发布 Gowin DDR2 Memory Interface IP 参考设计及 IP CoreGenerator 支持调用 Gowin DDR2 Memory Interface IP

2022-10-08 07:25:25

Gowin DDR2 Memory Interface IP用户指南主要内容包括 IP 的结构与功能描述、端口说明、时序说明、配置调用、参考设计等。主要用于帮助用户快速了解 Gowin DDR2 Memory Interface IP 的产品特性、特点及使用方法。

2022-10-08 07:08:19

Gowin® USB HSIC PHY IP 用户指南主要内容包括功能简介、信号定义、功能描述、界面配置,旨在帮助用户快速了解 Gowin USB HSIC PHY IP 的产品特性、特点及使用方法。

2022-09-30 06:05:04

IP CORE SDI PHY TRI-RATE ECP3

2023-03-30 12:01:43

2:DDR2U|DDR2_controller_phy:DDR2_controller_phy_inst|mem_dq[15]", cannot be assigned more than one

2014-03-18 19:55:04

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

描述了,DDR IP核配置 的全部过程。有兴趣的朋友可以看一下。

2012-07-26 11:08:32

什么是多点触控技术?多点触控是怎么实现的?多点触控技术的用途有哪些?

2021-06-17 07:47:51

,用于指示用户逻辑DDR2 IP核的内部PLL输出locked还未完成。phy_clkOutputALTMEMPHY产生供用户逻辑使用的半速率时钟信号。所有输入和输出到ALTMEMPHY的用户逻辑接口

2016-10-27 16:36:58

调用了DDR2控制器完整的ip核, 加了一个 黑金给的仿真模型(因为板子上的DDR2 就是这个),仿真的时候一直收不到local_init_done 拉高的信号,所以后面给的命令也没有实现,但是

2017-09-21 11:20:41

提供CPU/H264_MPEG4/USB/PCIe/SATA/3D/2D/DDR2/24bit DSP/PHY等常用IP cores1. Peripherals IP cores

2009-03-21 14:22:13

通过对2019年新能源汽车动力电池配套行业数据进行调查,研究梳理电池技术在新能源汽车发展过程中出现的问题瓶颈,归纳分析产生车辆安全事故的根本原因,进而从电池系统研发设计、电芯生产制造、生产质量管

2021-05-07 10:11:18

本帖最后由 eehome 于 2013-1-5 10:04 编辑

是否有人研究过单层ITO多点触控技术,发现这方面专利很少,有价值的paper也不多,若有人研究过,求交流,谢谢!

2012-11-14 10:45:08

大规模FPGA设计中的多点综合技术

2012-08-17 10:27:46

本文阐述了通过单总线测温元件DS1820来实现多点测温的技术,实现方法是利用DS1820和89C51单片机构建单线多点温度测控系统,通过软件对单片机进行控制,从而实现一根总线多点测温,达到理想的测温效果。

2021-05-17 07:14:49

行业的进步离不开技术的创新,就在感知规避、GPS跟随、室内视觉定位等技术的热度还未消退之时,又一批新锐技术已经登上历史的舞台。下面宇辰网独家整理了无人机领域的五大新锐技术,看看你知道多少?

2020-08-21 06:59:20

提供CPU/H264_MPEG4/USB/PCIe/SATA/3D/2D/DDR2/24bit DSP/PHY等常用IP cores1. Peripherals IP cores

2008-11-18 21:03:26

34. SATA controller and PHY35. DDR2/DDR, DDR2/DDR3 controller and PHY36. Mentor SATA host /Device

2009-08-31 21:25:12

34. SATA controller and PHY35. DDR2/DDR, DDR2/DDR3 controller and PHY36. Mentor SATA host /Device

2009-08-31 21:27:09

/USB2.0 controller and PHY33. PCIe Controller/PHY34. SATA controller and PHY35. DDR2/DDR, DDR2/DDR

2010-05-24 15:25:53

你好超级+ MPSoC设计。基于64位PL的DDR4设计。 2017.1使用IP Integrator。我试图将DDR接口设置为Ping-Pong PHY模式,而不是“控制器和物理层”。无论我做什么

2020-05-26 09:53:03

晶体管技术方案面临了哪些瓶颈?

2021-05-26 06:57:13

1、建立工程,2、调用DDR2 ip核。3、设置参数,选择如上图。其余保持默认。生成IP4、选择ddr2_phy_ddr_timing.sdc、ddr

2014-11-01 20:50:15

租用国内服务器为什么推荐选择河南耀磊商务: 河南耀磊商务江苏电信机房具有国内高标准,拥有高速的光纤线路,凭借优越的地理位置,为客户提供高质量的各项服务,给予提供完备的网络环境以及专业化的网络电信

2020-06-01 11:45:41

成为双模蓝牙芯片的重要工艺节点。锐成芯微基于多年的射频技术积累,在22nm工艺成功开发出双模蓝牙射频IP,适用于蓝牙耳机、蓝牙音箱、智能手表、智能家电、无线通讯、工业控制等多种物联网应用场景。此次锐成

2023-02-15 17:09:56

blocks.2. Design DDR/DDR2/DDR3 memory PHY both for receiver and transmitter.3. Interact with the layout

2017-11-13 14:46:14

在互联网上,IP多点传送技术应用越来越广泛,与园区网内多点传送不同的是,在互联网上,多播数据的发送端和接受端可能位于不同的网络上,这样,如何让这些多播终端系统正

2009-06-24 14:22:01 1

1 USB 2.0 PHY IP M31为客户提供了下一代USB 2.0 IP,可提供更小的芯片面积和更低的活动和暂停功耗。M31使用“全新的设计架构”来实现USB 2.0 IP,而不牺牲

2023-04-03 19:19:44

USB 1.1 PHY IP for IOT and Low Power application M31为客户提供了一个独特的用于物联网应用的USB 1.1 PHY IP。USB 1.1

2023-04-03 19:23:05

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收发器IP提供了一系列完整的PCIe 2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持

2023-04-03 19:47:28

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本应

2023-04-03 19:50:56

用于存储和高带宽连接的M31 PCIe 4.0 PHY IP–具有16GT/s的最高速度PCIe 4.0 PHY IP M31 PCIe 4.0 PHY IP为高带宽应用提供高性能、多通道

2023-04-03 19:54:58

M31 PCIe 5.0 PHY IP,用于存储和高带宽连接 M31 PCIe 5.0 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

M31移动/汽车应用MIPI IP–M31 MIPI M-PHY v3.1 IP MIPI M-PHY是一种具有高带宽能力的串行接口技术,专门为移动应用开发,以获得低引脚数和优异的功率效率

2023-04-03 20:05:47

M31移动/汽车应用MIPI IP – M31 MIPI D-PHY v1.1/v1.2 IP D-PHY是为移动应用开发的一种流行的MIPI物理层,具有灵活、高速、低功耗和低成本的优点

2023-04-03 20:09:44

M31移动/汽车应用MIPI IP–M31 MIPI C-PHY/D-PHY Combo v1.2 IP MIPI D-PHY是一串連接口技术,广泛应用于智能手机和其他支持多媒体的移动设备

2023-04-03 20:14:41

M31移动/汽车应用MIPI IP–M31 MIPI C-PHY v2.0/D-PHY v2.5组合IP M31在各种工艺节点中提供经硅验证的低功耗低成本C-PHY/D-PHY组合。用户

2023-04-03 20:20:48

M31 SerDes PHY IP M31 SerDes PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。SerDes IP支持从1.25G到10.3125Gbps的数据速率

2023-04-03 20:29:47

泰克公司日前宣布,推出针对硅验证 (silicon-proven) HS-Gear3 IP的M-PHY演示性测试解决方案,HS-Gear3 IP是MIPI联盟有关移动设备的M-PHY物理层规范的一个重要组成部分。

2013-03-29 17:00:40 1257

1257 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,立即推出基于台积电16纳米FinFET制程的DDR4 PHY IP(知识产权)。

2014-05-21 09:44:54 1769

1769 全面解析多点触控技术

2017-01-14 12:30:41 15

15 什么是多点触控? 1、多点触控定义 多点触控 (又称多重触控、多点感应、多重感应,英译为 Multitouch 或 Multi-Touch)是采用人机交互技术与硬件设备共同实现的技术,能在没有传统

2017-11-06 14:53:07 17

17 提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作

2017-11-22 07:20:50 4687

4687

近日,国际领先的定制化芯片设计方案提供商及DDR控制器和物理层IP供应商——灿芯半导体有限公司对外宣布推出基于SMIC40LL工艺的第二代DDR低功耗物理层IP,该IP与第一代的低功耗DDR PHY相比面积减少20%。

2018-03-17 10:43:39 7321

7321 PHY IP1000 单口千兆

2018-05-07 14:10:54 15

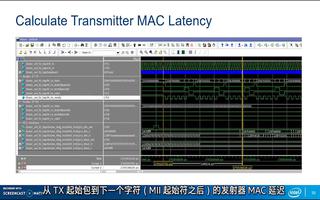

15 计算英特尔低延迟 40G 以太网 MAC 和 PHY IP 的延迟

2018-06-20 00:18:00 5775

5775

伴随手机等消费数码产品的风靡,小屏幕多点触控技术逐渐成熟,与此同时,针对大屏幕的多点触控技术也逐渐成为商业显示用户的重点需求,因为依托多点触控技术,可以实现与大屏幕的互动、感受、体验,可以完成大型多媒体互动、画面特效演示等众多精彩效果,为日常的工作学习带来更多便捷。

2018-09-01 10:48:00 5384

5384 学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DDR3 IP核作为例子进行IP核调取。

2019-11-10 10:28:45 4702

4702

硅IP和芯片提供商Rambus 31日宣布其Rambus GDDR6 PHY 内存已达到行业领先的18 Gbps性能。Rambus GDDR6 PHY IP以业界最快的18 Gbps数据速率运行,提供比当前DDR4解决方案快四到五倍的峰值性能,延续了公司长期开发领先产品的传统。

2019-11-15 16:07:03 883

883 如今大家使用的都是智能手机,相信大家对多点触摸技术都有过一定的使用体验。不仅仅是在智能手机上,现在智能的电视、 平板电脑 或是一些 笔记本电脑 中都有运用多点触控技术。多点触摸技术实际上是最初的触控技术的升级技术,从最初的单点触控到多点触控,丰富了我们对触控技术的体验。

2020-06-01 11:46:16 1438

1438 JEDEC还没有正式发布DDR5规范,但是DRAM制造商和SoC设计人员正在全力准备DDR5的发布。Cadence公司早在2018年就对这项新技术进行了宣传,并在之后发布了临时DDR5 IP

2020-06-08 17:37:34 5232

5232 DesignWare DDR5/4 PHY IP核提供基于固件的训练,无需更改硬件即可进行现场升级,从而帮助客户降低采用新协议的风险。基于固件的训练也有助于使用复杂的训练模式,在系统层面上支持最高裕度和通道可靠性。

2020-08-28 15:38:04 1986

1986 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

今天小新又为大家带来两款接口IP明星产品的技术更新:适用于22纳米工艺的DesignWare MIPI D-PHY IP和新一代DesignWare USB4 IP。希望这两款产品更新可以帮助开发者

2021-01-15 09:39:50 2116

2116 )22纳米工艺技术用于SoC设计。MIPI D-PHY IP针对可穿戴设备和物联网显示屏应用进行了进一步优化以降低功耗。

2021-01-18 15:00:24 2099

2099 领先的移动和汽车SoC半导体IP提供商Arasan Chip Systems今天宣布,用于台积公司22nm工艺技术的eMMC PHY IP立即可用 加利福尼亚州圣何塞2021年1月21

2021-01-21 10:18:23 2385

2385 UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

DDR PHY 与电路板调试:

Zynq UltraScale...

2022-02-08 15:51:58 1421

1421 Arasan的MIPI I3CⓇ Total IP™解决方案无缝集成MIPI I3CⓇ控制器、MIPI I3CⓇ PHY I/O和MIPI I3CⓇ软件栈。

2021-12-02 14:18:40 1432

1432 电子发烧友网站提供《Gowin USB HSIC PHY IP用户指南.pdf》资料免费下载

2022-09-15 10:57:43 2

2 电子发烧友网站提供《Gowin MIPI D PHY RX TXAdvance IP用户指南.pdf》资料免费下载

2022-09-15 15:22:42 5

5 电子发烧友网站提供《Gowin DDR Memory Interface IP用户指南.pdf》资料免费下载

2022-09-15 15:14:48 0

0 对于 PCIe 5 和 6,成熟的技术节点没有意义,将 PHY IP 预测分为主流和先进技术节点,因为 ASP 不同,控制器 IP ASP 应该是独立于技术的。假设将提出一个组合PCIe / CXL PHY。

2022-12-26 11:45:44 330

330 IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

2023-03-14 19:19:39 1

1 IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

2023-03-14 19:20:31 0

0 IP_数据表(I-5):SerDes PHY for TSMC 28nm HPC+

2023-03-16 19:25:46 1

1 IP_数据表(I-1):Combo Serdes PHY for TSMC 28nm HPM

2023-03-16 19:31:22 0

0 IP_数据表(I-6):SATA PHY for TSMC 28nm HPC+

2023-03-16 19:31:53 0

0 九阳Phy芯片IP179--9口TP开发板全套资料,包括芯片手册,原理图PDF和工程文件

2023-08-11 14:51:20 8

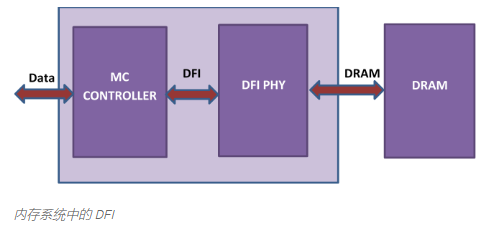

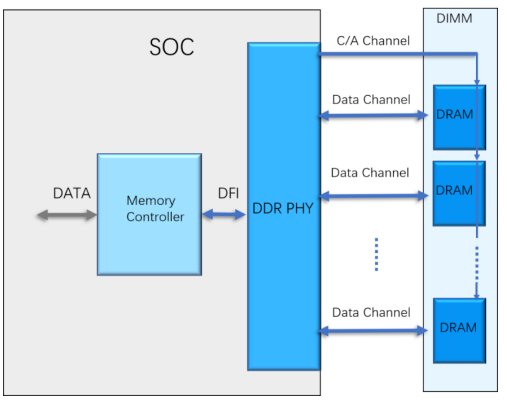

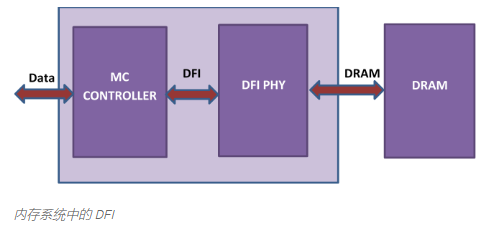

8 DDR PHY 接口 (DFI) 用于包括智能手机在内的多种消费电子设备。DFI 是一种接口协议,用于定义在 DRAM 设备之间以及 MC(微控制器)和 PHY 之间传输控制信息和数据所需的信号

2023-05-26 15:27:31 4581

4581

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

2023-07-05 19:45:11 1

1 IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

2023-07-05 19:45:56 1

1 IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

2023-07-05 19:46:14 1

1 IP_数据表(I-5):SerDes PHY for TSMC 28nm HPC+

2023-07-06 20:11:57 0

0 IP_数据表(I-2):Combo PHY for TSMC 28nm HPM

2023-07-06 20:12:26 1

1 IP_数据表(I-1):Combo Serdes PHY for TSMC 28nm HPM

2023-07-06 20:17:41 0

0 IP_数据表(I-6):SATA PHY for TSMC 28nm HPC+

2023-07-06 20:18:07 0

0 MIPI CSI-2 RX Subsystem IP实现MIPI CSI-2 v2.0协议以及底层的MIPI D-PHY v2.0协议

2023-07-07 14:15:02 1140

1140 IP 业务达成最终协议,Rambus 是首屈一指的芯片和硅 IP 提供商,致力于提高数据速率和安全性。Rambus 将保留其数字 IP 业务,包括存储器和接口控制器以及安全 IP。通过拟定的此次技术

2023-07-28 17:11:51 989

989 和存储器接口 PHY IP 业务。 随着人工智能、数据中心和超大规模应用、CPU 架构和网络设备日新月异的发展,此次技术资产收购丰富了 Cadence 现有的 IP 组合,并增强了公司的智能系统

2023-09-12 10:10:03 299

299

随着 DFI MC-PHY 接口规范的推进,事情正朝着正确的方向发展。对于不熟悉 DFI 的人来说,这是一个行业标准,它定义了任何通用 MC 和 PHY 之间的接口信号和协议。

2024-03-19 12:30:32 197

197

电子发烧友App

电子发烧友App

评论