本文将对源同步定时如何优化高速接口时序裕量进行讨论。时序预算是对系统正常工作所需时序参数或时序要求的计算。

2012-03-20 10:46:32 2444

2444

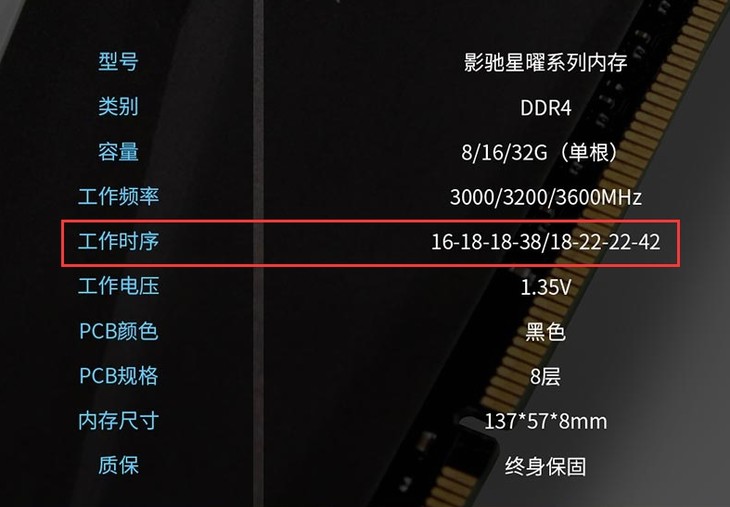

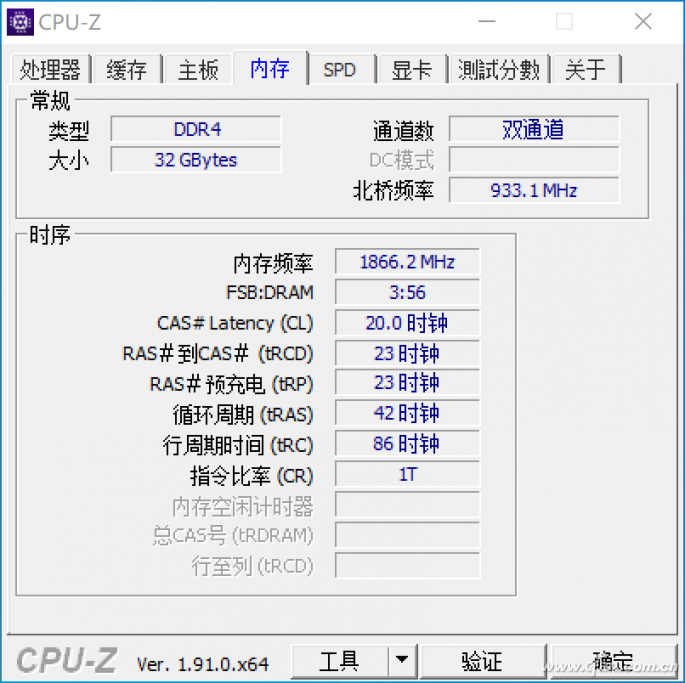

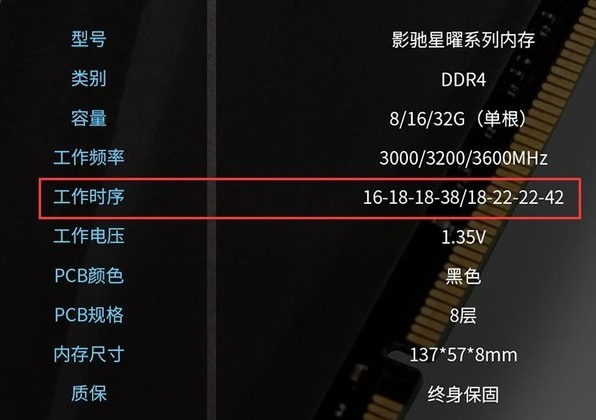

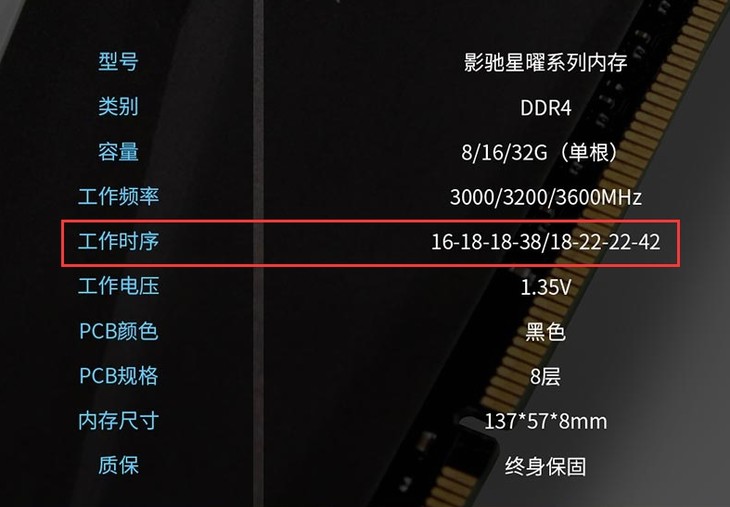

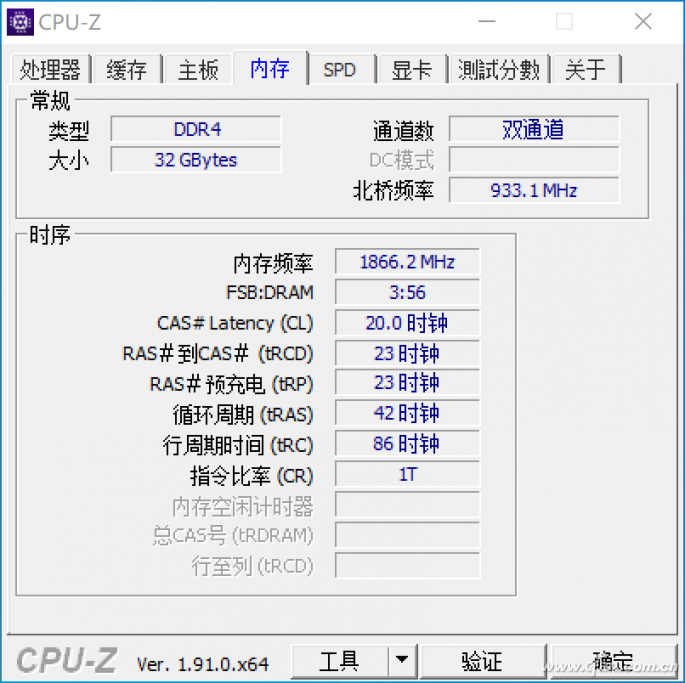

内存时序和内存频率一样,都代表了一款内存性能的高低。 内存时序由4个数字组成,中间用破折号隔开,例如16-18-18-38 这些数字表示延迟,也就是内存的反应时间。当内存接收到CPU发来的指令

2020-07-31 15:20:46 10156

10156

很多小伙伴都知道在挑选内存的时候不光要看频率,还要看时序,或者叫延迟。也就是经常标注在内存表面,在测试软件中也能看到的那些中间的带短线连接的两位数。不过要问它们到底具体代表什么意思,相信很多小伙伴

2020-08-12 16:24:10 3616

3616

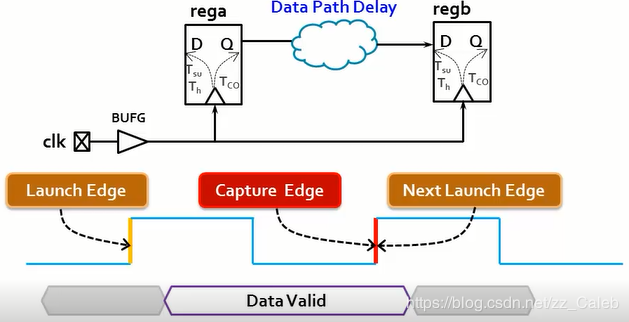

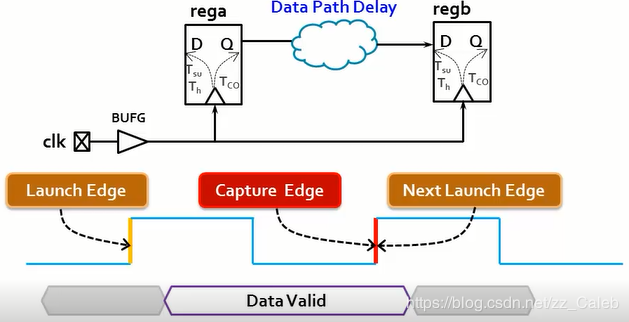

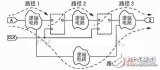

时序路径 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。 对于所有的时序路径,我们都要明确其起点和终点,这4类时序路径的起点和终点分别如下

2020-11-17 16:41:52 2768

2768

边沿。 ④ 通常情况下这两个边沿会有一个时钟周期的差别。 2、时序路径 (Timing path典型时序路径有四种) ① ② 第一类时序路径(红色) - 从device A的时钟到FPGA的第一

2020-11-25 15:27:21 8566

8566

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

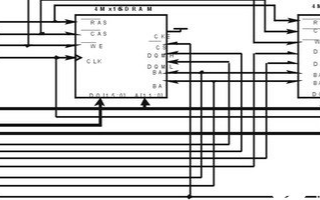

的工作原理 DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。 控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号被称为 系统时钟 。 DDR内存的数据传输,是通过前沿和下降沿来实现的

2023-07-28 13:12:06 1891

1891

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

内存时序究竟有多重要呢?究竟该如何去选择内存条呢?DDR内存时序是高一些好还是低一些好?

2021-06-18 08:20:11

目录片选引脚CS内存控制器是否需要我们手动设置片选引脚?内存控制器是如何知道地址对应哪个片选引脚呢?内存的计算读写位宽不同位宽外设的接线方式16位32位接线总结如何确定访问地址内存控制器的时序

2022-01-12 07:59:10

内存的原理和时序,学习哦!

2016-01-04 10:16:06

转载DDR3内存详解,存储器结构+时序+初始化过程2017-06-17 16:10:33a_chinese_man阅读数 23423更多分类专栏:硬件开发基础转自:首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其...

2021-07-27 07:10:34

的方法一般有四个步骤:时序分析→时序约束→时序报告→时序收敛。

为什么要进行时序分析?

信号在系统中传输时由于经过一些逻辑器件和PCB上的走线会造成一定的逻辑延时和路径延时,如果系统要求信号

2011-09-23 10:26:01

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

Card被分为A-F六个版本,各个版本之间的差异在表格中可以清楚看出来。差异主要在:条上内存颗粒数量、内存颗粒的位宽、内存条的Rank。这个版本的意思其实是内存条的不同组织形式,每个版本的特征与将来PCB布局布线、和内存条的频率时序都有关系,设计之初就要确定好。

2019-05-28 07:28:13

QuartesⅡ时序分析中常见的时间参数有哪些?

2021-09-18 08:41:47

的,应注意主板支持的最大参数,内存条的性能/大小超过该参数将造成浪费。内存注意内存条接口看一下你的主板的内存条接口是什么,别使用DDR4内存条的主板结果图便宜买了个DDR3的内存条,那可是用不了的。内存条的时序其实不用管什么时序,自己用的话时序多少都差不多,无需特别注重。内存条的品牌其实

2021-12-29 07:07:22

二相四线步进电机的一种四拍驱动时序电极1234A+1100A-0011B+1001B-0110

2021-07-08 07:43:27

本文根据演讲视频以及PPT整理而成。本文将主要围绕以下四个方面进行分享:时序数据与时序数据库时序数据库的演变时序数据库对比总结一、时序数据与时序数据库什么是时序数据库?按照维基百科解释,时间序列

2021-07-12 08:35:01

什么是“时序”?LCD1602时序参数表解析

2021-02-24 08:25:27

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2021-06-07 06:19:01

各位,我想知道怎么根据这些时序参数来确定IIC启动或者读写数据的时候延时多少啊,我看网上很多程序都是4us这个不适用吧

2018-11-21 10:16:12

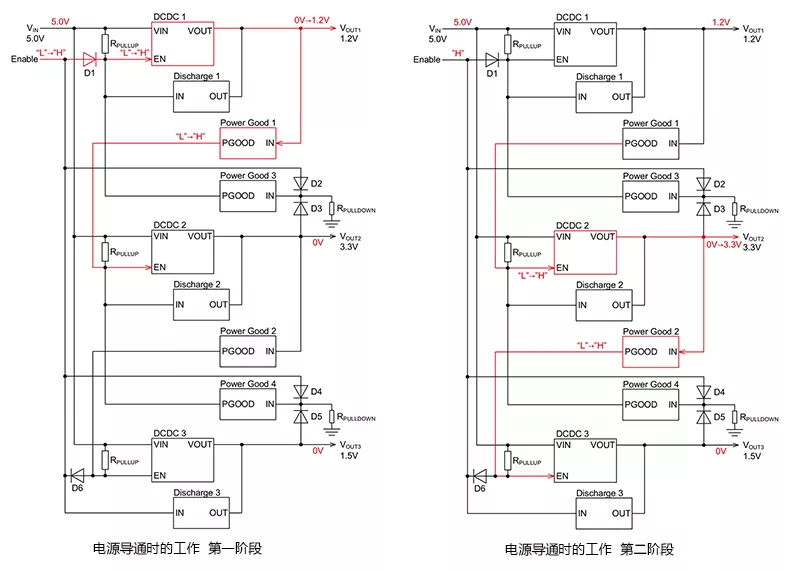

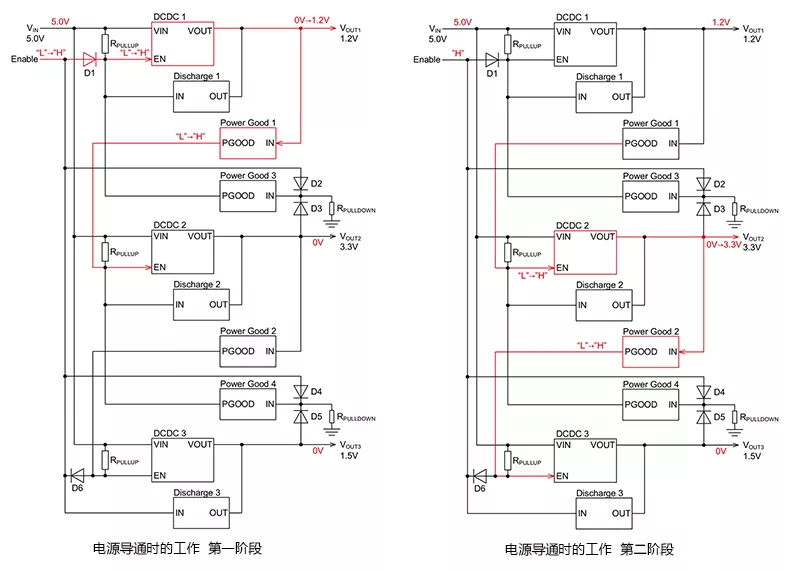

模拟时序控制器IC。它能控制和监视四个电压域。电压的上电和关断是通过控制相应电压转换器上的使能(开/关)引脚进行的。电压转换器的开启时间可以利用小电容产生的时间延迟来调整。各输出电压通过相应的监控引脚

2021-04-12 07:00:00

影响内存的关键因素是哪些?频率和时序,你是否真的了解呢?时序与频率有什么区别?哪个对内存性能影响大?

2021-06-18 07:15:39

同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 DC可以导出的时序文件包括时序描述文件和时序约束文件两种。前者描述了设计的时序情况主要用于进行综合后的动态仿真;后者带有关键路径的时延约束信息,主要供后端工具进行

2009-11-19 11:58:06 14

14 SDRAM的原理和时序

SDRAM内存模组与基本结构 我们平时看到的SDRAM都是以模组形式出现,为什么要做成这种形式呢?这首先要接触到两个概念:物理Bank与芯片位宽

2010-03-11 14:43:26 167

167 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 内存条芯片参数

整个DDR SDRAM颗粒的编号,一共是由14组数字或字母组成,他们分别代表内存的一个重要参数,了解了他们,就等于了解了现

2008-10-19 13:12:31 3913

3913 同步时序电路

4.2.1 同步时序电路的结构和代数法描述

2010-01-12 13:31:55 4672

4672

跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

本文通过对源同步时序公式的推导,结合对SPECCTRAQuest 时序仿真方法的分析,推导出了使用SPECCTRAQuest 进行时序仿真时的计算公式,并对公式的使用进行了说明。 通常我们在时序仿真中

2011-07-12 10:05:52 97

97 虽然内存价格暴跌已经导致该行业四大企业中的三家出现亏损,但美光科技总裁表示电脑内存价格很可能已经见底。

2012-02-14 09:30:20 786

786 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 时序参数.p6,有需要的朋友可以下来看看。

2016-05-11 11:30:19 4

4 CPU时序

2016-12-15 22:15:22 1

1 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 高精度SRAM端口时序参数测量电路的设计与实现_李恒

2017-01-07 19:00:39 0

0 小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。 会有来自不同角度的挑战,包括: •更好的设计计划,例如完整的和精确的时序约束和时钟规范 •节约时间的

2017-02-09 01:59:11 264

264 内存是CPU与硬盘之间的桥梁。高性能CPU、SSD,依赖内存的高性能表现。而影响内存性能最直接的因素---“频率”!原则上,频率越高,内存性能越强。(当然,这也不是绝对的,内存时序也有影响)。

2017-07-04 09:32:50 1567

1567 时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子技术中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 08:40:45 84666

84666

时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子技术中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 09:39:25 86342

86342

类图和时序图是在软件系统设计中直接和程序代码相关联的图,准确地说,程序代码是由类图直接产生,而时序图可以定义类图的方法。用例图用来描述系统功能,和类图与时序图没有直接关系。类图在UML中由三个部分

2017-10-29 11:21:34 6154

6154

PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端口,路径的终点是时序单元的输入引脚或是设计的输出端口。根据起点和终点

2018-06-22 14:40:00 6645

6645

时序图在有些教材上,又被翻译为顺序图,两者在表述上虽然有一些差别,但是大体都是准确的,可能称之为时序图会更加书面语话,听起来高大上的感觉。其实是一样的,重在理解,个人偏向于时序图,也就是时间顺序的意思。

2017-12-11 19:31:03 165730

165730

内存常见参数小科普。

2017-12-22 14:55:59 14694

14694

传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09:04 0

0 本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2020-03-13 07:59:00 1596

1596

组合电路和时序电路是计算机原理的基础课,组合电路描述的是单一的函数功能,函数输出只与当前的函数输入相关;时序电路则引入了时间维度,时序电路在通电的情况下,能够保持状态,电路的输出不仅与当前的输入有关,而且与前一时刻的电路状态相关,如我们个人PC中的内存和CPU中的寄存器,均为时序电路。

2018-09-25 09:50:00 24779

24779 通常来说,为了保证内存条的使用稳定性和兼容性,内存直接插到主板上都是以JEDEC标准上的基础频率和时序运行,但是对于最求极致游戏性能的玩家来说,高频内存是必不可少的。

2018-10-17 16:18:02 9617

9617 最近是跟内存耗上了,其一是手里没有其它硬件可测,更重要的是想趁着这段时间,把内存与性能之间的影响都慢慢测一下。今天测的就是时序与内存性能之间的关系了。时序很重要吗?答案是肯定的,但是时序对内存性能的影响到底有多大呢?下面就详细的测试一下。

2019-01-14 15:09:13 23311

23311 FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:02:00 4100

4100

静态时序或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

2019-11-22 07:09:00 2104

2104 为提高带宽,很多类型的 Memory 都采用了 Double Data Rate(DDR)interface,它对在内存控制器(memory controller)设计过程中的时序收敛和后仿真提出了挑战。

2019-08-03 10:36:40 3356

3356 本文档的主要内容详细介绍的是在写Verilog时对时序约束的四大步骤的详细资料说明包括了:一、 时钟,二、 Input delays,三、 Output delays,四、 时序例外

2019-08-30 08:00:00 32

32 很多用户购买内存,往往会把主要的关注度,集中在内存容量、频率、时序、价格,甚至灯效、外观等方面,却很少有人会留意到【内存的兼容性】。但是我想说,买内存最大的坑,莫过于内存与主板的兼容性。

2019-11-08 15:37:07 3826

3826 近日,技嘉推出了Designare DDR4-3200 64GB套条,由2条单条32GB内存组成。Designare内存开启XMP之后,它能在3200MHz频率达成18-18-18-38的时序,远远

2020-02-06 14:11:09 2722

2722 内存超频有一定几率损坏内存。内存超频涉及到修改内存的电压、主频、时序等内容,如果内存体质不佳且修改的范围超过了内存能够承受的上限,内存很容易因此而烧坏。即便超频的内存能够点亮并且通过压力测试,但也容易加速内存寿命老化。以下是对内存超频的详细说明:

2020-06-15 10:38:44 9092

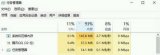

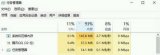

9092 生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Setup、Hold和Pulse Width的总体信息,但凡WNS、WHS或WPWS有一个小于0,就说明时序未收敛。

2020-08-31 13:49:10 5370

5370

这些数字表示延迟,也就是内存的反应时间。当内存接收到CPU发来的指令后,通常需要几个时钟周期来处理它,比如访问某一块数据。所以,时间越短,内存性能越好。

2020-09-03 16:29:46 4445

4445

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢?

2020-09-04 10:24:29 1607

1607 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 主板上市后,PC66/100的内存标准开始进入普通DIYer的视野,因为这与选购有着直接的联系。一时间,有关内存时序参数的介绍文章大量出现(其中最为著名的恐怕就是CL参数)。自那以后,DIYer才发现

2021-08-04 13:21:06 16

16 的,应注意主板支持的最大参数,内存条的性能/大小超过该参数将造成浪费。内存注意内存条接口看一下你的主板的内存条接口是什么,别使用DDR4内存条的主板结果图便宜买了个DDR3的内存条,那可是用不了的。内存条的时序其实不用管什么时序,自己用的话时序多少都差不多,无需特别注重。内存条的品牌其实

2022-01-06 15:34:12 10

10 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

很多读者对于怎么进行约束,约束的步骤过程有哪些等,不是很清楚。明德扬根据以往项目的经验,把时序约束的步骤,概括分成四大步

2022-07-02 10:56:45 4974

4974

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列文章的第1部分)。本文探讨了模拟前端时序、ADC时序和数字接口时序中的信号链考虑因素。

2022-12-13 11:20:18 1057

1057

1、时序错误的影响 一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是

2023-03-17 03:25:03 426

426 学习PLC编程的过程中,经常接触到一个概念,就是时序图,开始的时候,跳过了时序图的学习,今天在这里补上时序图的理解。

2023-04-25 11:31:39 5219

5219

本篇介绍了UML时序图的基础知识,并通过visio绘制一个物联网设备WIFI配网的UML时序图实例,来介绍UML时序图的画法与所表达的含义。

2023-05-16 09:09:22 1229

1229

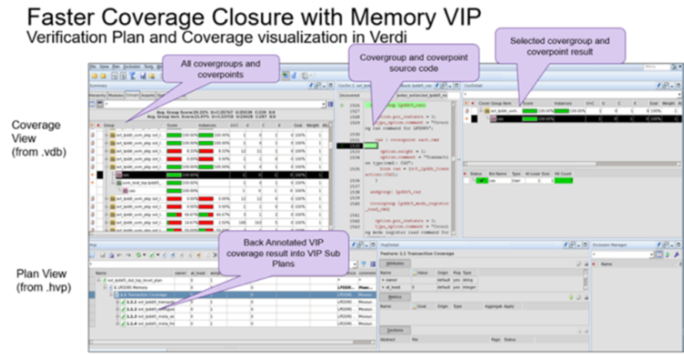

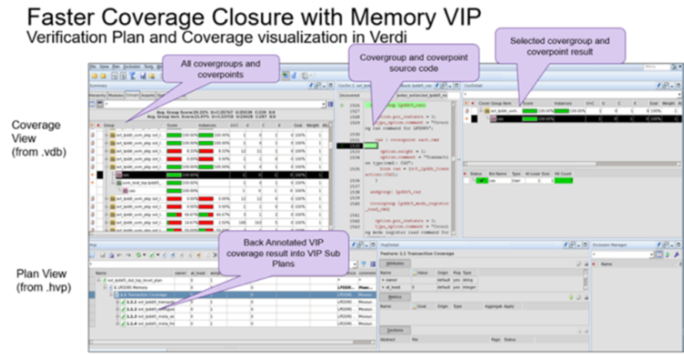

Synopsys 内存模型 (VIP) 具有内置的验证计划、功能和定时覆盖模型,可加速覆盖收敛。提供覆盖模型是为了帮助跨配置设置、模式寄存器设置、功能和时序参数的多种组合运行完整的验证方案。

2023-05-25 16:19:34 467

467

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30:43 247

247

很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 829

829

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 694

694 今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17:37 417

417

时序约束出现时序违例(Slack为负数),如何处理?

2023-07-10 15:47:06 3098

3098 今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

2023-07-07 17:15:00 1645

1645

时序:字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

2023-07-26 10:06:03 1644

1644 时序图(Timing Diagram)是信号随时间变化的图形。横坐标为时间轴,纵坐标为信号值,其值为 0 或 1。以这种图形为基础进行 plc 程序设计的方法称为时序图法。时序图是从使用示波器分析

2023-10-05 09:55:00 2063

2063 电源时序器有稳压功能吗?电源时序器是干什么用的? 电源时序器并不一定有稳压功能,但是在某些情况下,电源时序器可以具有这种功能。 首先,让我们来了解一下电源时序器是什么以及它的作用。简单来说,电源时序

2023-10-16 16:16:27 1862

1862 电源时序规格:电源导通时的时序工作

2023-12-08 18:21:43 326

326

LPDDR5和DDR5是两种不同类型的内存,它们在时序和性能方面有一些差异。尽管它们都是最新一代的内存标准,但它们面向不同的应用场景,并且在设计上有一些不同。 首先,让我们来了解一下LPDDR5

2024-01-04 10:22:06 1166

1166 有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291 时序电路是由触发器等时序元件组成的数字电路,用于处理时序信号,实现时序逻辑功能。根据时序元件的类型和组合方式的不同,时序电路可以分为同步时序电路和异步时序电路。本文将从这两个方面详细介绍时序

2024-02-06 11:22:30 291

291 时序电路是一种能够按照特定的顺序进行操作的电路。它以时钟信号为基准,根据输入信号的状态和过去的状态来确定输出信号的状态。时序电路广泛应用于计算机、通信系统、数字信号处理等领域。根据不同的分类标准

2024-02-06 11:25:21 399

399

电子发烧友App

电子发烧友App

评论