也许是应用程序,也许是上市时间限制,也许只是草率,但代码工匠似乎需要越来越多的程序、数据和暂存存储器来实现简单和复杂的功能。在某些情况下,这是可以理解的。GPS 需要大量地图数据,这会占用 NOVRAM 空间。然而,在其他情况下,似乎炸弹被用来杀死蚂蚁,嵌入式 MCU 中有 1 MB 的闪存,用于处理简单的 I/O 控制功能。

NOR Flash 是总线连接、并行接口、代码分区存储器的标准。相比之下,NAND 闪存已成长为与可执行代码没有直接关系的数据存储行业主力军。

本文着眼于高端 MCU 用于允许 NAND 闪存保存引导代码和固件的三种方法。有些只是编程的 I/O。有些通过片上硬件接口直接支持 NAND 闪存,有些通过更小的片上引导加载程序支持该过程。NOR Flash 中更小、低成本的引导加载程序仍然可以让微控制器访问大量代码和数据空间,将其缓存到 RAM 中并运行,通常比 NOR Flash 总线绑定内存更快,因为它可能不需要等待状态。此处引用的所有部件、数据表、参考设计、教程和开发系统都可以在 Digi-Key 网站上在线找到。

挑战标准

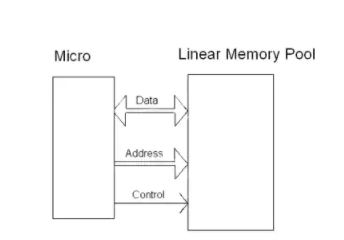

即使有许多 MCU 提供内存管理单元 (MMU)、索引和分页功能,可从任何微控制器直接访问的内存池也是由地址总线的二进制值直接寻址的线性块。NOR Flash 直接支持这种架构,是获取非易失性代码和数据的主力(图 1A)。

图 1A:标准 NOR 闪存与 RAM 一样,是线性寻址存储器位置的连续块。

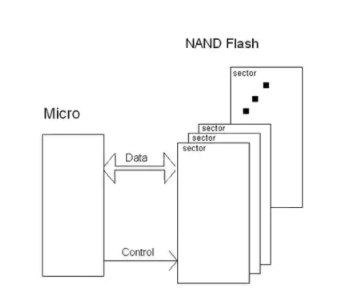

相比之下,NAND Flash 的组织方式类似于硬盘。连续的数据块聚集在一起形成以表格方式寻址的扇区,就像磁盘驱动器上的文件操作系统一样(图 1B)。

图 1B:NAND 闪存使用相同的数据总线来寻址内部的各个扇区。必须一次读入或写出整个扇区。

这不允许像 NOR 闪存那样使用 NAND 闪存来引导和运行代码。它不是随机存取存储器 (RAM)。必须读入、更新和回写整个扇区,而不是能够访问或修改单个内存位置。当代码执行跳跃时,这会进一步降低性能。每次在缓存块之外进行访问时,当微读入一个新的整个扇区时,一切都会停止。使用 NOR 闪存在单个高速微周期中可能发生的事情现在需要更多时间,因为必须首先访问整个块,然后将其缓存到 RAM 中。

然而,与 NOR 相比,NAND 闪存确实具有优势。首先,它具有更高的耐用性(与 NOR Flash 提供的 10K 或 100K 写入周期相比,通常为 100 万次写入)。话虽如此,但应该指出的是,现代 NOR Flash 一直在变得更好。第二个优点是即使需要读入和写回整个块,流操作总体上更快。设置完成后,每个位置都会以高速输入或输出,比每次访问 NOR 闪存所需的地址-解码-获取周期更快。因此,总体而言,NAND 闪存设备减少了移动大量数据的读写时间。

由于 SDRAM、DDR、DDR2 和 DDR3 等易失性 RAM 的密度和速度不断提高,大量低成本高速非易失性存储器已准备好用于缓存目的。这可以显着减少所需的传统 NOR 闪存数量,因为现在只需要一个基本的引导加载程序。

我们现在可以构建我们的系统,在我们的电路板上放置一个 NAND 闪存(或插入式 NAND 闪存卡)。然后,当微启动时,一个小型、低成本、基于片上 NOR 闪存的引导加载程序可以将代码和数据缓存到成本较低的连续线性可寻址 RAM 池中。在操作手头的任务时,可以在需要时将数据和动态加载的代码泵入和从 RAM 中抽出。

一些例子

一种选择是使用带有少量内部或外部 NOR 闪存的标准微控制器。通常,微控制器系列采用无 ROM 风格,所有访问都使用外部总线接口。片上闪存大小可以从非常小的块到非常大的块不等。如您所料,较小的块部件更便宜,无 ROM 部件更便宜。系统设计人员可以使用更小的块部件来降低成本,尤其是在可以使用深层外部 NAND 闪存池的情况下。

NXP的LPC2200系列采用这种方法,该系列采用 ROMless ( LPC2220FBD144,551 ) 风格,具有 128K 片上闪存,例如LPC2212FBD144/01,5和 256K 闪存,例如LPC2292FET144/01,5. 由于这些 16/32 位 75 MHz ARM® 7 处理器中不存在专用的 NAND 闪存接口硬件,恩智浦向工程师展示了如何使用两条通用 I/O 线和一个外部存储器接口 (EMI) 组。在这种情况下,片上闪存或小型外部 ROM 保存引导加载程序,代码控制从 NAND 闪存中提取和验证数据的过程。

我在这里使用斜体来强调验证的重要性,因为 NAND Flash 可能存在缺陷并卡在某些位置。另一方面,NOR Flash 通常更可靠且无缺陷。这意味着 NAND 闪存上的错误检测和纠正必须编码到关键代码和数据的访问和加载中。通常,只有 NAND 闪存的零页才能保证无缺陷。

恩智浦通过应用笔记 (AN10600) 说明了该应用的硬件实现和代码生成技术。¹

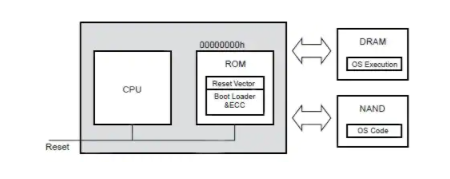

STMicroelectronics还提供通用应用笔记 (AN1935),可与ST 系列微控制器或几乎任何微控制器一起使用。本应用笔记展示了如何使用具有小页面(528 字节/264 字)或大页面(2,112 字节/1,056 字)单级单元 NAND 闪存设备的块零从外部 NAND 闪存启动(图2)。请注意此处如何直接支持 ECC 来验证数据的完整性。

图 2:一个小型内部 ROM 保存引导加载程序代码,它将运行时固件传输到外部 RAM(在本例中为 DRAM)。请注意在引导块代码中需要 ECC,因为 NAND 闪存可能存在缺陷。

添加片上功能

为实现 NAND 闪存的优势,微控制器供应商正在以多种方式在其 MCU 中集成直接 NAND 闪存支持。他们的目标是为嵌入式设计人员提供两全其美的体验。一种方法是使用片上小型引导加载程序,或者使用编程的 I/O,或者为 NAND 接口使用专用的片上硬件。

这是 Atmel 采用他们的AT91SAM7SE采用的方法,AT91SAM7SE是一个使用 ARM 7 架构的基于 ARM Thumb 的 32 位微控制器。是公司SAM7SE的成员系列。144 针 5 MHz 控制器具有 88 个 I/O 并容纳 32K x 8 片上闪存。这是一款中端处理器,具有强大的马力来处理许多通用任务,如果没有片上 NAND 闪存接口,它似乎对只有 32K 的代码空间感到饥饿。

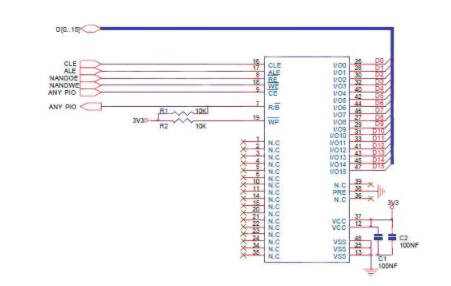

Atmel 部件上的外部总线接口支持高速、单周期 SDRAM,以及与 Smart Media、Compactflash 和启用 ECC 的 NAND 闪存设备的无缝连接。虽然有高达 512K 片上的版本可供选择,但出于成本控制目的,这个 32K 部件足以容纳引导加载程序并利用片上硬件接口用于 8 位和 16 位 NAND 闪存设备(使用其片上设备解码部分之一(图 3)。

图 3:Atmel 微控制器使用外部接口连接到 NAND 控制和数据线,无需任何胶水或外部逻辑。这里显示的是 16 位宽的接口,但这些部件也支持 8 位宽的接口。

Atmel 部件的在线仿真器 (ICE) 支持由基于 JTAG 的AT91SAM-ICE开发工具提供。Equinox Technologies FS2009USB (ARM)系统内编程工具也可用于测试、调试和制造环境。

第二种解决方案

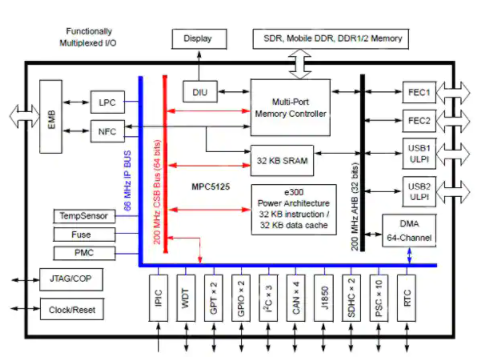

另一种方法是在微控制器上实现定序器或状态机,当微启动时,它会自动将 NAND 闪存的内容传输到 RAM。飞思卡尔半导体采用这种方法他们的 400 MHz 32 位MPC5125YVN400非常适合复杂的实时任务。这部分的有趣之处在于它是无 ROM 的,根本没有 Flash。相反,它允许通过其片上 NAND 闪存控制器从外部 NAND 闪存设备启动(图 4)。

图 4:当飞思卡尔 MPC5125 micro 的多端口内存控制器内部集成了专用 NAND Flash 接口逻辑时,NAND Flash 的内容可以在 micro 启动时自动传输到高速 RAM。

这些部件具有灵活、多功能的内存总线接口,不仅支持 DDR1、DDR2 和低功耗 DDR (LPDDR) 接口,而且在其 MMC、SD、和 SDIO 格式。内部控制器支持 8 位和 16 位宽的 NAND 闪存设备,并且可以从具有大于 2 KB 页面(或扇区)的设备启动。启动后,它支持 512 字节、2 KB、4 KB 和 8 KB 扇区大小,并具有内置的纠错和检测引擎。

请注意 USB OTG、以太网和 TFT 显示接口等高端外围设备。这些可能是代码和数据密集型的。更高密度的 NAND 闪存的一个完美应用是保存图形页面模板并使用片上 DMA 控制器将它们快速发送到显示器。这比必须使用代码时间来处理和渲染图形要快得多,并且可以在显示和图像质量方面产生真正的差异。–40° 至 +125°C 的扩展温度范围使该 MCU 也成为汽车应用的理想选择;尤其是其内置的多个 CAN 接口。

总之

几乎任何具有足够 I/O 的 micro 都可以与 NAND 闪存通信,并且通过他们的开发套件,大多数 micro 都证明了这一点,支持各种风格的 NAND 闪存卡,包括 USB、Smart Media、SD、CF、Micro SD、安全数字, 和别的。

虽然访问数据是一回事,但能够启动和运行有点棘手。如果您需要或希望使用 NAND 闪存,此处概述的三种方法是您嵌入式设计的良好起点。

最后,请记住,尽管 NAND 闪存具有高耐用性,但在正常使用中可能会出现缺陷,因此应将磨损均衡、错误检测/纠正、扇区锁定和其他系统完整性工具编码到您的应用程序中。

电子发烧友App

电子发烧友App

评论