本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB设计。

2014-07-24 11:11:21 4410

4410

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了一些要求。

2024-01-08 09:18:24 464

464

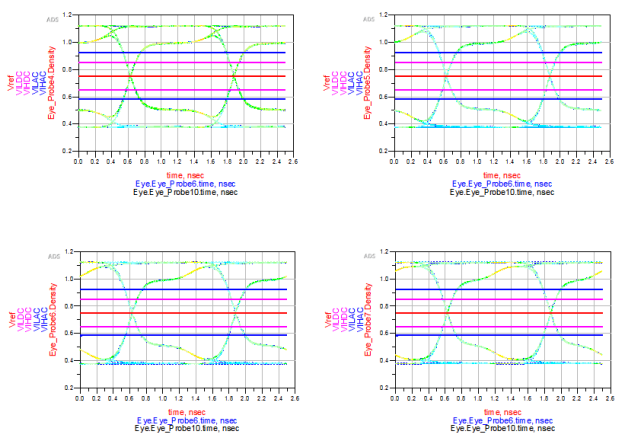

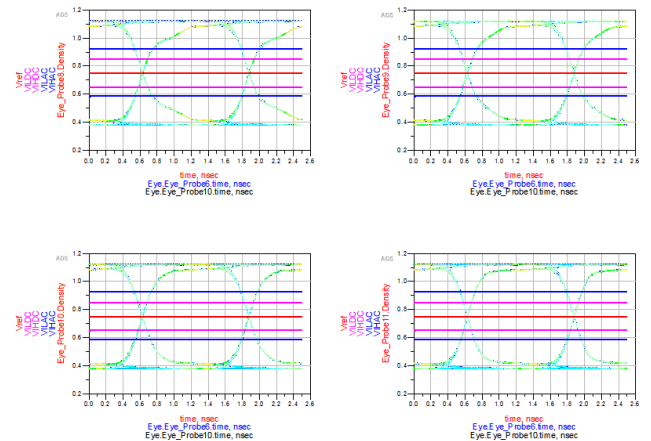

测试结果。由于信号完整性问题经常作为间歇性错误出现,因此重视同步切换控制、仿真和封装,保证设计符合信号完整性要求,在硅片制造前解决问题。对于IC应用,可利用仿真来选择合理的端接元件和优化元器件的布局,更

2013-12-05 17:44:44

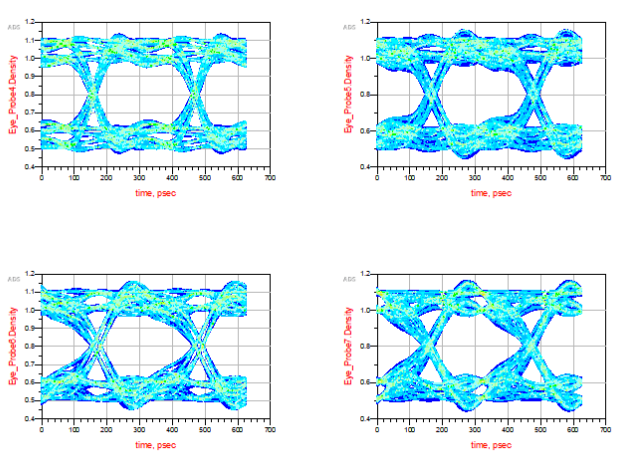

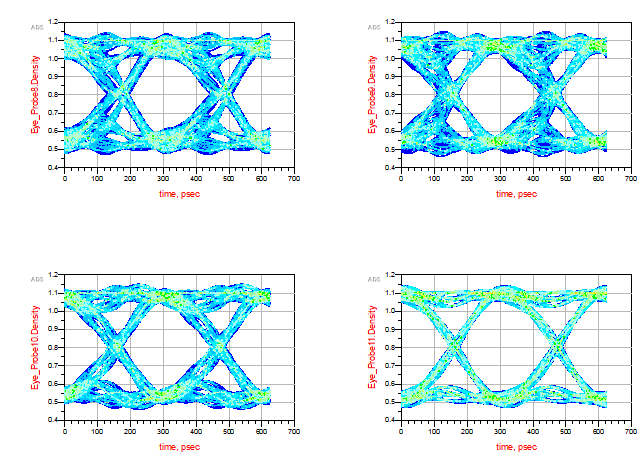

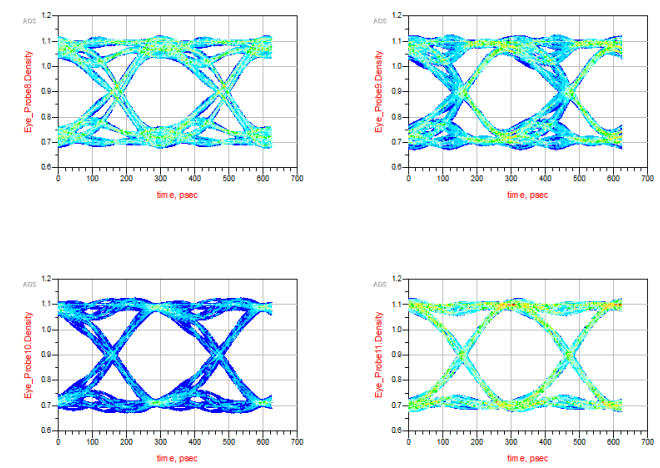

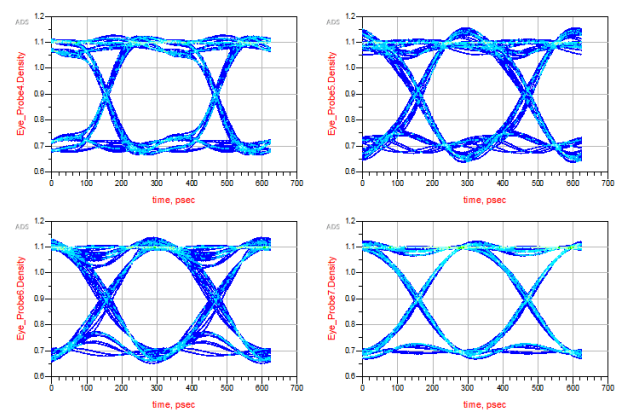

就可以简单的用眼图的形式来判断性能,而不需要像DDR3以前有建立保持时间的方法去判别,这样的话对于我们仿真来说会更有效率。4,根据一些功能的变化和调整减小了地址控制信号的引脚数,这个不用高速先生多说

2021-08-12 15:42:06

了极大的挑战。 本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性

2014-12-15 14:17:46

在CMD、ADD、CTRL信号为高电平时线路中就不会存在电流,可以降低功耗。DDR3和DDR4端接方式的对比如图4所示。图 4 DDR3和DDR4端接方式对比3 ACT_n信号为了避免由于容量增加

2019-11-12 12:40:17

做了电路设计有一段时间,发现信号完整性不仅需要工作经验,也需要很强的理论指导,坛友能提供一些信号完整性的视频资料么?非常感谢!

2019-02-14 14:43:52

在altium designer中想进行信号完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

而快速的初步分析,可确保有足够的电容器且它们具有正确的值。然后,运行分布式去耦分析可确保在电路板的不同位置满足PDN的所有阻抗需求。信号完整性仿真信号完整性仿真重点分析有关高速信号的3个主要问题:信号

2019-06-17 10:23:53

中国电子电器可靠性工程协会关于组织召开“信号完整性仿真应用”高级研修班的邀请函各有关单位:为了帮助广大从业人员详细了解信号完整性(SI)和电源完整性(PI)的基本概念、分析方法和应用实例,帮助电子

2009-11-25 10:13:20

高速设计中的信号完整性和电源完整性分析

2021-04-06 07:10:59

的完整性分析中,电路设计者需要考虑这些控制的实际实现方式,因为它们会影响到电路的负载特性以及波形性能。另外,还需考虑芯片上解耦电容的实现。 如图3所示的电路仿真图中包括了芯片、封装及PCB板信号线互联

2015-01-07 11:33:53

信号完整性与电源完整性的仿真分析与设计,不看肯定后悔

2021-05-12 06:40:35

其实电源完整性可做的事情有很多,今天就来了解了解吧。信号完整性与电源完整性分析信号完整性(SI)和电源完整性(PI)是两种不同但领域相关的分析,涉及数字电路正确操作。在信号完整性中,重点是确保传输

2021-11-15 07:37:08

先说一下,信号完整性为什么写电源完整性? SI 只是针对高速信号的部分,这样的理解没有问题。如果提高认知,将SI 以大类来看,SI&PI&EMI 三者的关系:所以,基础知识系列里还是

2021-11-15 06:32:45

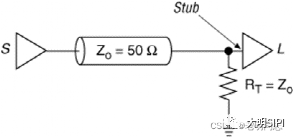

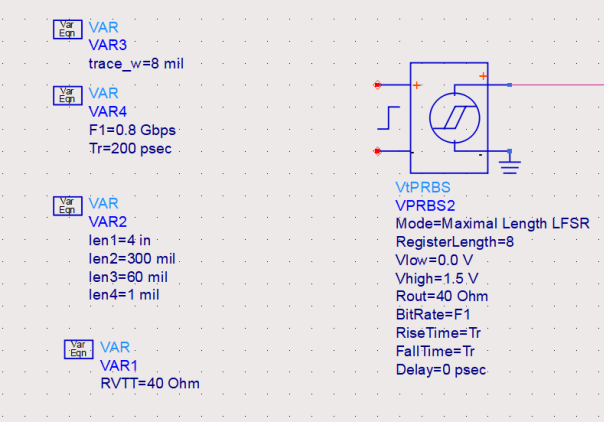

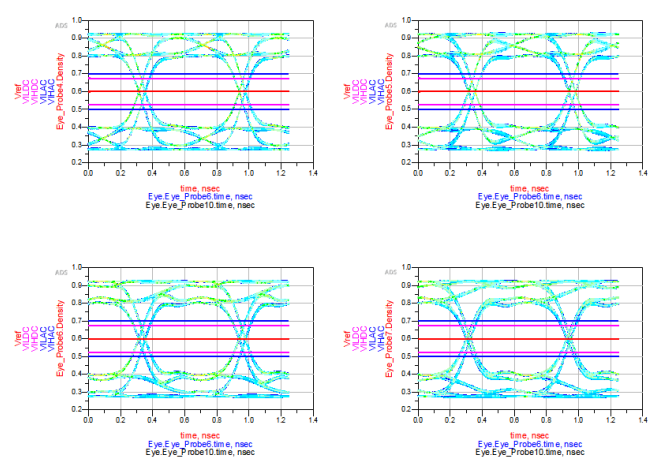

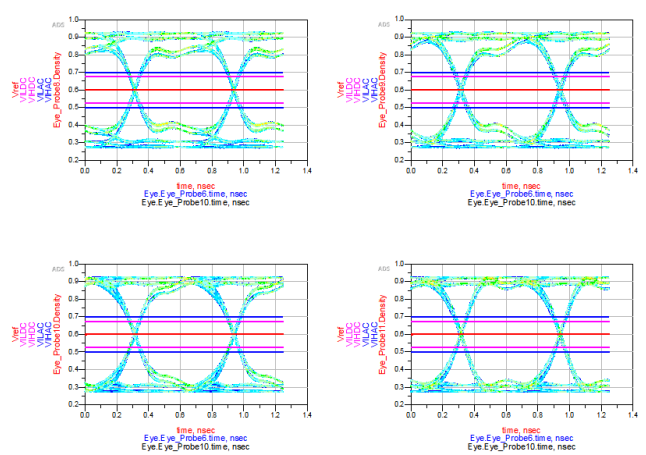

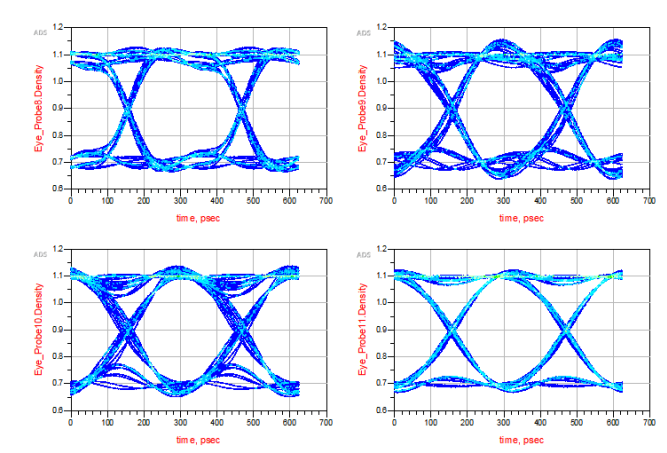

。 b、AC端接适合周期性信号,不适合非周期性信号。 c、会导致容性负载增加,RC延时增加。 d、相对于并联端接,有助于减小直流功耗。 图5、6 ADS仿真:RC端接 (4)戴维南端接:通过

2023-03-07 17:13:20

信号完整性资料

2015-09-18 17:26:36

很不错的一本信号完整性教材。其实EMC、EMI问题最终都是信号完整性问题。

2011-12-09 22:49:23

信号完整性分析与设计信号完整性设计背景???什什么是信号完整D??信信号完整性设计内è??典典型信号完整性问题与对2现在数字电路发展的趋ê??速速率越来越???芯芯片集成度越来越高£PC板板越来越

2009-09-12 10:20:03

信号完整性的定义信号完整性包含哪些内容

2021-03-04 06:09:35

信号完整性基础

2013-11-14 22:26:42

扰、轨道塌陷和电磁干扰。3、随着上升边的减小或者时钟频率的提高,各种信号完整性问题变得更严重,并且更加难以解决。4、由于晶体管越来越小,它们的上升边将越来越短,信号完整性也将成为越来越大的问题,这是

2015-12-12 10:30:56

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-25 06:51:11

熟悉PCB layout设计,学习DDR3\DDR4板的布局技巧,且熟悉至少一种仿真软件,不管是Hspice,还是Ansys designer/HFSS/SIwave/,或者是Hyperlynx

2019-09-03 17:54:59

输出到被分析的网络上。像电阻、电容、电感等被动元件,如果没有源的驱动,是无法给出仿真结果的。2、针对每个元件的信号完整性模型必须正确。3、在规则中必须设定电源网络和地网络,具体操作见本文。4、设定激励源

2015-12-28 22:25:04

Cadenc高速電路設計SI PI 信号完整性电源完整性仿真視頻教程下載鏈接地址:链接:http://pan.baidu.com/s/1pJiPpzl密码:3yjv

2015-07-30 21:44:10

。线宽为4mil。

我想问,在这种情况下,我是否可以通过控制这些信号走线的阻抗,再通过仿真这些信号,找到比较适合的阻抗值,从而同样达到减少或消除反射的噪音,满足信号完整性的要求。

2018-06-21 00:05:07

不同的标准外,还应该能够提供动态的OCT和可变摆率,以此来管理信号的上升和下降时间。结论DDR3在未来即将超越DDR2的使用,高端FPGA提供的低成本、高效能、高密度和良好的信号完整性方案必须满足JEDEC读写均衡要求。来源:EDN CHINA

2019-04-22 07:00:08

哪位同学有Hyperlynx的对PCB信号完整性仿真的相关教程分享一下???跪求!!!

2016-06-15 10:16:02

关于组织召开“信号完整性仿真应用”高级研修班的邀请函各有关单位:为了帮助广大从业人员详细了解信号完整性(SI)和电源完整性(PI)的基本概念、分析方法和应用实例,帮助电子行业

2009-11-18 17:28:42

`各位大侠好,小弟最近在走一个DDR3的布线,数据线等长做到了+/-5mil,可地址线和控制线由于空间不够,只能做到+/-200mil,这样布线有问题吗?设计的板子是4层板,中间两层是电源

2015-06-22 20:59:24

allegro_SI_信号完整性仿真

2014-05-16 10:43:51

hyperlynx Sigrity信号完整性仿真之高速理论视频教程Allegro 平板电脑DDR3 PCB设计视频教程链接:https://pan.baidu.com/s/1P1elXupWFQ8KNh-u7QhCDg 密码:fc5q

2018-08-25 15:54:28

完整性问题的4种实用技术途径,推导和仿真背后隐藏的解决方案,以及改进信号完整性的推荐设计准则等。本书还讨论了信号完整性中S参数的应用问题,并给出了电源分配网络的设计实例。本书强调直觉理解、实用工具和工程

2017-08-08 18:03:31

`编辑推荐《国外电子与通信教材系列:信号完整性与电源完整性分析(第二版)》强调直觉理解、实用工具和工程素养。作者以实践专家的视角指出造成信号完整性问题的根源,并特别给出了设计阶段前期的问题解决

2017-09-19 18:21:05

的详细介绍可以百度搜索“华秋DFM”官方链接内容简介: 《Cadence高速电路板设计与仿真:信号与电源完整性分析(第4版)》以Cadence Allegro SPB 16。3为基础,以具体的高速

2017-07-18 18:12:07

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关

2019-07-30 07:00:00

。过分的下冲能够引起假的时钟或数据错误。它们可以通过增加适当端接予以减少或消除。在Cadence的信号仿真软件中,将以上的信号完整性问题都放在反射参数中去度量。在接收和驱动器件的IBIS模型库中,我们

2019-11-19 18:55:31

噪声3.电磁干扰(EMI)常见的信号完整性的噪声问题,有振铃,反射,近端串扰,开关噪声,非单调性,地弹,电源反弹,衰减,容性负载。以上所有的噪声问题都与下面的4个噪声源有关:1:单一网络的信号完整性

2017-11-22 17:36:01

想了解什么是信号完整性的朋友,可以进来看看

2013-04-24 14:11:10

首先我们定义下什么是电源和信号完整性?信号完整性 信号完整性(SI)分析集中在发射机、参考时钟、信道和接收机在误码率(BER)方面的性能。电源完整性(PI)侧重于电源分配网络 (PDN) 提供恒定

2021-12-30 06:33:36

密不可分,它们也是DDR4区别于DDR3的主要技术突破。POD电平的全称是Pseudo Open-Drain 伪漏极开路,其与DDR3对比简单的示例电路如下图二所示。图二 POD示意电路从中可以看到

2022-12-16 17:01:46

何为信号完整性:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序

2021-12-30 08:15:58

各位大侠,请问大家用什么工具来做电源信号完整性仿真,cadence中有其SI 和 PI工具,为什么有些教程是在allegro中嵌入Ansoft 的siwave工具来仿真 这两者有很大区别吗?另外做完后仿真后,如果性能不佳 怎么整改?只能重新布线?

2016-08-12 13:42:28

资深硬件工程师的高速信号完整性仿真实例操作,用的是allegro,很有价值。[hide][/hide]

2020-07-13 23:18:49

或获取高速数字信号传输系统各个环节的信号完整性模型。 (2)在设计原理图过程中,利用信号完整性模型对关键网络进行信号完整性预分析,依据分析结果来选择合适的元器件参数和电路拓扑结构等。 (3)在

2018-09-03 11:18:54

中,采用Cadence软件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型来分析信号完整性,对阻抗匹配以及拓扑结构进行优化设计,以保证系统正常工作。本文只对信号反射和串扰进行详细

2015-01-07 11:30:40

PCB板设计之前,首先建立高速数字信号传输的信号完整性模型。 根据SI模型对信号完整性问题进行一系列的预分析,根据仿真计算的结果选择合适的元器件类型、参数和电路拓扑结构,作为电路设计的依据。 在

2018-08-29 16:28:48

PCB板设计之前,首先建立高速数字信号传输的信号完整性模型。 根据SI模型对信号完整性问题进行一系列的预分析,根据仿真计算的结果选择合适的元器件类型、参数和电路拓扑结构,作为电路设计的依据。 在

2008-06-14 09:14:27

。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配技术对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM

2018-08-02 09:34:58

摘 要:从信号完整性分析设计规则、完整性分析仿真器、波形分析器等三个方面说明了如何利用Protel 99的信号完整性分析功能进行印刷电路板的设计。 关键词:信号完整性;电磁干扰;波形

2018-08-27 16:13:55

如何保证脉冲信号传输的完整性,减少信号在传输过程中产生的反射和失真,已成为当前高速电路设计中不可忽视的问题。

2021-04-07 06:53:25

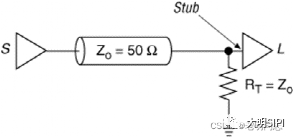

布线必须考虑的关键因素。因为时序要求严格,这种节点通常必须采用端接器件才能达到最佳SI质量。要预先确定这些节点,同时将调节元器件放置和布线所需要的时间加以计划,以便调整信号完整性设计的指针。5、技术

2018-07-31 17:12:43

何为信号完整性?信号完整性包括哪些?干扰信号完整性的因素有哪些?如何去解决?

2021-05-06 07:00:23

如何进行兼顾电源影响的DDR4信号完整性仿真

2021-01-08 07:53:31

信号完整性设计方法,是从全局上把握整个设计,所做的远远不只有仿真。《信号完整性设计中的5类典型问题》一文中,对几类问题做过简单的阐述,感兴趣的可参考阅读。在系统化信号完整性设计方法的框架下,需要仿真

2017-06-23 11:52:11

信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的工具和资源不少,本文主要探索,究竟还有什么办法可以确保信号完整性?

2019-08-02 07:52:35

信号完整性、提升产品质量的必由之路。

八、解决问题能力

对于信号完整性工程师而言, 仿真和测试只是手段 ,真正的核心是分析和解决问题的能力。现代工程师能轻松获取波形曲线,但理解其背后的意义和问题才是

2024-03-05 17:16:39

模拟DDR3的地址信号与时钟信号

2021-03-02 08:12:10

信号完整性(SI)问题解决得越早,设计的效率就越高,从而可避免在电路板设计完成之后才增加端接器件。SI设计规划的工具和资源不少,本文探索信号完整性的核心议题以及解决SI问题的几种方法,在此忽略

2015-01-07 11:44:45

信号完整性与电源完整性分析信号完整性(SI)和电源完整性(PI)是两种不同但领域相关的分析,涉及数字电路正确操作。在信号完整性中,重点是确保传输的1在接收器中看起来就像 1(对0同样如此)。在电源

2021-11-15 06:31:24

有网友质疑大家普遍对信号完整性很重视,但对于电源完整性的重视好像不够,主要是因为,对于低频应用,开关电源的设计更多靠的是经验,或者功能级仿真来辅助即可,电源完整性分析好像帮不上大忙,而对于50M

2019-09-20 14:44:25

针对DDR2-800和DDR3的PCB信号完整性设计

2012-12-29 19:12:39

高速信号的电源完整性分析在电路设计中,设计好一个高质量的高速PCB板,应该从信号完整性(SI——Signal Integrity)和电源完整性 (PI——Power Integrity )两个方面来

2012-08-02 22:18:58

高速电路信号完整性分析与设计—信号完整性仿真仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上升沿从20%~80%VCC的时间,一般是ns级或

2009-09-12 10:31:31

高速电路信号完整性分析与设计—信号完整性仿真:仿真信号仿真中有两类信号可称之为高速信号:高频率的信号(>=50M)上升时间tr很短的信号:信号上

2009-10-06 11:19:50 0

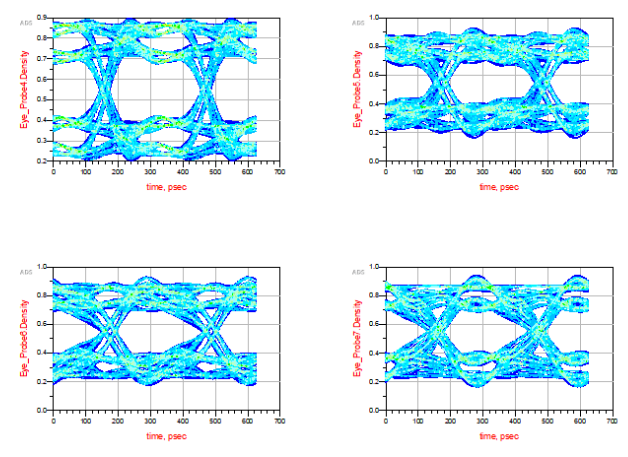

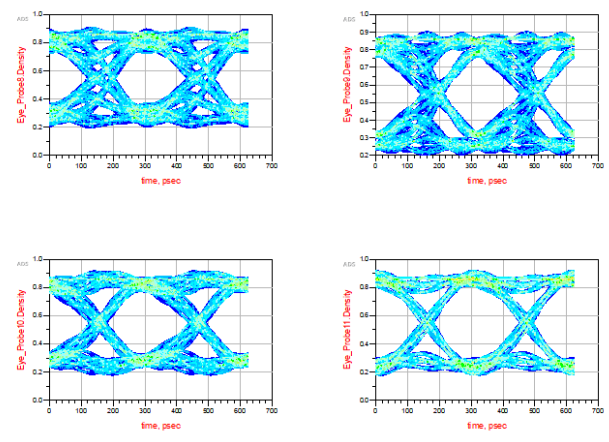

0 针对高速数字电路印刷电路板的板级信号完整性, 分析了IBIS 模型在板级信号完整性分析中的作用。利用ADS 仿真软件, 采用电磁仿真建模和电路瞬态仿真测试了某个实际电路版

2010-08-23 17:18:04 37

37 本文章主要涉及到对 DDR2 和DDR3 在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB 层数,特别是4 层板

2011-07-12 17:31:10 0

0 介绍引起信号完整性问题的主要因素, 利用。进行信号仿真的步骤, 给出了的信号仿真的时比结果, 并以该信号作为分析对象, 详细分析了为判断信号质童的优劣, 对仿真波形进行定量分析

2011-11-30 11:09:46 0

0 为了使设计人员对信号完整性与电源完整性有个全面的了解,文中对信号完整性与电源完整性的问题进行了仿真分析与设计,也从系统的角度对其进行了探讨。

2011-11-30 11:12:24 0

0 本专题详细介绍了信号完整性各部分知识,包括信号完整性的基础概述,信号完整性设计分析及仿真知识,还有具体应用中的一些小经验分享等等,充分翔实的向大家描述了信号完整性。

2011-11-30 11:44:35

针对DDR2-800和DDR3的PCB信号完整性设计

2016-02-23 11:37:23 0

0 针对DDR2-800和DDR3的PCB信号完整性设计,要认证看

2016-12-16 21:23:41 0

0 10129@52RD_信号完整性与电源完整性的仿真分析与设计

2016-12-14 21:27:39 0

0 引起的。主要的信号完整性问题包括反射、振铃、地弹、串扰等。 源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面

2017-11-16 13:24:51 0

0 本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

2018-02-06 18:47:57 2638

2638

借助功能强大的Cadence公司SPEECTRAQuest仿真软件,利用IBIS模型,对高速信号进行信号完整性仿真分析是一种高效可行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而达到提高设计质量,缩短设计周期的目的。

2019-05-20 15:25:37 1098

1098

技术分享:信号完整性仿真 - 入门

2019-07-02 12:03:07 3530

3530

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-20 14:22:53 1011

1011

本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

2021-01-23 08:45:50 28

28 本文章主要涉及到对DDR2和DDR3在PCB设计时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。 文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中

2021-03-25 14:26:01 3864

3864

Hyperlynx信号完整性仿真性分析。

2021-04-07 13:59:10 121

121 DDR4电路板设计与信号完整性验证挑战

2021-09-29 17:50:07 10

10 信号完整性与电源完整性的仿真(5V40A开关电源技术参数)-信号完整性与电源完整性的仿真分析与设计!!!

2021-09-29 12:11:21 89

89 高速电路信号完整性分析与设计—端接与拓扑

2022-02-10 16:38:28 0

0 高速电路信号完整性分析与设计—信号完整性仿真

2022-02-10 17:29:52 0

0 终端端接对于信号完整性有着重要的意义,它和源端匹配一样都是解决信号完整性问题的重要手段。

2023-06-15 11:08:03 892

892

为什么电路端接电阻能改善信号完整性? 在电路设计中,信号完整性是一个极其重要的概念。信号完整性是指信号在传输、转换和处理过程中所遭受的失真、干扰或损失。这些信号可能是模拟信号或数字信号,它们的完整性

2023-10-24 10:04:52 372

372 PCB级的信号完整性仿真

2022-12-30 09:20:36 5

5

正在加载...

电子发烧友App

电子发烧友App

评论