我们将介绍:

DDR x4 x8 x16 chip width

DDR bank & rank

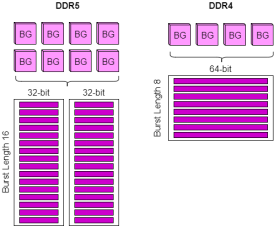

DDR bankgroup

DDR Prefetch

DDR Page Size

DDR Row Buffer

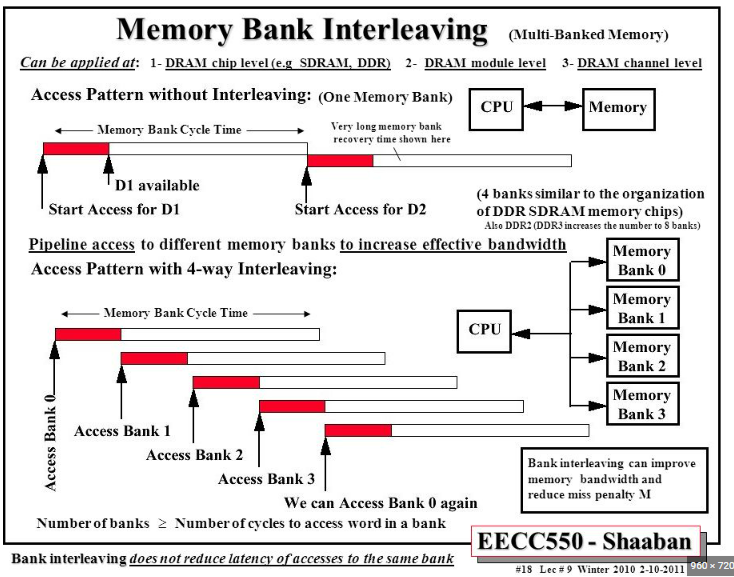

DDR Bank Interleaving

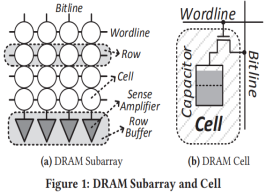

DDR Cell & Command Sequence

DDR x4 x8 x16

x4 x8 x16 指的上图黑色的chip输出的位宽,正常的DDR bus width 需要64bit,所以

| chip width | x4 | x8 | x16 |

| 黑色chip数量 | 16 | 8 | 4 |

上图是最常见的x8,也就有8个黑色的chip颗粒。x16的性能和x8的性能相比怎么样呢?

更差,因为x16的bankgroup更少。

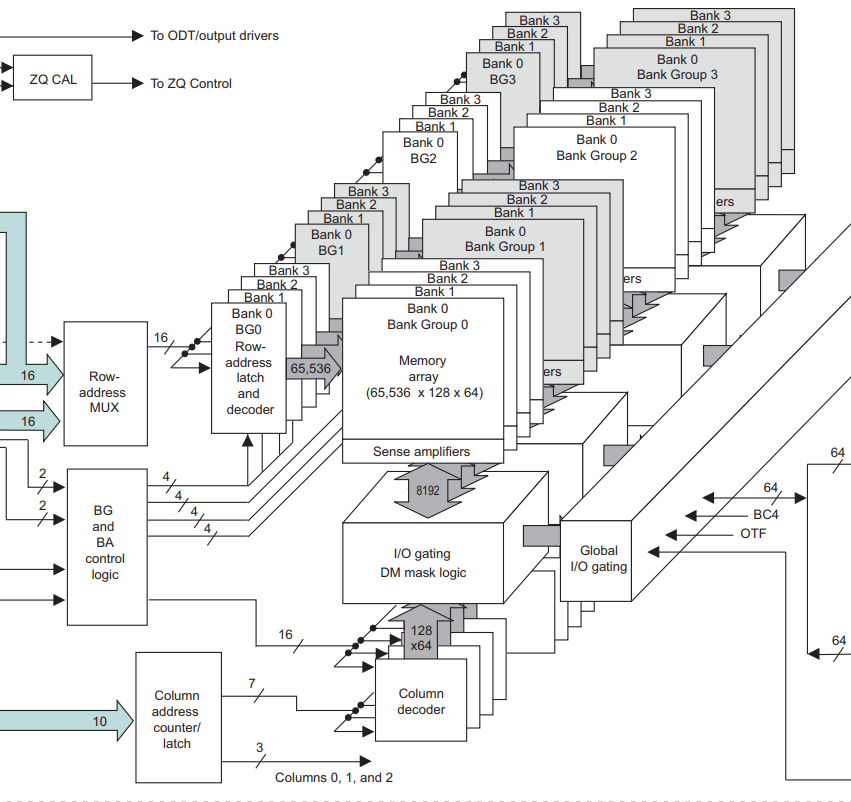

DDR4 x8 4 bankgroup

图自 https://www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr4/8gb_ddr4_sdram.pdf

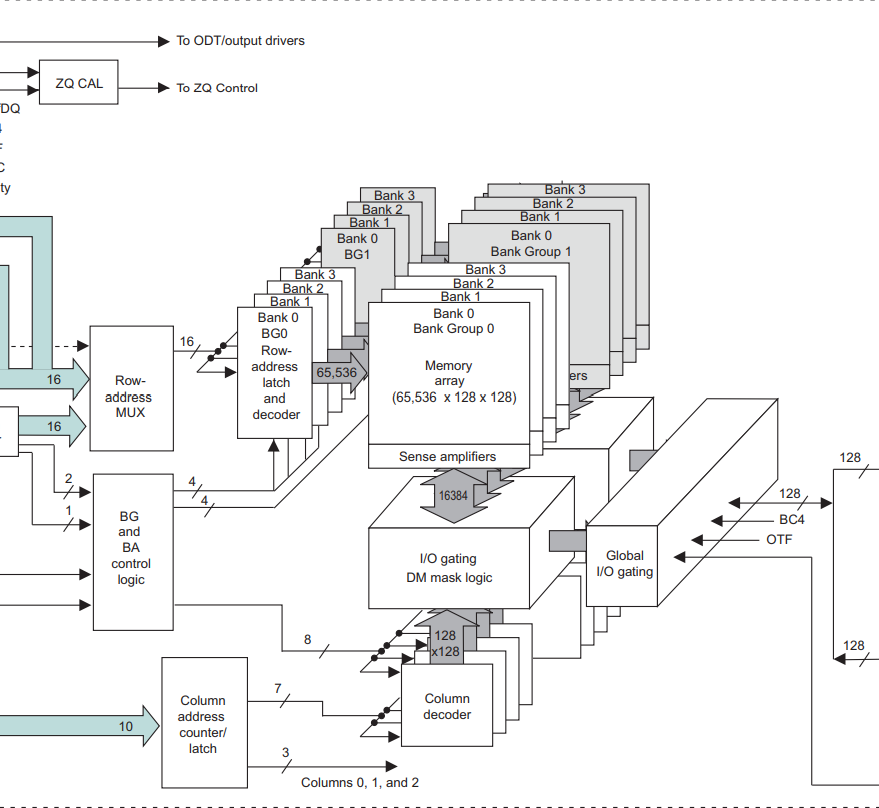

DDR4 x16 2 bankgroup

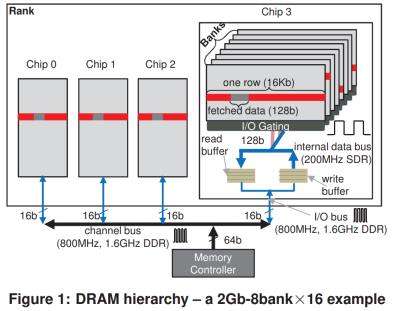

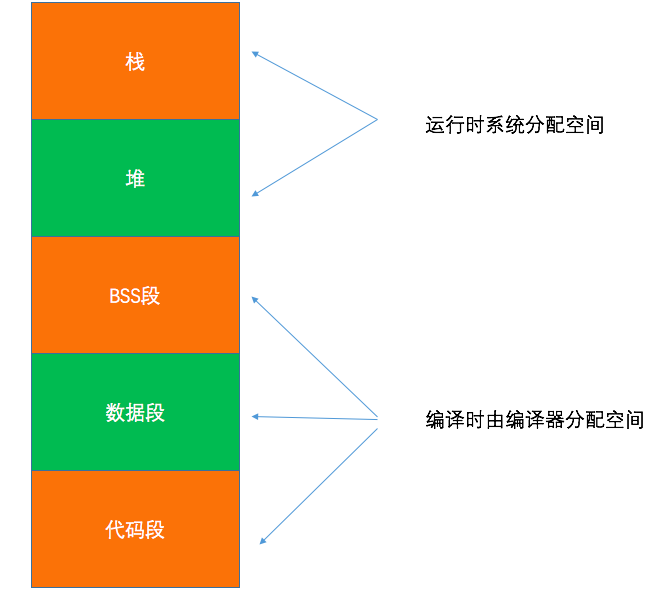

DDR bank rank

DDR 正面就是一个rank,背面如果也有颗粒,那就又是一个rank。实物图中的8个颗粒组成了一个rank。

其中的一个颗粒的架构图如上面两个图所示,内部分成bankgroup,bankgroup内又分成bank。

我们每次发送的读写命令都是操作的各个颗粒里面同一个位置的bank。比如chip0的bank3,chip1的bank3,chip2的bank3…

DDR bankgroup

DDR的bankgroup可以理解为是将颗粒分成了group进行操作,也可以抽象成是把黑色颗粒chip内又独立成了各个单独的小颗粒,即各个bankgroup。

增加bank的数量就意味着可以增加各个bank之间pipeline操作,因此bank数量越多,吞吐率越大。

为什么有bankgroup?

解决这个问题我们先要理解prefetch。

DDR每更新一代,外面管脚pin的传输速度都翻倍。但是其实DDR内部真正memory的速度和latency是没有变化的,DDR通过预取完成这个假象。

DDR3 x8的预取的本质:

x8即每个颗粒输出8bit,DDR内部慢速的memory通过每次输出64bit,在外部快速的pin管脚上连续输出,即可以得到8倍频。

如果xW W为每个颗粒的位宽,DDR memory和外部管脚的速度相差为M,那么每个颗粒预取WxN bit。

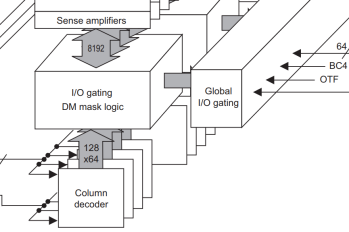

截自 1 Gig x 8的图,右侧的64即为预取的64bit。

| DDR N | DDR | DDR2 | DDR3 | DDR4 | DDR5 |

| Prefetch | 2 | 4 | 8 | 8 | 16 |

8倍频的DDR3的Prefetch 8,bus width 64bit,正好对应64B。

16倍频的DDR4如果继续prefetch16,那么就会对应128B,与cacheline的64byte对应不上,因此DDR4采用了上文说的bankgroup,在不同的bankgroup间切换输出,来避免连续的输出128Byte。

32倍频的DDR5 prefetch16,难道就不会有输出128B的问题了吗?

确实没有这个问题。如果想要继续使用bankgroup的方法,在多个bankgroup之间切换,也很难做到。因此DDR5的64bit bus切成了两半,32bit x 16 仍然是64B。

实际上64bit额外还有ECC bit,不过我们不必理解。

DDR Page Size

DDR Page Size实际上是每次激活DDR时,输出到row buffer中的数据大小,具体的计算方式是2^column_width * chip_width / 8 Byte.

如果DDR的column address 10 bit, 那么chip_width是4的 page size对应512B,chip_width是8的 page size对应1KB。

DDR Row Buffer

每次activation激活命令发送到DDR时,将DDR的一整行输出到row buffer中,如上图所示。row buffer中的一小部分当前请求的被预取的数据被输出到外部。 如果我们下一次需要读取另一行,那么就需要先写回这一行,然后precharge bit line,再去打开新的一行,这样代价还是挺大的。

所以比较理想的情况是继续读取当前这一行的下一个部分数据,这样不需要写回,可以持续的从row buffer中读取。

图自https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6853217

上图中,row size即page size为2KB,本次预取chip3中的128b,如果下一次能继续读取后面的128b,那么只需要发送一个command命令就可以了。

我们借着这张图回顾一下上面介绍过的内容:

每个chip位宽16bit,需要4个chip组成64bit

外部时钟800Mhz,因为DDR double rate传输,所以实际上是1600Mhz,内部时钟200Mhz,时钟相差8倍。所以我们每次需要预取16x8=128bit.

注意看上图中的每个chip都有一个红色的横条,也就是每次读取的时候都是不同chip的同一个位置的bank被读取。

那么为什么Chip3中的不同的bank的红色横条的位置不一样?

DDR Bank Interleaving

DDR 同一个bank内不同的row之间切换需要上文说的 restore写回和precharge。

但是不同bank之间,共享命令地址数据总线,但是内部的memory是独立的,所以我们可以访问bank0的第1行之后,访问bank1的第7行,再访问bank3的第2行,bank之间的pipeline输出,最大程度的利用数据总线。

如下图所示,

DDR Cell & Command Sequence

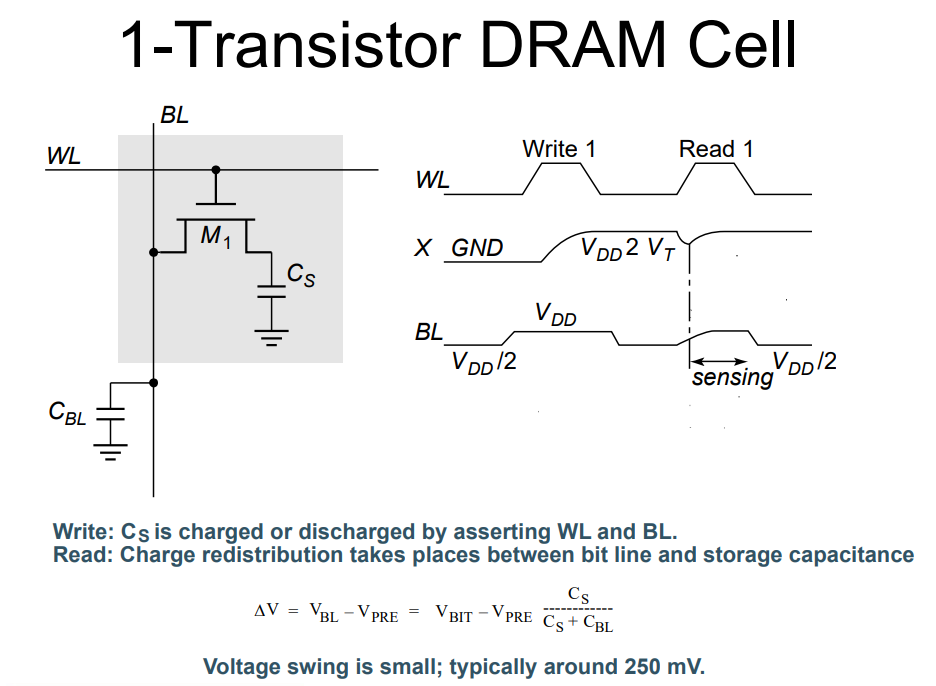

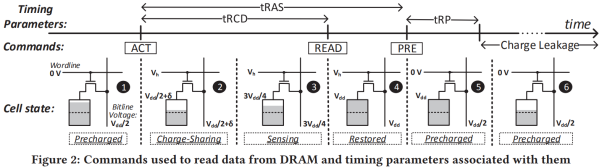

上文说的DDR需要写回,是因为DDR是电容组成,存在泄露,除了写回,也需要定期刷新。上图中的Cs存储真正的memory。为了简单,我们将电压理解成0/1 V.

图自https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=7446096

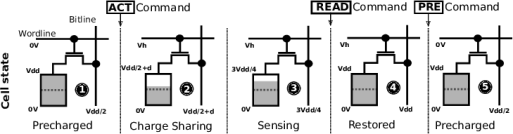

上一次操作结束后,会对DRAM precharge,将Cbl charge到0.5v的电位。

我们如果发起读命令,activation操作,会激活一行,即拉高WL线,这时Cs的电位0/1 V和Cbl0.5v的电压会发生charge sharing

Sensing阶段会将电压差经过sense amplifier 存储这一行的数据到row buffer中

Read 命令会从row buffer中,预取对应长度的数据,输出到外侧

在sense amplifier 完成工作后,会将Vdd的电压充至1V,即为restore,此时被破坏了的数据得到了恢复

断开wordline,充电bitline至0.5v,即为precharge操作。

简单的说

Activate 激活对应行 word line,数据输出到row buffer

Read 列命令对应从row buffer中读取数据

Precharge命令恢复bitline至一半电压

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论